TPS53318, TPS53319 ZHCS979F - JUNE 2012 - REVISED OCTOBER 2020

# 具有 Eco-Mode 控制模式的 TPS5331x 8A 或 14A 高效 同步降压转换器

## 1 特性

- 转换输入电压范围:1.5V 至 22V

- VDD 输入电压范围: 4.5V 至 25V

- 在电压为 12V 至 1.5V 且电流为 14A 时效率达 91%

- 输出电压范围: 0.6V 至 5.5V

- 5V LDO 输出

- 支持单轨输入

- 集成功率 MOSFET,持续输出电流达 8A (TPS53318)或 14A (TPS53319)

- 自动跳跃 Eco-mode<sup>™</sup> 可提高轻负载效率

- 关断电流 < 110 µ A

- D-CAP™模式可提供快速瞬态响应

- 可借助外部电阻器在 250kHz 至 1MHz 之间选择开 关频率

- 可选自动跳跃或仅 PWM 工作模式

- 内置 1% 0.6V 基准电压

- 0.7ms、1.4ms、2.8ms 和 5.6ms 可选内部电压伺 服器软启动

- 集成升压开关

- 预充电启动功能

- 具有热补偿的可调过流限制

- 过压、欠压、UVLO 和过热保护

- 支持所有陶瓷输出电容器

- 漏极开路电源正常状态指示

- 整合 NexFET™ 电源块技术

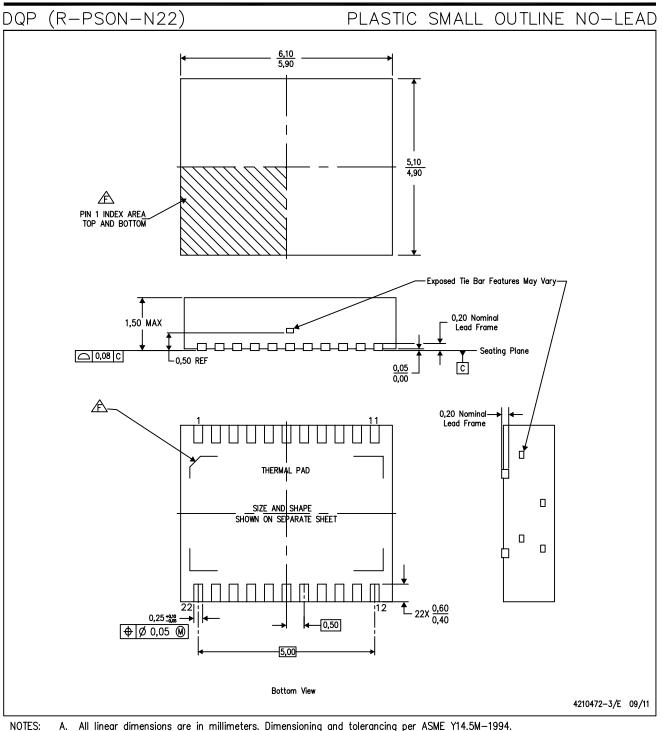

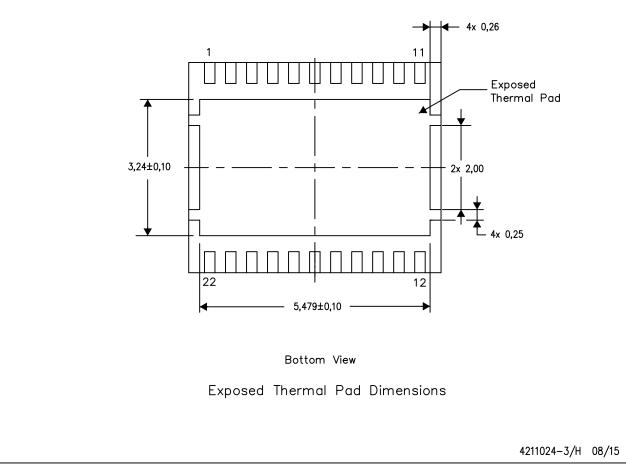

- 采用 PowerPAD<sup>™</sup> 的 22 引脚 QFN (DQP) 封装

## 2 应用

- 服务器和存储

- 工作站和台式机

- 电信基础设施

## 3 说明

TPS53318 和 TPS53319 器件是集成 MOSFET、具有 D-CAP 模式的 8A 或 14A 同步开关。它们被设计用于 易于使用、低外部组件数量、和空间受限的电源系统。

这些器件特有精准的 1%,0.6V 基准,和集成的升压 开关。具有竞争力的特性示例包括:1.5V 至 22V 宽转 换输入电压范围、超低的外部组件数、针对超快瞬变的 D-CAP™ 模式控制、自动跳跃模式运行、内部软启动 控制、可选频率并且无需补偿。

转换输入电压范围为 1.5V 至 22V,电源电压范围为 4.5V 至 25V,输出电压范围为 0.6V 至 5.5V。

这些器件采用 5mm x 6mm 22 引脚 QFN 封装,额定运行温度范围为 - 40°C 至 85°C。

| 器件信息 <sup>(1)</sup> |    |  |

|---------------------|----|--|

| 封准                  | 封准 |  |

| 器件型号     | 封装              | 封装尺寸(标称值)       |  |

|----------|-----------------|-----------------|--|

| TPS53318 | LSON-CLIP (22)  | 6.00mm x 5.00mm |  |

| TPS53319 | 20011-021F (22) |                 |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的封装选项附录部分。

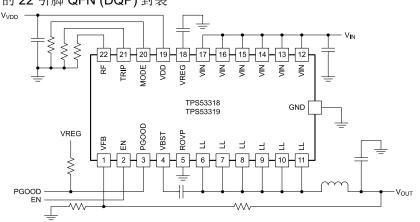

简化应用

## **Table of Contents**

| 1 | 特性                                    | 1 |

|---|---------------------------------------|---|

|   | 应用                                    |   |

| 3 | 说明                                    | 1 |

|   | Revision History                      |   |

| 5 | Device Comparison Table               | 3 |

|   | Pin Configuration and Functions       |   |

| 7 | Specifications                        | 6 |

|   | 7.1 Absolute Maximum Ratings          |   |

|   | 7.2 ESD Ratings                       | 6 |

|   | 7.3 Recommended Operating Conditions  | 6 |

|   | 7.4 Thermal Information               | 7 |

|   | 7.5 Electrical Characteristics        |   |

|   | 7.6 Typical Characteristics1          | 0 |

|   | 7.7 TPS53319 Typical Characteristics1 | 4 |

|   | 7.8 TPS53318 Typical Characteristics1 |   |

| 8 | Detailed Description1                 |   |

|   | 8.1 Overview1                         |   |

|   | 8.2 Functional Block Diagram1         | 6 |

|   |                                       |   |

| 8.3 Feature Description                               | 17  |

|-------------------------------------------------------|-----|

| 8.4 Device Functional Modes                           |     |

| 9 Application and Implementation                      |     |

| 9.1 Application Information                           |     |

| 9.2 Typical Applications                              |     |

| 10 Power Supply Recommendations                       |     |

| 11 Layout                                             | .31 |

| 11.1 Layout Guidelines                                | 31  |

| 11.2 Layout Example                                   | 32  |

| 12 Device and Documentation Support                   | .33 |

| 12.1 Device Support                                   | 33  |

| 12.2 Receiving Notification of Documentation Updates. | .33 |

| 12.3 Support Resources                                | 33  |

| 12.4 Trademarks                                       | .33 |

| 12.5 Electrostatic Discharge Caution                  | .33 |

| 12.6 Glossary                                         |     |

| 13 Mechanical, Packaging, and Orderable               |     |

| Information                                           | .33 |

|                                                       |     |

## **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision E (November 2016) to Revision F (October 2020) | Page |

|---|---------------------------------------------------------------------|------|

| • | 更新了整个文档的表、图和交叉参考的编号格式。                                              | 1    |

| • | Added ROVP pin description                                          | 4    |

|   | Added additional ROVP pin information.                              |      |

| С | hanges from Revision D (February 2015) to Revision E (November 2016) | Page |

|---|----------------------------------------------------------------------|------|

| • | Changed Pin 19 From: ground To: V <sub>IN</sub> 12 V in 🛽 9-1        | 24   |

| <ul> <li>Added recommendation for ROVP connection when ROVP function is not needed in the second second</li></ul> | n Pin Functions table 4 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| <ul> <li>Corrected typographical error. Changed "when the VDD voltage rises above 1 V" to<br/>rises above 2 V" in #8.3.1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                       |

| • Added ROVP Pin Design Note in #8.3.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         |

| - |                                                                                  |      |

|---|----------------------------------------------------------------------------------|------|

| • | 添加了引脚配置和功能部分、ESD 等级表、特性说明部分、器件功能模式、应用和实施部分、<br>议部分、布局部分、器件和文档支持部分以及机械、封装和可订购信息部分 |      |

| • | Added clarity to <i>节 8.3.7</i>                                                  |      |

| c | hanges from Revision A (JUNE 2012) to Revision B (MAY 2013)                      | Page |

####

## Changes from Revision \* (JUNE 2012) to Revision A (AUGUST 2012)

Page

## **5** Device Comparison Table

| ORDER NUMBER <sup>(1)</sup> | OUTPUT CURRENT (A) |

|-----------------------------|--------------------|

| TPS53318DQP                 | 8                  |

| TPS53319DQP                 | 14                 |

(1) For detailed ordering information see the *Package Option Addendum* section at the end of this data sheet.

## **6** Pin Configuration and Functions

## 图 6-1. 22 Pins DQP (LSON-CLIP) Package (Top View)

#### 表 6-1. Pin Functions

| PIN   |      | I/O/P <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                      |  |  |

|-------|------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME  | NO.  | I/O/P(')             | DESCRIPTION                                                                                                                                                                                                                                                                      |  |  |

| EN    | 2    | I                    | Enable pin. Typical turnon threshold voltage is 1.3 V. Typical turnoff threshold voltage is 1.0 V.                                                                                                                                                                               |  |  |

| GND   |      | G                    | Ground and thermal pad of the device. Use proper number of vias to connect to ground plane.                                                                                                                                                                                      |  |  |

|       | 6    |                      |                                                                                                                                                                                                                                                                                  |  |  |

|       | 7    |                      |                                                                                                                                                                                                                                                                                  |  |  |

|       | 8    | В                    | Output of converted power. Connect this pin to the output inductor.                                                                                                                                                                                                              |  |  |

| LL    | 9    |                      |                                                                                                                                                                                                                                                                                  |  |  |

|       | 10   |                      |                                                                                                                                                                                                                                                                                  |  |  |

|       | 11   |                      |                                                                                                                                                                                                                                                                                  |  |  |

| MODE  | 20   | I                    | Soft start and mode selection. Connect a resistor to select soft-start time using $\frac{1}{8}$ 8-3. The soft-start time is detected and stored into internal register during start-up.                                                                                          |  |  |

| PGOOD | 3    | 0                    | Open drain power-good flag. Provides 1-ms start-up delay after VFB falls in specified limits. When VFB goes out of the specified limits, PGOOD goes low after a 2-µs delay.                                                                                                      |  |  |

| ROVP  | 5    | I                    | Redundant overvoltage protection (OVP) input. Use a resistor divider to connect this pin to $V_{OUT}$ . Internally pulled down to GND with a 1.5-M $\Omega$ resistor. If redundant OVP is not needed, connect this pin to GND. Do not leave ROVP pin floating (see $\# 8.3.9$ ). |  |  |

| RF    | 22   | I                    | Switching frequency selection. Connect a resistor to GND or VREG to select switching frequency using 表 8-1. The switching frequency is detected and stored during the start-up.                                                                                                  |  |  |

| TRIP  | 21 I |                      | OCL detection threshold setting pin. $I_{TRIP} = 10 \ \mu A$ at room temperature. 3000 ppm/°C current is sourced and set the OCL trip voltage as follows.                                                                                                                        |  |  |

|       |      |                      | $V_{OCL} = V_{TRIP}/32 \qquad (V_{TRIP} \le 2.4 \text{ V}, V_{OCL} \le 75 \text{ mV})$                                                                                                                                                                                           |  |  |

| VBST  | 4    | Р                    | Supply input for high-side FET gate driver (boost terminal). Connect capacitor from this pin to LL node.<br>Internally connected to VREG via bootstrap MOSFET switch.                                                                                                            |  |  |

| VDD   | 19   | Р                    | Controller power supply input. VDD input voltage range is from 4.5 V to 25 V.                                                                                                                                                                                                    |  |  |

| VFB   | 1    | I                    | Output feedback input. Connect this pin to V <sub>OUT</sub> through a resistor divider.                                                                                                                                                                                          |  |  |

|       | 12   |                      |                                                                                                                                                                                                                                                                                  |  |  |

|       | 13   |                      |                                                                                                                                                                                                                                                                                  |  |  |

| VIN   | 14   | P                    | Conversion power input. The conversion input voltage range is from 1.5 V to 22 V.                                                                                                                                                                                                |  |  |

|       | 15   |                      |                                                                                                                                                                                                                                                                                  |  |  |

|       | 16   |                      |                                                                                                                                                                                                                                                                                  |  |  |

|       | 17   |                      |                                                                                                                                                                                                                                                                                  |  |  |

| VREG  | 18   | Р                    | 5-V low dropout (LDO) output. Supplies the internal analog circuitry and driver circuitry.                                                                                                                                                                                       |  |  |

## 表 6-1. Pin Functions (continued)

| PIN<br>NAME NO. |  | I/O/P <sup>(1)</sup> | DESCRIPTION                                                                                   |  |

|-----------------|--|----------------------|-----------------------------------------------------------------------------------------------|--|

| Thermal Pad     |  | G                    | Ground and thermal pad of the device. Use a proper number of vias to connect to ground plane. |  |

(1) I = Input, O = Output, B = Bidirectional, P = Supply, G = Ground

## 7 Specifications

## 7.1 Absolute Maximum Ratings

|                                                              |                                      |                        | VAL   | VALUE <sup>(1)</sup> |      |

|--------------------------------------------------------------|--------------------------------------|------------------------|-------|----------------------|------|

|                                                              |                                      |                        | MIN   | MAX                  | UNIT |

|                                                              | VIN (main supply)                    |                        | - 0.3 | 30                   |      |

|                                                              | VDD                                  | VDD                    |       | 28                   |      |

| Input voltage range                                          | VBST                                 |                        | - 0.3 | 32                   | V    |

|                                                              | VBST (wit                            | h respect to LL)       | - 0.3 | 7                    |      |

|                                                              | EN, MOD                              | E, TRIP, RF, ROVP, VFB | - 0.3 | 7                    |      |

|                                                              | LL                                   | DC                     | - 2   | 30                   | -    |

|                                                              |                                      | Pulse < 20ns, E = 5 μJ | - 7   | 32                   |      |

| Output voltage range                                         | PGOOD,                               | PGOOD, VREG            |       | 7                    | v    |

|                                                              | GND                                  |                        | - 0.3 | 0.3                  |      |

| Source/Sink current                                          | VBST                                 |                        | 50    |                      | mA   |

| Operating free-air temperatur                                | e, T <sub>A</sub>                    |                        | - 40  | 85                   |      |

| Junction temperature range, <sup>-</sup>                     | TJ                                   |                        | - 40  | 150                  | °C   |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |                                      |                        |       | 300                  | C    |

| Storage temperature, T <sub>stg</sub>                        | torage temperature, T <sub>stg</sub> |                        |       |                      |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±500 V may actually have higher performance.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                   |                               | MIN   | MAX | UNIT |

|-----------------------------------|-------------------------------|-------|-----|------|

|                                   | VIN (main supply)             | 1.5   | 22  |      |

|                                   | VDD                           | 4.5   | 25  |      |

| Input voltage range               | VBST                          | 4.5   | 28  | V    |

|                                   | VBST (with respect to LL)     | 4.5   | 6.5 |      |

|                                   | EN, MODE, TRIP, RF, ROVP, VFB | - 0.1 | 6.5 |      |

| Output voltage range              | LL                            | - 1   | 27  | V    |

|                                   | PGOOD, VREG                   | - 0.1 | 6.5 | v    |

| Junction temperature range, $T_J$ |                               | - 40  | 125 | °C   |

## 7.4 Thermal Information

|                        |                                              | TPS53318<br>TPS53319 |      |

|------------------------|----------------------------------------------|----------------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DQP                  | UNIT |

|                        |                                              | 22 PINS              |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 27.2                 |      |

| R <sub>0 JC(top)</sub> | Junction-to-case (top) thermal resistance    | 17.1                 |      |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 5.9                  | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 0.8                  | C/vv |

| ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 5.8                  |      |

| R <sub>0 JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.2                  |      |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report.

## 7.5 Electrical Characteristics

Over recommended free-air temperature range,  $V_{VDD}$  = 12 V (unless otherwise noted)

|                        | PARAMETER                              | CONDITIONS                                                                               | MIN    | TYP   | MAX    | UNIT |

|------------------------|----------------------------------------|------------------------------------------------------------------------------------------|--------|-------|--------|------|

| SUPPLY CI              | JRRENT                                 |                                                                                          |        |       |        |      |

| V <sub>VIN</sub>       | VIN pin power conversion input voltage |                                                                                          | 1.5    |       | 22     | V    |

| V <sub>VDD</sub>       | Supply input voltage                   |                                                                                          | 4.5    |       | 25.0   | V    |

| I <sub>VIN(leak)</sub> | VIN pin leakage current                | V <sub>EN</sub> = 0 V                                                                    |        |       | 1      | μA   |

| I <sub>VDD</sub>       | VDD supply current                     | $T_{\rm A}$ = 25°C, No load, V <sub>EN</sub> = 5 V, V <sub>VFB</sub> = 0.630 V           |        | 420   | 590    | μA   |

| IVDDSDN                | VDD shutdown current                   | $T_A = 25^{\circ}C$ , No load, $V_{EN} = 0 V$                                            |        |       | 110    | μA   |

| INTERNAL               | REFERENCE VOLTAGE                      |                                                                                          |        |       |        |      |

| V <sub>VFB</sub>       | VFB regulation voltage                 | CCM condition <sup>(1)</sup>                                                             |        | 0.600 |        | V    |

|                        |                                        | T <sub>A</sub> = 25°C                                                                    | 0.597  | 0.600 | 0.603  |      |

| V <sub>VFB</sub>       | VFB regulation voltage                 | $0^{\circ}C \leqslant T_{A} \leqslant 85^{\circ}C$                                       | 0.5952 | 0.600 | 0.6048 | V    |

|                        |                                        | $-40^{\circ}C \leqslant T_{A} \leqslant 85^{\circ}C$                                     | 0.594  | 0.600 | 0.606  |      |

| I <sub>VFB</sub>       | VFB input current                      | V <sub>VFB</sub> = 0.630 V, T <sub>A</sub> = 25°C                                        |        | 0.01  | 0.20   | μA   |

| LDO OUTP               | UT                                     |                                                                                          |        |       |        |      |

| V <sub>VREG</sub>      | LDO output voltage                     | $0 \text{ mA} \leqslant I_{VREG} \leqslant 30 \text{ mA}$                                | 4.77   | 5.00  | 5.36   | V    |

| I <sub>VREG</sub>      | LDO output current <sup>(1)</sup>      | Maximum current allowed from LDO                                                         |        |       | 30     | mA   |

| V <sub>DO</sub>        | Low drop out voltage                   | V <sub>VDD</sub> = 4.5 V, I <sub>VREG</sub> = 30 mA                                      |        |       | 250    | mV   |

| BOOT STR               | AP SWITCH                              | -                                                                                        |        |       |        |      |

| V <sub>FBST</sub>      | Forward voltage                        | $V_{VREG-VBST}$ , $I_F$ = 10 mA, $T_A$ = 25°C                                            |        | 0.1   | 0.2    | V    |

| I <sub>VBSTLK</sub>    | VBST leakage current                   | V <sub>VBST</sub> = 23 V, V <sub>SW</sub> = 17 V, T <sub>A</sub> = 25°C                  |        | 0.01  | 1.50   | μA   |

| DUTY AND               | FREQUENCY CONTROL                      |                                                                                          |        |       |        |      |

| t <sub>OFF(min)</sub>  | Minimum off-time                       | T <sub>A</sub> = 25°C                                                                    | 150    | 260   | 400    | ns   |

| t <sub>ON(min)</sub>   | Minimum on-time                        | $V_{IN}$ = 17 V, $V_{OUT}$ = 0.6 V, $f_{SW}$ = 1<br>MHz,<br>$T_A$ = 25 °C <sup>(1)</sup> |        | 35    |        | ns   |

| SOFT-STAF              | RT TIMING                              |                                                                                          |        |       | 1      |      |

|                        |                                        | R <sub>MODE</sub> = 39 k Ω                                                               |        | 0.7   |        |      |

|                        | Internal soft-start time from          | R <sub>MODE</sub> = 100 k Ω                                                              |        | 1.4   |        |      |

| t <sub>SS</sub>        | $V_{OUT} = 0 V$ to 95% of $V_{OUT}$    | R <sub>MODE</sub> = 200 k Ω                                                              |        | 2.8   |        | ms   |

|                        |                                        | R <sub>MODE</sub> = 470 k Ω                                                              |        | 5.6   |        |      |

### TPS53318, TPS53319

ZHCS979F - JUNE 2012 - REVISED OCTOBER 2020

## Over recommended free-air temperature range, V<sub>VDD</sub> = 12 V (unless otherwise noted)

| -                                                 | PARAMETER                      | <u> </u> | CONDITIONS                                                                    | MIN    | TYP    | MAX    | UNIT   |

|---------------------------------------------------|--------------------------------|----------|-------------------------------------------------------------------------------|--------|--------|--------|--------|

| OUTPUT V                                          | OLTAGE DISCHARGE               |          | · · · · · · · · · · · · · · · · · · ·                                         | I      | I      |        |        |

| IDSCHG                                            | Output voltage discharge cu    | rrent    | V <sub>EN</sub> = 0 V, V <sub>SW</sub> = 0.5 V                                | 5.0    | 6.6    | 9.0    | mA     |

| POWERGO                                           | OD                             |          |                                                                               |        |        |        |        |

| V <sub>THPG</sub>                                 | PG threshold                   |          | PG in from lower                                                              | 92.5%  | 95.0%  | 98.5%  |        |

|                                                   |                                |          | PG in from higher                                                             | 107.5% | 110.0% | 112.5% |        |

|                                                   |                                |          | PG hysteresis                                                                 | 2.5%   | 5.0%   | 7.5%   |        |

| R <sub>PG</sub>                                   | PG transistor on-resistance    |          |                                                                               | 15     | 30     | 60     | Ω      |

| t <sub>PGDEL</sub>                                | PG delay                       |          | Delay for PG in                                                               | 0.8    | 1      | 1.2    | ms     |

| LOGIC THE                                         | RESHOLD AND SETTING CON        | DITIONS  |                                                                               |        |        |        |        |

| V <sub>EN</sub>                                   | EN Voltage                     |          | Enable                                                                        | 1.0    | 1.3    | 1.6    | .,     |

|                                                   |                                |          | Disable                                                                       | 0.8    | 1.0    | 1.2    | V      |

| I <sub>EN</sub>                                   | EN Input current               |          | V <sub>EN</sub> = 5 V                                                         |        |        | 1.0    | μA     |

|                                                   |                                |          | $R_{RF} = 0 \Omega$ to GND, $T_A = 25^{\circ}C^{(2)}$                         | 200    | 250    | 300    |        |

|                                                   |                                |          | $R_{\rm RF}$ = 187 k Ω to GND, $T_{\rm A}$ = 25°C <sup>(2)</sup>              | 250    | 300    | 350    |        |

|                                                   |                                |          | $R_{RF} = 619 \text{ k} \Omega$ , to GND, $T_{A} = 25^{\circ} \text{C}^{(2)}$ | 350    | 400    | 450    |        |

|                                                   |                                |          | $R_{RF} = Open, T_A = 25^{\circ}C^{(2)}$                                      | 450    | 500    | 550    |        |

| f <sub>SW</sub>                                   | Switching frequency            |          | $R_{RF} = 866 \text{ k} \Omega$ to VREG, $T_A = 25^{\circ} \text{C}^{(2)}$    | 540    | 600    | 660    | kHz    |

|                                                   |                                |          | $R_{RF} = 309 \text{ k}\Omega$ to VREG, $T_A = 25^{\circ}C^{(2)}$             | 670    | 750    | 820    |        |

|                                                   |                                |          |                                                                               |        |        |        |        |

|                                                   |                                |          | $R_{RF} = 124 \text{ k} \Omega$ to VREG, $T_A = 25^{\circ}C^{(2)}$            | 770    | 850    | 930    |        |

|                                                   |                                |          | $R_{RF} = 0 \Omega$ to VREG, $T_A = 25^{\circ}C^{(2)}$                        | 880    | 970    | 1070   |        |

|                                                   | ON: CURRENT SENSE              |          |                                                                               |        |        |        |        |

| I <sub>TRIP</sub>                                 | TRIP source current            |          | $V_{\text{TRIP}} = 1 \text{ V}, \text{ T}_{\text{A}} = 25^{\circ}\text{C}$    |        | 10     |        | μA     |

| TCITRIP                                           | TRIP current temperature co    |          | On the basis of 25°C <sup>(2)</sup>                                           |        | 3000   |        | ppm/°C |

| V <sub>TRIP</sub>                                 | Current limit threshold        | TPS53318 | V <sub>TRIP-GND</sub>                                                         | 0.4    |        | 1.5    | V      |

|                                                   | setting range                  | TPS53319 |                                                                               |        |        | 2.4    |        |

| V <sub>OCL</sub>                                  | Current limit threshold        |          | V <sub>TRIP</sub> = 1.2 V                                                     | 37.5   |        |        | mV     |

|                                                   |                                |          | V <sub>TRIP</sub> = 0.4                                                       |        | 12.5   |        |        |

| V <sub>OCLN</sub>                                 | Negative current limit thresh  | old      | V <sub>TRIP</sub> = 1.2 V                                                     |        | - 37.5 |        | mV     |

| OCLIN                                             |                                |          | $V_{TRIP} = 0.4 \text{ V}$                                                    |        | - 12.5 |        |        |

|                                                   |                                |          | $R_{TRIP}$ = 66.5 k $\Omega$ , 0°C $\leqslant$ $T_{A}$ $\leqslant$ 125°C      | 4.6    | 5.4    | 6.3    |        |

| I <sub>OCP</sub>                                  | Valley current limit threshold |          | $R_{TRIP}$ = 66.5 k $\Omega$ , $-$ 40°C $\leqslant$ $T_{A}$ $\leqslant$ 125°C | 4.4    | 5.4    | 6.3    | A      |

| M                                                 |                                |          | Positive                                                                      | 3      | 15     |        |        |

| V <sub>AZCADJ</sub>                               | Auto zero cross adjustable r   | ange     | Negative                                                                      |        | - 15   | - 3    | mV     |

| PROTECTI                                          | ON: UVP and OVP                |          | I I                                                                           |        |        |        |        |

| V <sub>OVP</sub>                                  | OVP trip threshold             |          | OVP detect                                                                    | 115%   | 120%   | 125%   |        |

| t <sub>OVPDEL</sub>                               | OVP propagation delay          |          | VFB delay with 50-mV overdrive                                                |        | 1      |        | μs     |

| V <sub>UVP</sub>                                  | Output UVP trip threshold      |          | UVP detect                                                                    | 65%    | 70%    | 75%    |        |

| t <sub>UVPDEL</sub>                               | Output UVP propagation del     | ay       |                                                                               | 0.8    | 1.0    | 1.2    | ms     |

|                                                   |                                |          | From enable to UVP workable                                                   | 1.5    | 2.3    | 3.0    | ms     |

|                                                   | Output UVP enable delay        |          |                                                                               |        |        |        |        |

| t <sub>UVPEN</sub>                                | Output UVP enable delay        |          |                                                                               |        |        |        |        |

| t <sub>UVPEN</sub><br>UVLO<br>V <sub>UVVREG</sub> | Output UVP enable delay        |          | Wake up                                                                       | 4.00   | 4.20   | 4.33   | V      |

### Over recommended free-air temperature range, $V_{VDD}$ = 12 V (unless otherwise noted)

|                     | PARAMETER                     | CONDITIONS                          | MIN        | TYP  | MAX  | UNIT |

|---------------------|-------------------------------|-------------------------------------|------------|------|------|------|

| PROTECTIO           | ON: UVP and OVP               | ·                                   |            | ¥    |      |      |

| V <sub>OVP</sub>    | OVP trip threshold            | OVP detect                          | 115%       | 120% | 125% |      |

| t <sub>OVPDEL</sub> | OVP propagation delay         | VFB delay with 50-mV overdrive      |            | 1    |      | μs   |

| V <sub>UVP</sub>    | Output UVP trip threshold     | UVP detect                          | 65%        | 70%  | 75%  |      |

| t <sub>UVPDEL</sub> | Output UVP proprogation delay |                                     | 0.8        | 1.0  | 1.2  | ms   |

| t <sub>UVPEN</sub>  | Output UVP enable delay       | From enable to UVP workable         | 1.5        | 2.3  | 3.0  | ms   |

| UVLO                |                               |                                     | - <b>i</b> |      |      |      |

| V                   | VREG UVLO threshold           | Wake up                             | 4.00       | 4.20 | 4.33 | V    |

| V <sub>UVVREG</sub> | VREG OVEO Intesnoid           | Hysteresis                          |            | 0.25 | V    |      |

| THERMAL             | SHUTDOW N                     |                                     |            |      |      |      |

| т                   | Thermal shutdown threshold    | Shutdown temperature <sup>(2)</sup> |            | 145  |      | °C   |

| T <sub>SDN</sub>    |                               | Hysteresis <sup>(2)</sup>           |            | 10   |      | C    |

|                     |                               |                                     |            |      |      |      |

(1) Ensured by design. Not production tested.

(2) Not production tested. Test condition is  $V_{IN}$  = 12 V,  $V_{OUT}$  = 1.2 V,  $I_{OUT}$  = 5 A using application circuit shown in [8] 9-12.

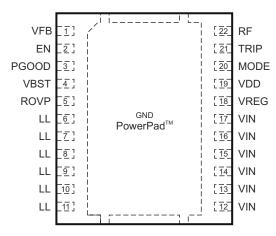

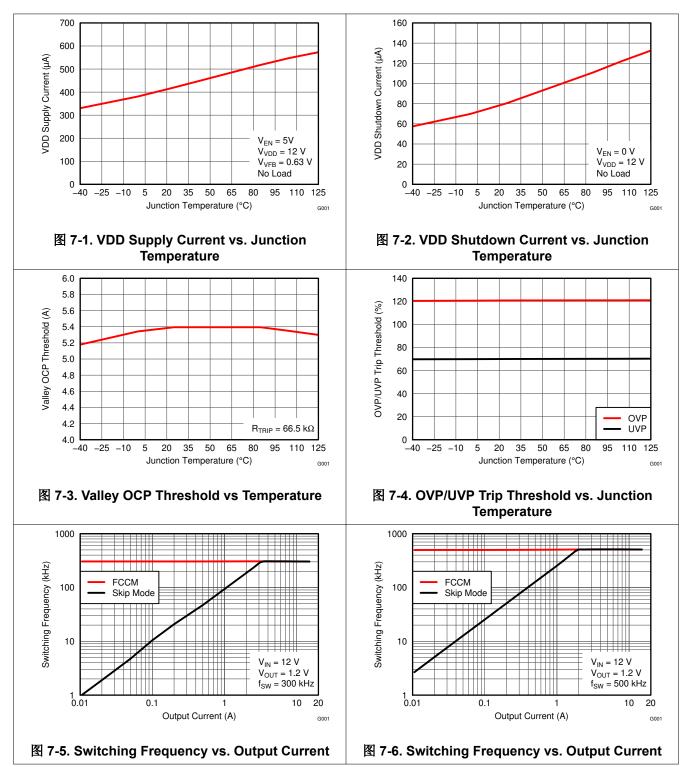

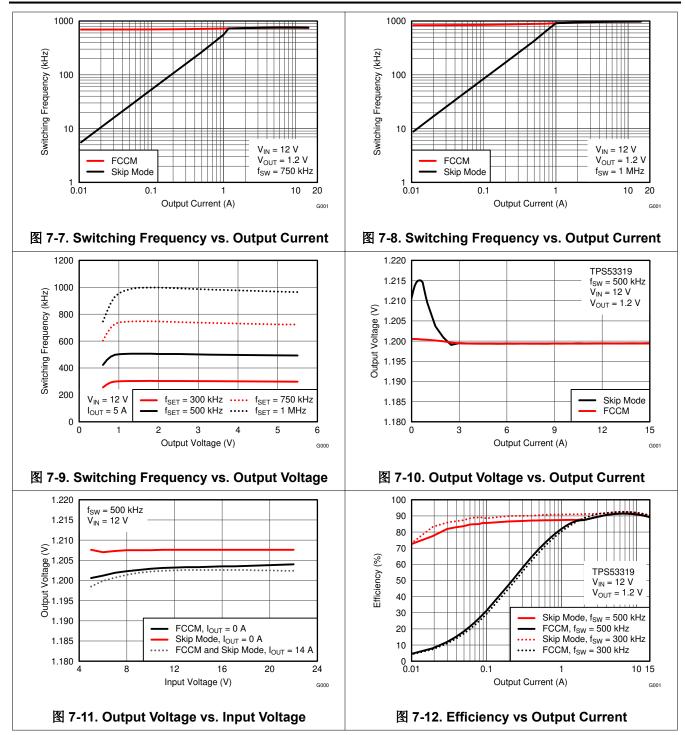

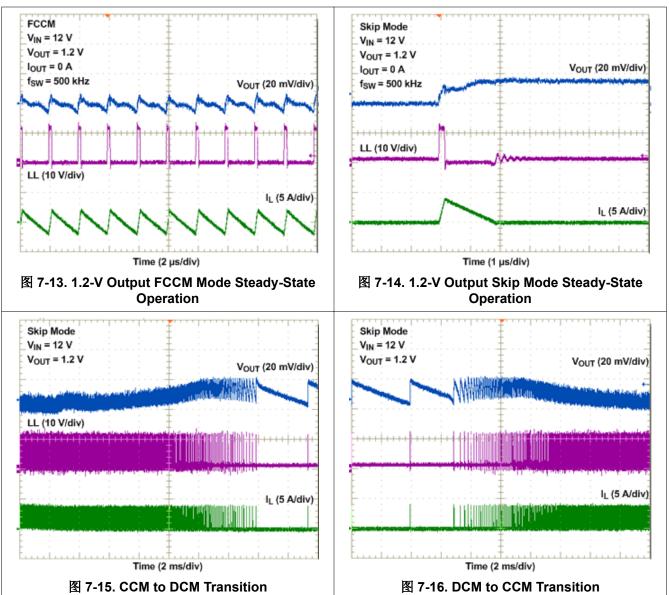

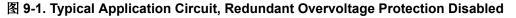

## 7.6 Typical Characteristics

Copyright © 2021 Texas Instruments Incorporated

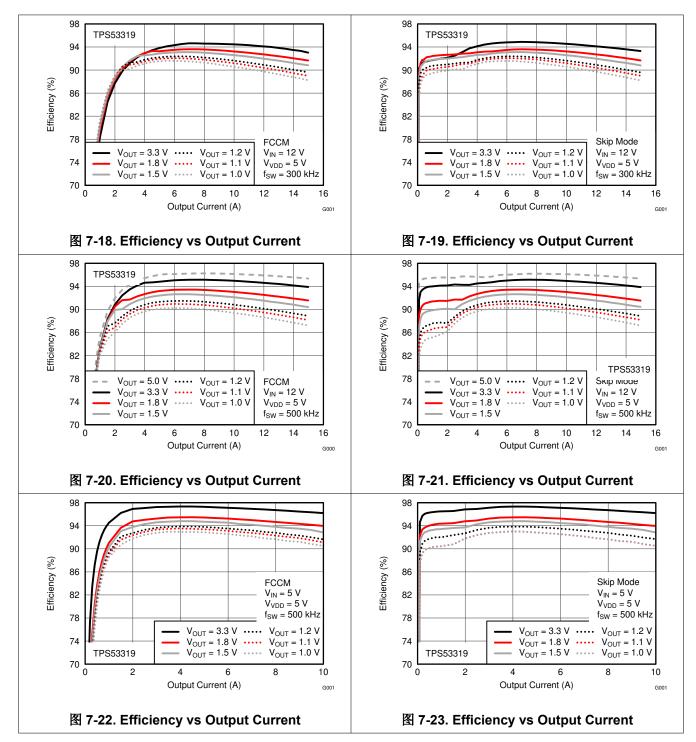

## 7.7 TPS53319 Typical Characteristics

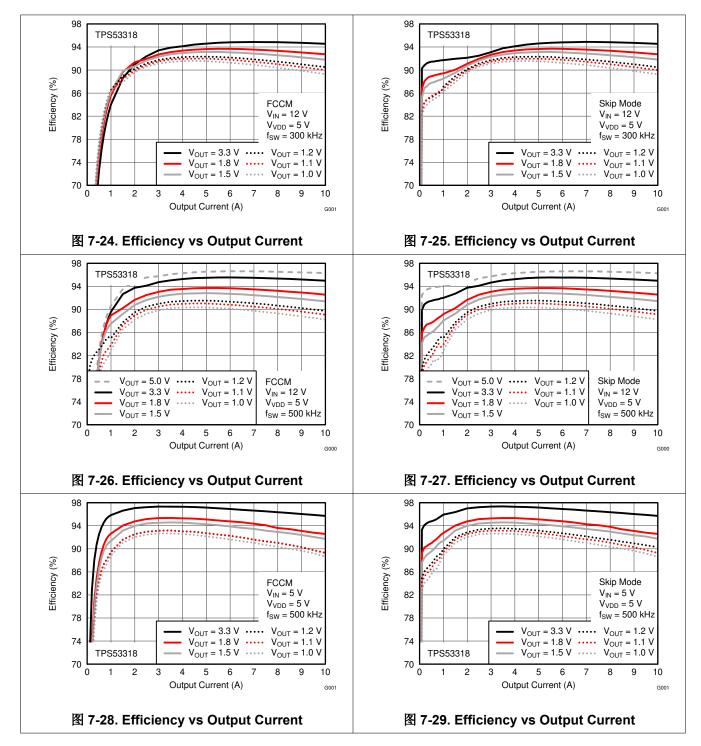

## 7.8 TPS53318 Typical Characteristics

## 8 Detailed Description

## 8.1 Overview

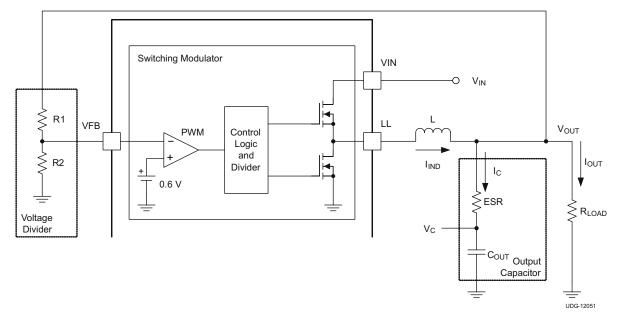

The TPS53318 and TPS53319 devices are high-efficiency, single channel, synchronous buck converters suitable for low output voltage point-of-load applications in computing and similar digital consumer applications. The device features proprietary D-CAP<sup>™</sup> mode control combined with an adaptive on-time architecture. This combination is ideal for building modern low duty ratio, ultra-fast load step response DC-DC converters. The output voltage ranges from 0.6 V to 5.5 V. The conversion input voltage range is from 1.5 V to 22 V and the VDD bias voltage is from 4.5 V to 25 V. The D-CAP mode uses the equivalent series resistance (ESR) of the output capacitor or capacitors to sense the device current. One advantage of this control scheme is that it does not require an external phase compensation network. This allows a simple design with a low external component count. Eight preset switching frequency values can be chosen using a resistor connected from the RF pin to ground or VREG. Adaptive on-time control tracks the preset switching frequency over a wide input and output voltage range while allowing the switching frequency to increase at the step-up of the load.

These devices have a MODE pin to select between auto-skip mode and forced continuous conduction mode (FCCM) for light load conditions. The MODE pin also sets the selectable soft-start time ranging from 0.7 ms to 5.6 ms as shown in  $\frac{1}{8}$  8-3.

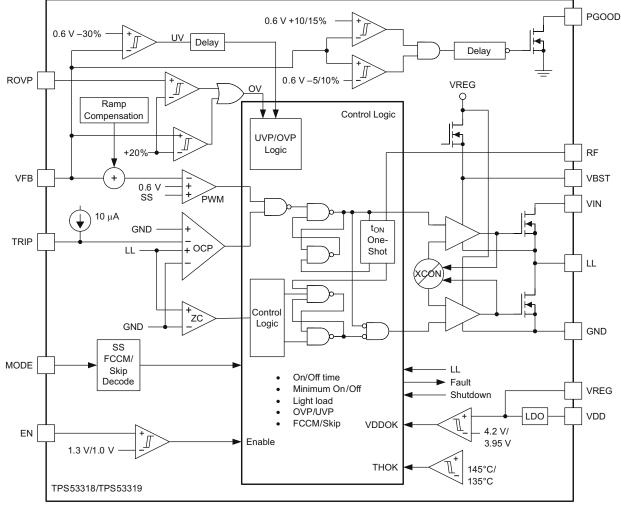

## 8.2 Functional Block Diagram

UDG-12041

A. The thresholds shown in # 8.2 are typical values. Refer to # 7.5 for threshold tolerance specifications.

## 8.3 Feature Description

## 8.3.1 5-V LDO and VREG Start-Up

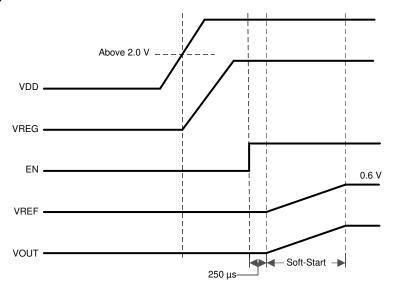

Both the TPS53318 and TPS53319 devices provide an internal 5-V LDO function using input from VDD and output to VREG. When the VDD voltage rises above 2 V, the internal LDO is enabled and outputs voltage to the VREG pin. The VREG voltage provides the bias voltage for the internal analog circuitry and also provides the supply voltage for the gate drives.

图 8-1. Power-Up Sequence Voltage Waveforms

The 5-V LDO is not controlled by the EN pin. The LDO starts-up any time VDD rises to approximately 2 V (see 8 8-1).

## 8.3.2 Adaptive On-Time D-CAP Control and Frequency Selection

Neither the TPS53318 nor the TPS53319 device have a dedicated oscillator to determine switching frequency. However, the device operates with pseudo-constant frequency by feedforwarding the input and output voltages into the on-time one-shot timer. The adaptive on-time control adjusts the on-time to be inversely proportional to the input voltage as shown in 方程式 1.

$$t_{ON} \propto \frac{V_{OUT}}{V_{IN}}$$

(1)

This makes the switching frequency fairly constant in steady state conditions over a wide input voltage range. The switching frequency is selectable from eight preset values by a resistor connected between the RF pin and GND or between the RF pin and the VREG pin as shown in  $\frac{1}{2}$  8-1. Maintaining open resistance sets the switching frequency to 500 kHz.

Note

|              | SISTOR (R <sub>RF</sub> )<br>NNECTIONS | SWITCHING<br>FREQUENCY      |

|--------------|----------------------------------------|-----------------------------|

| VALUE (k Ω ) | CONNECT TO                             | (f <sub>SW</sub> )<br>(kHz) |

| 0            | GND                                    | 250                         |

| 187          | GND                                    | 300                         |

| 619          | GND                                    | 400                         |

| OPEN         | n/a                                    | 500                         |

| 866          | VREG                                   | 600                         |

| 309          | VREG                                   | 750                         |

| 124          | VREG                                   | 850                         |

| 0            | VREG                                   | 970                         |

### 表 8-1. Resistor and Switching Frequency

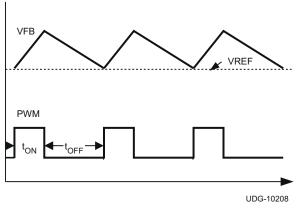

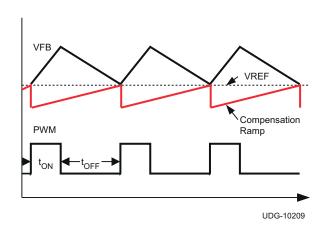

The off-time is modulated by a PWM comparator. The VFB node voltage (the mid-point of resistor divider) is compared to the internal 0.6-V reference voltage added with a ramp signal. When both signals match, the PWM comparator asserts a set signal to terminate the off-time (turn off the low-side MOSFET and turn on high-side the MOSFET). The set signal is valid if the inductor current level is below the OCP threshold, otherwise the off-time is extended until the current level falls below the threshold.

The waveforms shown in 🗏 8-2 show on-time control without ramp compensation. The waveforms shown in 🖺 8-3 show on-time control without ramp compensation.

图 8-2. On-Time Control Without Ramp Compensation

图 8-3. On-Time Control With Ramp Compensation

## 8.3.3 Ramp Signal

The TPS53318 and TPS53319 devices add a ramp signal to the 0.6-V reference in order to improve jitter performance. As described in the previous section, the feedback voltage is compared with the reference information to keep the output voltage in regulation. By adding a small ramp signal to the reference, the signal-to-noise ratio at the onset of a new switching cycle is improved. Therefore the operation becomes less jittery and more stable. The ramp signal is controlled to start with -7 mV at the beginning of an on-cycle and becomes 0 mV at the end of an off-cycle in steady state.

During skip mode operation, under discontinuous conduction mode (DCM), the switching frequency is lower than the nominal frequency and the off-time is longer than the off-time in CCM. Because of the longer off-time, the ramp signal extends after crossing 0 mV. However, it is clamped at 3 mV to minimize the DC offset.

## 8.3.4 Adaptive Zero Crossing

The TPS53318 and TPS53319 devices have an adaptive zero crossing circuit which performs optimization of the zero inductor current detection at skip mode operation. This function pursues ideal low-side MOSFET turning off

timing and compensates inherent offset voltage of the Z-C comparator and delay time of the Z-C detection circuit. It prevents SW-node swing-up caused by too late detection and minimizes diode conduction period caused by too early detection. As a result, better light load efficiency is delivered.

## 8.3.5 Output Discharge Control

When the EN pin becomes low, the TPS53318 and TPS53319 devices discharge the output capacitor using the internal MOSFET connected between the SW pin and the PGND pin while the high-side and low-side MOSFETs are maintained in the OFF state. The typical discharge resistance is 75  $\Omega$ . The soft discharge occurs only as EN becomes low. The discharge circuit is powered by VDD. While VDD remains high, the discharge circuit remains active.

### 8.3.6 Power-Good

The TPS53318 and TPS53319 devices have power-good output that indicates high when switcher output is within the target. The power-good function is activated after soft-start has finished. If the output voltage becomes within +10% and -5% of the target value, internal comparators detect power-good state and the power-good signal becomes high after a 1-ms internal delay. If the output voltage goes outside of +15% or -10% of the target value, the power-good signal becomes low after two microsecond (2-  $\mu$  s) internal delay. The power-good output is an open drain output and must be pulled up externally.

The power-good MOSFET is powered through the VDD pin.  $V_{VDD}$  must be >1 V in order to have a valid power-good logic. It is recommended to pull PGOOD up to VREG (or a voltage divided from VREG).

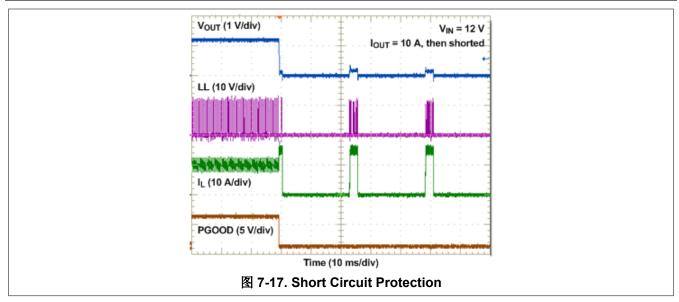

## 8.3.7 Current Sense, Overcurrent, and Short Circuit Protection

The TPS53318 and TPS53319 device offer cycle-by-cycle overcurrent limiting control. The inductor current is monitored during the *OFF* state and the controller maintains the *OFF* state during the period in that the inductor current is larger than the overcurrent trip level. In order to provide both good accuracy and cost effective solution, the TPS53319 device supports temperature compensated MOSFET  $R_{DS(on)}$  sensing. The TRIP pin should be connected to GND through the trip voltage setting resistor,  $R_{TRIP}$ . The TRIP terminal sources current ( $I_{TRIP}$ ) which is 10  $\mu$  A typically at room temperature, and the trip level is set to the OCL trip voltage V<sub>TRIP</sub> as shown in  $\overline{\mathcal{FRIR}}$  2.

$$V_{\text{TRIP}}(\mathsf{m}\mathsf{V}) = \mathsf{R}_{\text{TRIP}}(\mathsf{k}\Omega) \times \mathsf{I}_{\text{TRIP}}(\mu\mathsf{A})$$

<sup>(2)</sup>

The inductor current is monitored by the LL pin. The GND pin is used as the positive current sensing node and the LL pin is used as the negative current sense node. The trip current,  $I_{TRIP}$  has a 3000ppm/°C temperature slope to compensate the temperature dependency of the  $R_{DS(on)}$ . For each device,  $I_{TRIP}$  is also adjusted based on the device-specific on-resistance measurement in production tests to eliminate the any OCP variation from device to device. Duty-cycle should not be over 45% in order to provide the most accurate OCP.

As the comparison is made during the *OFF* state,  $V_{TRIP}$  sets the valley level of the inductor current. Thus, the load current at the overcurrent threshold,  $I_{OCP}$ , can be calculated as shown in 5程式 3.

$$I_{OCP} = \frac{V_{TRIP}}{(32 \times R_{DS(on)})} + \frac{I_{IND(ripple)}}{2} = \frac{R_{TRIP}}{12.3 \times 10^3} + \frac{1}{2 \times L \times f_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$$

(3)

where

•  $R_{TRIP}$  is in  $\Omega$

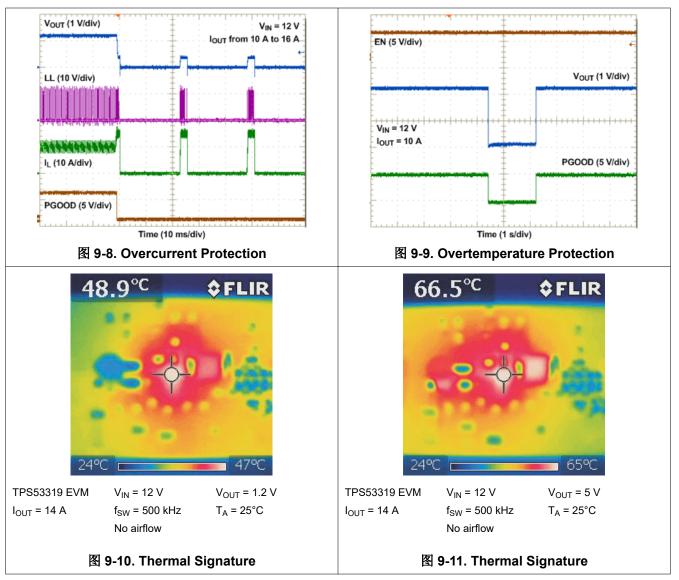

In an overcurrent or short-circuit condition, the current to the load exceeds the current to the output capacitor thus the output voltage tends to decrease. Eventually, it crosses the undervoltage protection threshold and shuts down. After a hiccup delay (16 ms plus 0.7 ms soft-start period), the controller restarts. If the overcurrent condition remains, the procedure is repeated and the device enters hiccup mode.

Copyright © 2021 Texas Instruments Incorporated

$t_{HIC(wait)} = (2^n + 257) \times 4 \, \mu s$

• n = 8, 9, 10, or 11 depending on soft-start time selection

$$t_{HIC(dly)} = 7 \times (2^n + 257) \times 4 \mu s$$

|                                                 | A 0-2. Incoup Inning                              |                                                     |

|-------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|

| SELECTED SOFT-START TIME (t <sub>SS</sub> )(ms) | HICCUP WAIT TIME<br>(t <sub>HIC(wait)</sub> )(ms) | HICCUP DELAY TIME<br>(t <sub>HIC(delay)</sub> )(ms) |

| 0.7                                             | 2.052                                             | 14.364                                              |

| 1.4                                             | 3.076                                             | 21.532                                              |

| 2.8                                             | 5.124                                             | 35.868                                              |

| 5.6                                             | 9.220                                             | 64.540                                              |

表 8-2. Hiccup Timing

For the TPS53318 device, the OCP threshold is internally clamped to 10.5 A. The recommended  $R_{TRIP}$  value for the TPS53318 device is less than 150 k  $\Omega$ .

### 8.3.8 Overvoltage and Undervoltage Protection

The TPS53318 and TPS53319 devices monitor the resistor divided feedback voltage to detect overvoltage and undervoltage. When the feedback voltage becomes lower than 70% of the target voltage, the UVP comparator output goes high and an internal UVP delay counter begins counting. After 1 ms, the device latches OFF both high-side and low-side MOSFETs drivers. The controller restarts after a hiccup delay (refer to  $\frac{1}{5}$  8-2). This function is enabled 1.5-ms after the soft start is completed.

When the feedback voltage becomes higher than 120% of the target voltage, the OVP comparator output goes high and the circuit latches OFF the high-side MOSFET driver and latches ON the low-side MOSFET driver. The output voltage decreases. Before the latch-off action for both the high-side and low-side drivers, the output voltage must be pulled down below the UVP threshold voltage for a period of 1 ms. After the 1 ms period, the drivers are latched off.

## 8.3.9 Redundant Overvoltage Protection (OVP)

The TPS53318 and TPS53319 devices have a redundant input for OVP protection. The ROVP pin senses the voltage divided from output voltage and sends it to the OVP comparator. If this voltage is higher than 120% of the target voltage, the overvoltage protection engages and the low-side FET is turned on. When the output voltage is lower than the UVP threshold then the device latches off.

This redundant OVP function typically protects against a situation where the feedback loop is open or where a VFB pin short to GND exists. The ROVP pin has an internal 1.5-M  $\Omega$  pulldown resistor.

#### Note

For an application that does not require a redundant OVP feature, tie the ROVP pin to GND. Do not leave ROVP pin floating.

## 8.3.10 UVLO Protection

The TPS53318 and TPS53319 devices use VREG undervoltage lockout protection (UVLO). When the VREG voltage is lower than 3.95 V, the device shuts off. When the VREG voltage is higher than 4.2 V, the device restarts. This is a non-latch protection.

(4)

#### 8.3.11 Thermal Shutdown

The TPS53318 and TPS53319 devices monitor the internal die temperature. If the temperature exceeds the threshold value (typically 145°C), the device shuts down. When the temperature falls about 10°C below the threshold value, the device will turn back on. This is a non-latch protection.

#### 8.3.12 Small Signal Model

From small-signal loop analysis, a buck converter using D-CAP mode can be simplified as shown in 🛽 8-4.

图 8-4. Simplified Modulator Model

The output voltage is compared with the internal reference voltage (ramp signal is ignored here for simplicity). The PWM comparator determines the timing to turn on the high-side MOSFET. The gain and speed of the comparator can be assumed high enough to keep the voltage at the beginning of each on cycle substantially constant.

$$H(s) = \frac{1}{s \times ESR \times C_{OUT}}$$

(6)

For loop stability, the 0-dB frequency,  $f_0$ , defined below needs to be lower than 1/4 of the switching frequency.

$$f_0 = \frac{1}{2\pi \times \text{ESR} \times C_{\text{OUT}}} \le \frac{f_{\text{SW}}}{4}$$

(7)

According to  $\overline{\beta}$   $\overline{R}$ , the loop stability of D-CAP mode modulator is mainly determined by the chemistry of the capacitor. For example, specialty polymer capacitors (SP-CAP) have an output capacitance in the order of several 100 µF and ESR in range of 10 m  $\Omega$ . These make  $f_0$  on the order of 100 kHz or less, creating a stable loop. However, ceramic capacitors have an  $f_0$  at more than 700 kHz, and need special care when used with this modulator. An application circuit for ceramic capacitor is described in # 8.3.13.

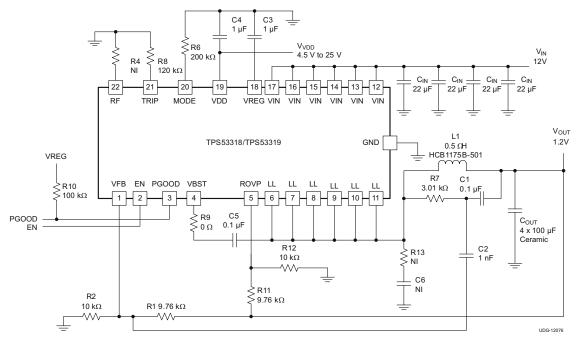

## 8.3.13 External Component Selection Using All Ceramic Output Capacitors

When a ceramic output capacitor is used, the stability criteria in  $\overline{\beta}$  程式 7 cannot be satisfied. The ripple injection approach as shown in  $\[Begin{subarray}{c}9-1\]$  is implemented to increase the ripple on the VFB pin and make the system stable. In addition to the selections made using steps 1 through step 6 in  $\[Begin{subarray}{c}9-2.1.2\]$ , the ripple injection components must be selected. The C2 value can be fixed at 1 nF. The value of C1 can be selected between 10 nF to 200 nF.

(8)

$$\frac{L \times C_{OUT}}{R7 \times C1} > N \times \frac{t_{ON}}{2}$$

where

• N is the coefficient to account for L and C<sub>OUT</sub> variation

N is also used to provide enough margin for stability. It is recommended that N = 2 for  $V_{OUT} \le 1.8$  V and N = 4 for  $V_{OUT} \ge 3.3$  V or when L  $\le 250$  nH. The higher  $V_{OUT}$  needs a higher N value because the effective output capacitance is reduced significantly with higher DC bias. For example, a 6.3-V, 22-µF ceramic capacitor may have only 8 µF of effective capacitance when biased at 5 V.

Because the VFB pin voltage is regulated at the valley, the increased ripple on the VFB pin causes the increase of the VFB DC value. The AC ripple coupled to the VFB pin has two components, one coupled from SW node and the other coupled from the VOUT pin and they can be calculated using 523 and 5210 when neglecting the output voltage ripple caused by equivalent series inductance (ESL).

$$V_{INJ\_SW} = \frac{V_{IN} - V_{OUT}}{R7 \times C1} \times \frac{D}{f_{SW}}$$

(9)

$$V_{INJ_OUT} = ESR \times I_{IND(ripple)} + \frac{I_{IND(ripple)}}{8 \times C_{OUT} \times f_{SW}}$$

(10)

The DC voltage at the VFB pin can be calculated by 方程式 11:

$$V_{VFB} = 0.6 + \frac{V_{INJ}_{SW} + V_{INJ}_{OUT}}{2}$$

(11)

And the resistor divider value can be determined by 方程式 12:

$$R1 = \frac{V_{OUT} - V_{VFB}}{V_{VFB}} \times R2$$

(12)

## 8.4 Device Functional Modes

## 8.4.1 Enable, Soft Start, and Mode Selection

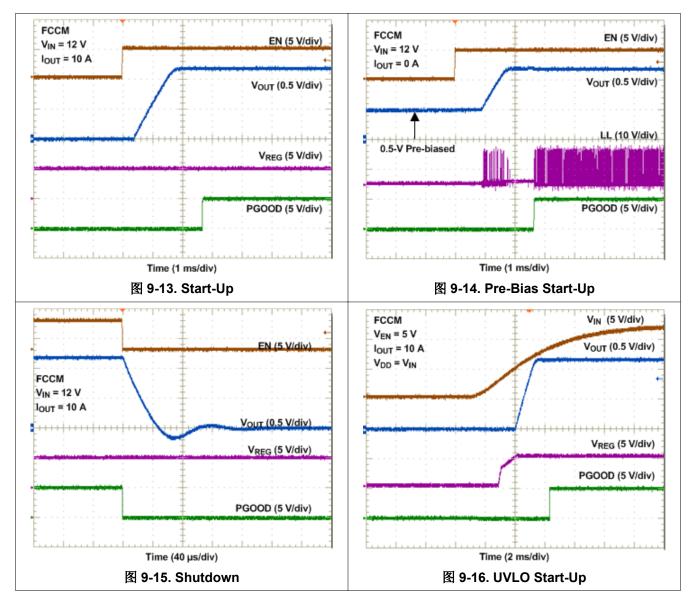

When the EN pin voltage rises above the enable threshold voltage (typically 1.3 V), the controller enters its startup sequence. The internal LDO regulator starts immediately and regulates to 5 V at the VREG pin. The controller calibrates the switching frequency setting resistance attached to the RF pin during the first 250  $\mu$  s. It then stores the switching frequency code in the internal registers. During this period, the MODE pin also senses the resistance attached to this pin and determines the soft-start time. Switching is inhibited during this phase. In the second phase, an internal DAC starts ramping up the reference voltage from 0 V to 0.6 V. Depending on the MODE pin setting, the ramping up time varies from 0.7 ms to 5.6 ms. Smooth and constant ramp-up of the output voltage is maintained during start-up regardless of load current.

#### Note

Enable voltage should not higher then VREG for 0.8 V.

| MODE SELECTION            | ACTION           | SOFT-START TIME<br>(t <sub>SS</sub> ) (ms) | R <sub>MODE</sub> (kΩ) |

|---------------------------|------------------|--------------------------------------------|------------------------|

|                           |                  | 0.7                                        | 39                     |

| Auto Skip                 | Pull down to GND | 1.4                                        | 100                    |

|                           |                  | 2.8                                        | 200                    |

|                           |                  | 5.6                                        | 475                    |

|                           |                  | 0.7                                        | 39                     |

| Forced CCM <sup>(1)</sup> |                  | 1.4                                        | 100                    |

|                           | Connect to PGOOD | 2.8                                        | 200                    |

|                           |                  | 5.6                                        | 475                    |

## 表 8-3. Soft-Start and MODE Settings

(1) Device enters FCCM after the PGOOD pin goes high when MODE is connected to PGOOD through the resistor  $R_{MODE}$ .

After the soft-start period begins, the MODE pin becomes the input of an internal comparator which determines auto skip or FCCM mode operation. If MODE voltage is higher than 1.3 V, the converter enters into FCCM mode. Otherwise it operates in auto skip mode at light-load condition. Typically, when FCCM mode is selected, the MODE pin connects to the PGOOD pin through the R<sub>MODE</sub> resistor, so that before PGOOD goes high, the converter remains in auto skip mode.

### 8.4.2 Auto-Skip Eco-mode Light Load Operation

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$$

(13)

where

•  $f_{SW}$  is the PWM switching frequency

Switching frequency versus output current in the light-load condition is a function of L, V<sub>IN</sub> and V<sub>OUT</sub>, but it decreases almost proportionally to the output current from the  $I_{OUT(LL)}$  given in au# 13. For example, it is 60 kHz at  $I_{OUT(LL)}$ /5 if the frequency setting is 300 kHz.

## 8.4.3 Forced Continuous Conduction Mode

When the MODE pin is tied to PGOOD through a resistor, the controller keeps continuous conduction mode (CCM) in light load condition. In this mode, switching frequency is kept almost constant over the entire load range which is suitable for applications need tight control of the switching frequency at a cost of lower efficiency.

## 9 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

The TPS53318 and TPS53319 devices are high-efficiency, single channel, synchronous buck converters suitable for low output voltage point-of-load applications in computing and similar digital consumer applications. The device features proprietary D-CAP mode control combined with an adaptive on-time architecture. This combination is ideal for building modern low duty ratio, ultra-fast load step response DC-DC converters. The output voltage ranges from 0.6 V to 5.5 V. The conversion input voltage range is from 1.5 V to 22 V and the VDD bias voltage is from 4.5 V to 25 V. The D-CAP mode uses the equivalent series resistance (ESR) of the output capacitor or capacitors to sense the device current. One advantage of this control scheme is that it does not require an external phase compensation network allowing for a simple design with a low external component count. Eight preset switching frequency values can be chosen using a resistor connected from the RF pin to ground or VREG. Adaptive on-time control tracks the preset switching frequency over a wide input and output voltage range while allowing the switching frequency to increase at the step-up of the load.

## 9.2 Typical Applications

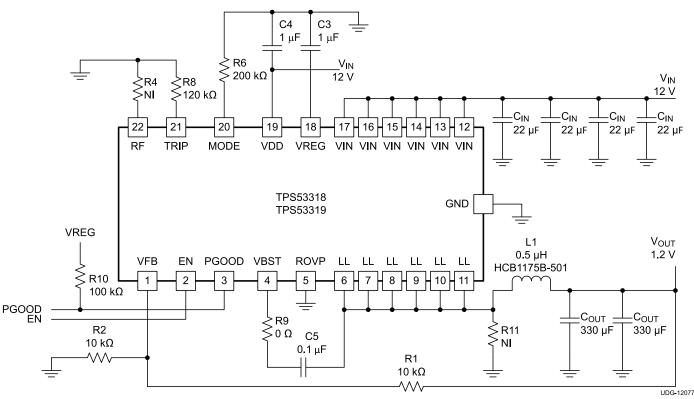

9.2.1 Application Using Bulk Output Capacitors, Redundant Overvoltage Protection Function (OVP) Disabled

#### 9.2.1.1 Design Requirements

This design uses the parameters listed in  $\frac{1}{5}$  9-1.

|                     | PARAMETER                 | TEST CONDITIONS                                                               | MIN  | TYP   | MAX  | UNIT             |  |

|---------------------|---------------------------|-------------------------------------------------------------------------------|------|-------|------|------------------|--|

| INPUT CI            | HARACTERISTICS            |                                                                               |      |       |      |                  |  |

| V <sub>IN</sub>     | Voltage range             |                                                                               | 5    | 12    | 18   | V                |  |

|                     | Maximum input current     | V <sub>IN</sub> = 5 V, I <sub>OUT</sub> = 8 A                                 |      |       | A    |                  |  |

| I <sub>MAX</sub>    | No load input current     | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 0 A with auto-skip<br>mode         |      | 1     |      | mA               |  |

| OUTPUT              | CHARACTERISTICS           |                                                                               |      |       |      | 1                |  |

|                     | Output voltage            |                                                                               |      | 1.2   |      |                  |  |

| V <sub>OUT</sub>    |                           | Line regulation, 5 V $\leqslant$ V $_{IN}$ $\leqslant$ 14 V with FCCM         | 0.2% |       |      | v                |  |

|                     | Output voltage regulation | Load regulation, V_IN = 12 V, 0 A $\leqslant$ I_OUT $\leqslant$ 8 A with FCCM |      | 0.5%  |      |                  |  |

| V <sub>RIPPLE</sub> | Output voltage ripple     | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 8 A with FCCM                      |      | 10    |      | mV <sub>PP</sub> |  |

| I <sub>LOAD</sub>   | Output load current       |                                                                               | 0    |       | 8    | •                |  |

| I <sub>OVER</sub>   | Output overcurrent        |                                                                               |      | 11    |      | A                |  |

| t <sub>ss</sub>     | Soft-start time           |                                                                               |      | 1     |      | ms               |  |

| SYSTEM              | S CHARACTERISTICS         |                                                                               |      |       |      |                  |  |

| f <sub>SW</sub>     | Switching frequency       |                                                                               |      | 500   | 1000 | kHz              |  |

| -                   | Peak efficiency           | V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = 1.2 V, I <sub>OUT</sub> = 4 A      |      | 91%   |      |                  |  |

| η                   | Full load efficiency      | V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = 1.2 V, I <sub>OUT</sub> = 8 A      |      | 91.5% |      | 1                |  |

| T <sub>A</sub>      | Operating temperature     |                                                                               |      | 25    |      | °C               |  |

### 9.2.1.2 Detailed Design Procedure

The external components selection is a simple process when using organic semiconductors or special polymer output capacitors.

#### 9.2.1.2.1 Step One: Select Operation Mode and Soft-Start Time

Select operation mode and soft-start time using  $\frac{1}{8}$  8-3.

#### 9.2.1.2.2 Step Two: Select Switching Frequency

Select the switching frequency from 250 kHz to 1 MHz using  $\frac{1}{8}$  8-1.

#### 9.2.1.2.3 Step Three: Choose the Inductor

The inductance value should be determined to give the ripple current of approximately 1/4 to 1/2 of maximum output current. Larger ripple current increases output ripple voltage and improves signal-to-noise ratio and helps ensure stable operation, but increases inductor core loss. Using 1/3 ripple current to maximum output current ratio, the inductance can be determined by  $\beta$ R14.

$$L = \frac{1}{I_{IND(ripple)} \times f_{SW}} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}} = \frac{3}{I_{OUT(max)} \times f_{SW}} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}}$$

(14)

The inductor requires a low DCR to achieve good efficiency. It also requires enough room above peak inductor current before saturation. The peak inductor current can be estimated in 5  $\pm$  15.

$$I_{\text{IND(peak)}} = \frac{V_{\text{TRIP}}}{32 \times R_{\text{DS(on)}}} + \frac{1}{L \times f_{\text{SW}}} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}}$$

(15)

#### Copyright © 2021 Texas Instruments Incorporated

#### 9.2.1.2.4 Step Four: Choose the Output Capacitor or Capacitors

When organic semiconductor capacitor or capacitors or specialty polymer capacitor or capacitors are used, loop stability, capacitance, and ESR should satisfy 57. For jitter performance, 16 is a good starting point to determine ESR.

$$\mathsf{ESR} = \frac{\mathsf{V}_{\mathsf{OUT}} \times 10\,\mathsf{mV} \times (1-\mathsf{D})}{0.6\,\mathsf{V} \times \mathsf{I}_{\mathsf{IND}}(\mathsf{ripple})} = \frac{10\,\mathsf{mV} \times \mathsf{L} \times \mathsf{f}_{\mathsf{SW}}}{0.6\,\mathsf{V}} = \frac{\mathsf{L} \times \mathsf{f}_{\mathsf{SW}}}{60}(\Omega) \tag{16}$$

where

- D is the duty factor

- The required output ripple slope is approximately 10 mV per t<sub>SW</sub> (switching period) in terms of VFB terminal voltage

#### 9.2.1.2.5 Step Five: Determine the Value of R1 and R2

The output voltage is programmed by the voltage-divider resistor, R1 and R2 shown in 图 8-4. R1 is connected between VFB pin and the output, and R2 is connected between the VFB pin and GND. Recommended R2 value is from 10 k  $\Omega$  to 20 k  $\Omega$ . Determine R1 using 方程式 17.

$$R1 = \frac{V_{OUT} - \frac{I_{IND(ripple)} \times ESR}{2} - 0.6}{0.6} \times R2$$

(17)

#### 9.2.1.2.6 Step Six: Choose the Overcurrent Setting Resistor

The overcurrent setting resistor,  $R_{TRIP}$ , can be determined by 5程式 18.

$$R_{TRIP} = \left(I_{OCP} - \left(\frac{1}{2 \times L \times f_{SW}}\right) \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}\right) \times 12.3$$

(18)

where

•  $R_{TRIP}$  is in k  $\Omega$

## 9.2.1.3 Application Curves

9.2.2 Application Using Ceramic Output Capacitors, Redundant Overvoltage Protection Function (OVP) Enabled

图 9-12. Typical Application Circuit, Redundent OVP Enabled

### 9.2.2.1 Design Requirements

This design uses the parameters listed in 表 9-1.

#### 9.2.2.2 Detailed Design Procedure

The detailed design procedure for this design example is similar to the procedure for the previous design example. The differences are discussed in the following two sections.

#### 9.2.2.2.1 External Component Selection Using All Ceramic Output Capacitors

Refer to  $\frac{1}{7}$  8.3.13 for guidelines for this design with all ceramic output capacitors.

#### 9.2.2.2.2 Redundant Overvoltage Protection

The redundant overvoltage level is programmed according to the output voltage setting, it is controlled by resistors R11 and R12 as shown in 39-12. Connect resistor R11 between the ROVP pin and the output, and connect resistor R12 between the ROVP pin and GND. This design recommends that the value of resistor R11 match the value of resistor R1 (or slightly higher), and that the value of resistor R2 match the value of resistor R12.

TPS53318, TPS53319 ZHCS979F - JUNE 2012 - REVISED OCTOBER 2020

## 9.2.2.3 Application Curves

## **10 Power Supply Recommendations**

The devices are designed to operate from an input voltage supply range between 1.5 V and 22 V (4.5 V to 25 V biased). This input supply must be well regulated. Proper bypassing of input supplies and internal regulators is also critical for noise performance, as is PCB layout and grounding scheme. See the recommendations in # 11.

## 11 Layout

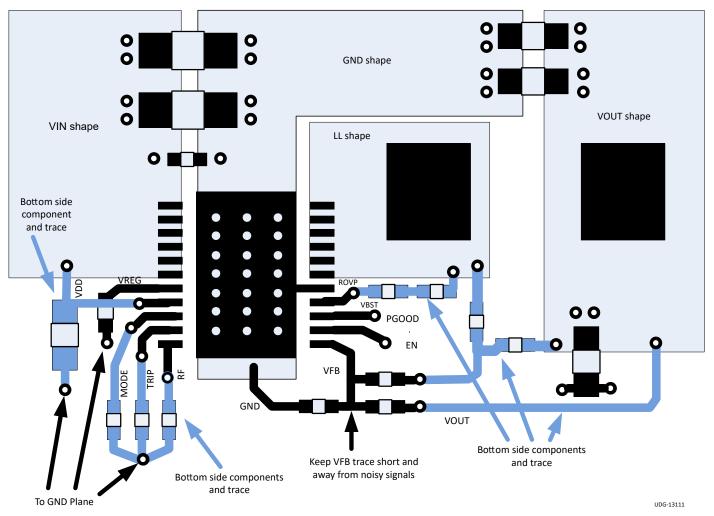

## **11.1 Layout Guidelines**

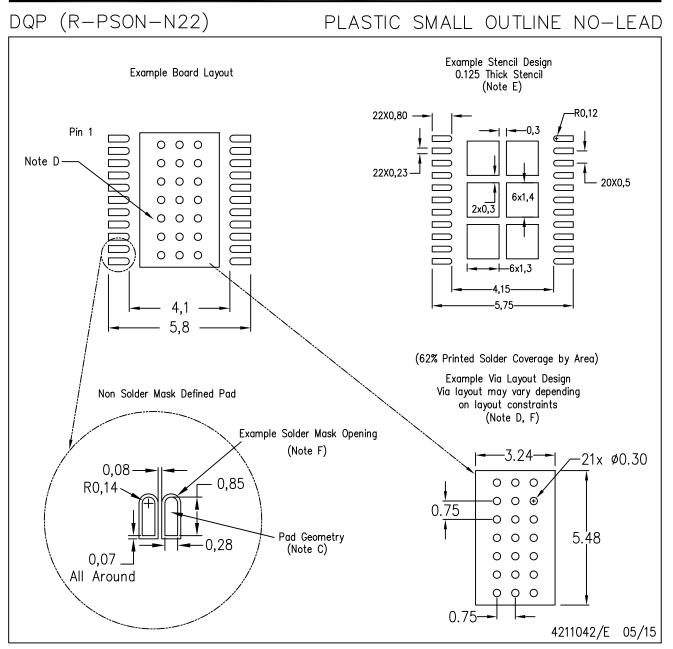

- The power components (including input/output capacitors, inductor, and TPS53318 or TPS53319 device) should be placed on one side of the PCB (solder side). At least one inner plane should be inserted, connected to ground, to shield and isolate the small signal traces from noisy power lines.

- All sensitive analog traces and components such as VFB, PGOOD, TRIP, MODE, and RF should be placed away from high-voltage switching nodes such as LL, VBST to avoid coupling. Use internal layer or layers as ground plane or planes and shield feedback trace from power traces and components.

- Place the VIN decoupling capacitors as close to the VIN and PGND pins as possible to minimize the input AC current loop.