# Dual channel transceiver IC for SIO and IO-Link sensor applications

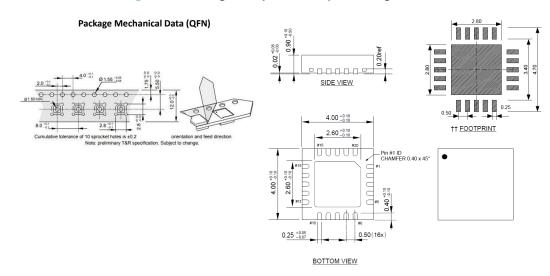

QFN 20L (4x4 mm)

# Product status link L6364

| Product summary |         |  |  |  |  |

|-----------------|---------|--|--|--|--|

| Order code      | Package |  |  |  |  |

| L6364Q          | QFN 20L |  |  |  |  |

#### **Features**

- Supply voltage from 5 V to 35 V

- 5 V and 3.3 V compatible I/Os

- 5 V and 3.3 V, 50 mA linear regulators

- 50 mA DC-DC regulator with configurable frequency (0.5 MHz to 2 MHz) & voltage (5 V-10.5 V)

- Low dissipative (5 Ω) CQ and DIO output stages configurable in high side, low side, push/pull

- Configurable (0.11 A to 0.25 A) current limitation threshold of CQ and DIO lines

- Configurable (0.22 A to 0.5 A) current limitation threshold of CQ//DIO line (Join Mode)

- Fully protected:

- Embedded reverse polarisation diode (DOUT pin)

- Full zero current reverse polarity between Vplus, CQ, DIO and PGND pins

- Configurable (up to 216°C) thermal shutdown threshold

- 7-bit, calibrated, temperature measurement

- Configurable (6.0 V to 15 V) Vplus undervoltage detection

- CQ and DIO short-circuit current limit and reporting

- -40 to +150°C operating temperature

- · Suitable to drive L, C and R loads

- Quartz-free IO-Link clock extraction and timing generation at COM2 (38.4k Baud) and COM3 (230.4k Baud)

- Integrated UART peripheral with M-sequence handling (inc. checksum) for all IO-Link sequences according to specification v1.1

- Single octet UART mode for unlimited M-sequence size and continuous data transfer

- · Internal data buffer for up to 15 octets

- · Transparent UART mode for special applications

- CQ and DIO switching time = 100 ns ( $2k \Omega / 2.2 \text{ nF load}$ )

- 8 V Zener limits for fast demagnetization of inductive loads

- Two LED drivers with configurable (up to 8 mA) current

- Design to meet application requirements:

- ESD IEC 61000-4-2 protection to 4 kV

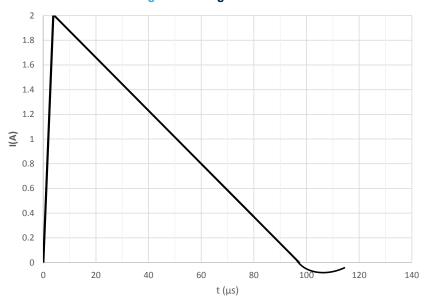

- EMC surge protection 2A/50 μs, (coupling 500 Ω)

- Smart format QFN-20L 4x4 mm package

# **Application**

- Industrial sensors

- · Factory automation

- Process control

# **Description**

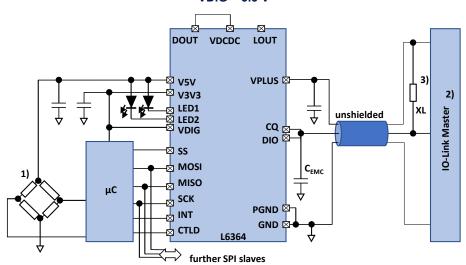

The L6364 is a dual channel transceiver for industrial sensor applications.

It has been designed to support the IO-Link standard and acts as a bridge between a microcontroller with a sensor or actuator function and a 24 V supply and signaling cable.

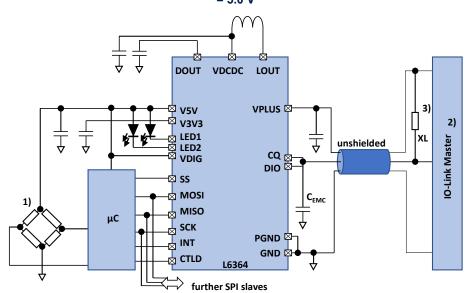

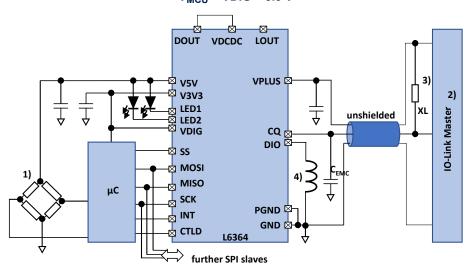

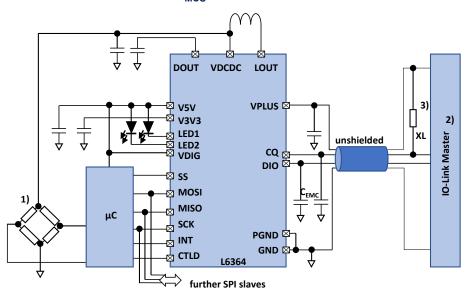

In normal operation the L6364 is configured by the microcontroller via the SPI interface at startup. Typically, the L6364 then operates as a Single Input Output IOLink device driving the output lines as configured by the microcontroller. If the device is connected to an IO-Link master, then the master can initiate communication and exchange data with the microcontroller while the L6364 acts as a physical layer for the communication.

DS13363 - Rev 2 page 2/55

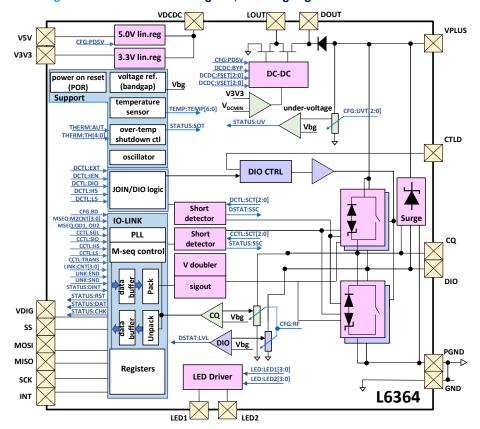

# 1 Block Diagram

VPLUS 5.0V Lin.Reg V5V DC-DC V3V3 3.3V Lin.Reg NC NC PLL Short detectors M-seq control Pack Sigout cq VDIG MOSI MISO PGND Registers **LED Driver** SCK Ţ LED1 LED2

Figure 1. Block Diagram

DS13363 - Rev 2 page 3/55

# 2 Package and pin-out

VDIG CQ CQ DIO NC VDCDC VPLUS

Figure 2. Package and pinout - QFN

PINOUT TOP THROUGH VIEW

N.B. GND exposed pad and GND pin to be shorted on PCB

DS13363 - Rev 2 page 4/55

**Table 1. Pin Description**

| Group/Exposure      | Pin number<br>(QFN) | Name              | Function                                | Type <sup>(1)</sup> |

|---------------------|---------------------|-------------------|-----------------------------------------|---------------------|

|                     | 11                  | V <sub>PLUS</sub> | Line supply voltage                     | PWR                 |

|                     | 14                  | CQ                | Line data signal SIO/SDCI               | ANA IO              |

| Line/External       | 13                  | DIO               | Line data signal DI/DO                  | ANA IO              |

|                     | 15                  | P <sub>GND</sub>  | Switch ground return                    | PWR                 |

|                     | 4, TAB              | GND               | Ground                                  | PWR                 |

|                     | 17                  | MOSI              | SPI data, microcontroller to L6364      | CI                  |

|                     | 19                  | SS                | SPI synchronization, slave select       | CI                  |

|                     | 20                  | SCK               | SPI interface clock signal              | CI                  |

| SPI/Internal/Dig    | 18                  | MISO              | SPI data, L6364 to microcontroller      | COZ                 |

|                     | 16                  | INT               | Interrupt                               | CO                  |

|                     | 1                   | V <sub>DIG</sub>  | SPI interface supply                    | PWR                 |

|                     | 10                  | CTLD              | Direct control of DIO output channel    | CI                  |

| LED/External        | 6                   | LED1              | LED1 source current                     | ANA O               |

| LED/External        | 7                   | LED2              | LED2 source current                     | ANA O               |

| Low voltage supply/ | 3                   | V5V               | Sensor and microcontroller              | PWR                 |

| Internal            | 2                   | V3V3              | supply                                  | PWR                 |

|                     | 9                   | D <sub>OUT</sub>  | VPLUS following diode protections       | ANA IO              |

| DCDC/Internal       | 8                   | L <sub>OUT</sub>  | Inductor power feed                     | ANA IO              |

|                     | 5                   | V <sub>DCDC</sub> | DCDC supply output, intermediate supply | PWR                 |

| Unused/Internal     | 12                  | N/C               | Not connected                           | -                   |

<sup>1.</sup> PWR: power, CI: CMOS input, CO: CMOS output, COZ: output with tristate function, ANA IO: Analogue input output, ANA O: Analogue output.

DS13363 - Rev 2 page 5/55

# 3 Technical Data

# 3.1 Absolute Maximum Ratings

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All voltages are referenced to GND unless otherwise specified.

Table 2. Absolute maximum ratings

| Symbol                                                   | Parameter                                        | Value              | Unit |

|----------------------------------------------------------|--------------------------------------------------|--------------------|------|

| V=                                                       | Supply Voltage (steady-state)                    | - 40 to + 40       | V    |

| V <sub>PLUS</sub>                                        | Supply Voltage (transient)                       | Internally limited | V    |

| V                                                        | HS or LS Output channel voltage (steady-state)   | - 40 to + 40       | V    |

| V <sub>CQ</sub>                                          | HS or LS Output channel voltage (transient )     | Internally limited | V    |

| V <sub>DIO</sub>                                         | DIO channel voltage (steady-state)               | - 40 to + 40       | V    |

| ▼ DIO                                                    | DIO channel voltage (transient)                  | Internally limited | V    |

| V5V                                                      | 5V voltage pin                                   | - 1 to 7           | V    |

| V3V3                                                     | 3.3V voltage pin                                 | - 1 to 5           | V    |

| V <sub>DIG</sub> , V <sub>LED1</sub> , V <sub>LED2</sub> | Digital pins end LED pins                        | - 1 to 7           | V    |

| V <sub>ESD</sub>                                         | Electrostatic protection (HBM)                   | 2                  | kV   |

| P <sub>D</sub>                                           | Power Dissipation                                | Internally limited | W    |

| T <sub>LEAD</sub>                                        | Soldering temp. (20-40sec, cf. JEDEC J-STD-020C) | 260                | °C   |

| T <sub>STOR</sub>                                        | Storage Temperature Range                        | -40 to 150         | °C   |

Operation above the absolute maximum ratings may lead to instantaneous device failure. Operation of the L6364 between the operating ratings and the absolute maximum ratings leads to a reduced operating lifetime.

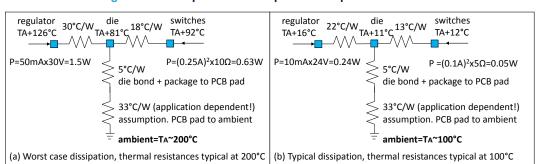

# 3.2 Thermal Characteristics

Table 3. Thermal data

| Symbol              | Parameter                                                                                                                 | Value  |       | Unit  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|

| Symbol              | Falallielei                                                                                                               | QFN20L | CSP19 | Oilit |

|                     | Thermal resistance junction-ambient                                                                                       |        |       |       |

| R <sub>th(JA)</sub> | (FR4, Cu Thick. 35 $\mu$ m, 2 layers, total exposed area = 5 mm <sup>2</sup> ; exposed pad soldered to Cu area with vias) | 54     | 80    | °C/W  |

# 3.3 Recommended operating conditioning

Table 4. Recommended operating conditions

| Symbol                   | Parameter                                                        | Min. | Тур. | Max. | Unit |

|--------------------------|------------------------------------------------------------------|------|------|------|------|

| I <sub>QUIES</sub>       | Operating current supply, no pin currents, DCDC enables          |      | 3.0  | 3.5  | mA   |

| I <sub>QUIES</sub> START | Operating current supply on pin V <sub>PLUS</sub> during startup |      |      | 10   | mA   |

DS13363 - Rev 2 page 6/55

| Symbol                    | Parameter                                                                  | Min. | Тур. | Max. | Unit |

|---------------------------|----------------------------------------------------------------------------|------|------|------|------|

| V <sub>SUP</sub>          | V <sub>PLUS</sub> supply voltage, I <sub>V3v3</sub> =50mA, (DCDC disabled) | 4.5  | 24   | 35   | V    |

| V <sub>SUP</sub>          | V <sub>PLUS</sub> supply voltage, I <sub>V5V0</sub> =50mA, (DCDC disabled) | 6    | 24   | 35   | V    |

| V <sub>SUP</sub>          | Minimum VPLUS (DCDC enabled) (see Figure 12)                               |      | 10.5 |      | V    |

| V <sub>DCDC_5V_MIN</sub>  | Minimum VDCDC output voltage (V <sub>SET</sub> ) for use of V5V            | 6.1  |      |      | V    |

| V <sub>DCDC_3V3_MIN</sub> | Minimum V <sub>3V3</sub> for VDCDC                                         |      | 2.8  |      | V    |

| C <sub>BLK</sub>          | Blocking capacitor on VPLUS                                                | 100  |      |      | nF   |

| C <sub>EMC</sub>          | EMC blocking capacitor                                                     |      | 470  |      | pF   |

| C <sub>V3V3</sub>         | Capacitor C <sub>V3V3</sub>                                                | 1    |      | 10   | μF   |

| C <sub>V5V</sub>          | Capacitor C <sub>V5V</sub> (V5V in use)                                    | 1    |      | 10   | μF   |

| C <sub>DOUT</sub>         | Capacitor C <sub>DOUT</sub>                                                | 10   |      |      | nF   |

| C <sub>DCDC</sub>         | Capacitor C <sub>DCDC</sub>                                                |      | 2.2  |      | uF   |

| L <sub>DCDC</sub>         | Inductor L <sub>DCDC</sub>                                                 |      | 220  |      | uH   |

| C <sub>QLOAD_MAX</sub>    | Maximum load capacitor CQ (see Figure 20) <sup>(1)</sup>                   |      |      | 250  | nF   |

| C <sub>DIOLOAD_MAX</sub>  | Maximum load capacitor DIO (see Figure 20) (1)                             |      |      | 250  | nF   |

| C <sub>JOINLOAD_MAX</sub> | Maximum load capacitor JOIN mode (see Figure 21) (1)                       |      |      | 500  | nF   |

| L <sub>CQLOAD_MAX</sub>   | Maximum load inductance CQ (see Figure 20)                                 |      |      | (2)  | mH   |

| L <sub>DIOLOAD_MAX</sub>  | Maximum load inductance DIO (see Figure 20)                                |      |      | (2)  | mH   |

| L <sub>JOINLOAD_MAX</sub> | Maximum load inductance JOIN mode (see Figure 21)                          |      |      | (2)  | mH   |

<sup>1.</sup> values measured with pure capacitive load.

# 3.4 Electrical Characteristics

Electrical parameters are valid over the operating temperature and voltage range, unless otherwise stated.

Table 5. Receiver CQ/DIO

| Symbol            | Parameter           | Test Conditions                                               | Min. | Тур.                         | Max.                      | Unit  |

|-------------------|---------------------|---------------------------------------------------------------|------|------------------------------|---------------------------|-------|

| V <sub>THH</sub>  | Input threshold "H" | RF bit = 0 in CFG register (see                               | 10.5 |                              | 13                        | V     |

| V <sub>THL</sub>  | Input threshold "L" | Figure 17 and<br>Figure 18 Register<br>map).                  | 8    |                              | 11.5                      | V     |

| V <sub>THHR</sub> | Input threshold "H" | RF bit = 1 in CFG                                             | -10% | (V <sub>PLUS</sub> /1.8)-0.5 | +10%                      | V     |

| V <sub>THLR</sub> | Input threshold "L" | register (see<br>Figure 17 and<br>Figure 18 Register<br>map). | -10% | (V <sub>PLUS</sub> /1.8)+0.5 | +10%                      | V     |

| V <sub>HYS</sub>  | Hysteresis          |                                                               | 0.5  | 1                            | 1.5                       | V     |

| V <sub>IN</sub>   | Input range CQ/DIO  |                                                               |      |                              | 35, V <sub>PLUS</sub> +10 | V     |

| f <sub>BIT</sub>  | Data rate           | BD=0                                                          |      | 38.4                         |                           | kBaud |

| f <sub>BIT</sub>  | Data rate           | BD=1                                                          |      | 230.4                        |                           | kBaud |

| T <sub>BIT</sub>  | Bit time            |                                                               |      | 1/f <sub>BIT</sub>           |                           | μs    |

| f <sub>CK</sub>   | Internal clock base |                                                               | -10% | 10                           | +10%                      | MHz   |

DS13363 - Rev 2 page 7/55

<sup>2.</sup> unlimited, see Section 18 for further details.

# Table 6. Short-circuit and Wake-up detection

| Symbol               | Parameter                  | Test Conditions | Min. | Тур.             | Max. | Unit |

|----------------------|----------------------------|-----------------|------|------------------|------|------|

| I <sub>SHORT</sub>   | Set current tolerance      | See Table 28    | -20% | I <sub>SET</sub> | +20% | mA   |

| t <sub>SHORT</sub>   | Filter delay               |                 | -10% | 14               | +10% | μs   |

| N <sub>RETRY</sub>   | Retries                    | SIO=1           |      | 2                |      |      |

| t <sub>RETRY</sub>   | Retry delay                | SIO=1           | -10% | 50               | +10% | μs   |

| t <sub>RESTART</sub> | Short-circuit restart time | SIO=1           | -10% | 100              | +10% | ms   |

### Table 7. POR (Power On Reset)

| Symbol            | Parameter             | Test Conditions | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------|-----------------|------|------|------|------|

| V <sub>POR</sub>  | POR release threshold |                 | 1.6  | 2    | 2.5  | V    |

| V <sub>HYST</sub> | POR hysteresis        |                 |      | 0.1  |      | V    |

# Table 8. Output switches individual channels CQ/DIO

| Symbol           | Parameter         | Test Conditions         | Min. | Тур. | Max. | Unit |

|------------------|-------------------|-------------------------|------|------|------|------|

| R <sub>SW</sub>  | Output resistance | I <sub>OUT</sub> =100mA |      | 5    | 10   | Ω    |

| V                | ZEN Zener voltage | I <sub>OUT</sub> =10mA  | 6    |      | 10   | V    |

| V ZEN            |                   | I <sub>OUT</sub> =100mA |      | 8    |      | V    |

| I <sub>SAT</sub> | Saturated current |                         |      | 1.2  |      | Α    |

# Table 9. Line surge protection, parameters with respect to any pair PGND, CQ, DIO, VPLUS

| Symbol                    | Parameter                           | Test Condition            | Min. | Тур. | Max. | Unit |

|---------------------------|-------------------------------------|---------------------------|------|------|------|------|

| V <sub>SURGE(CLAMP)</sub> | Voltage clamps protection threshold | abosorbed current < 40 uA | 35   | 40   | 45   | V    |

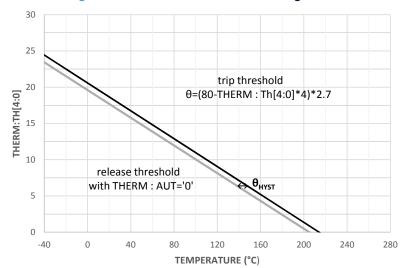

#### Table 10. Thermal shutdown

| Symbol            | Parameter            | Test Condition | Min. | Тур. | Max. | Unit |

|-------------------|----------------------|----------------|------|------|------|------|

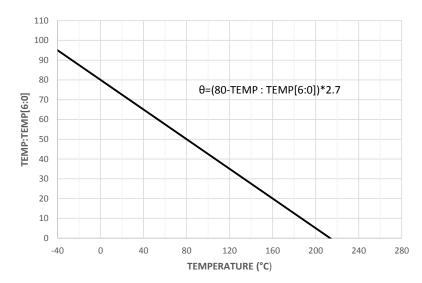

| εΤ                | Temperature accuracy | 150°C          | -10  |      | 10   | °C   |

| εΤ                | Temperature accuracy | 30°C           | -5   |      | 5    | °C   |

| O <sub>HYST</sub> | Thermal hysteresis   |                |      | 10   |      | °C   |

# Table 11. Digital pins

| Symbol    | Parameter                    | Test Condition | Min.                 | Тур. | Max.                  | Unit |

|-----------|------------------------------|----------------|----------------------|------|-----------------------|------|

| $V_{DIG}$ | Voltage drop on digital pins | I = -4 mA      |                      |      | 0.5                   | V    |

| $V_{DL}$  | Input low signal             |                |                      |      | 0.15 V <sub>DIG</sub> | V    |

| $V_{DH}$  | Input high signal            |                | 0.5 V <sub>DIG</sub> |      |                       | V    |

DS13363 - Rev 2 page 8/55

| Symbol          | Parameter            | Test Condition | Min. | Тур. | Max. | Unit |

|-----------------|----------------------|----------------|------|------|------|------|

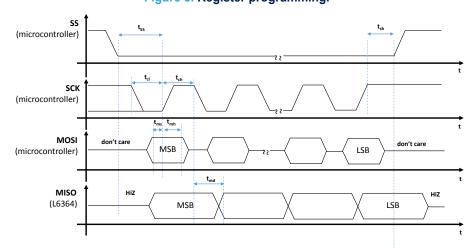

| t <sub>cl</sub> | Clock low phase      | SCK            | 50   |      |      | ns   |

| t <sub>ch</sub> | Clock high phase     | SCK            | 50   |      |      | ns   |

| t <sub>ms</sub> | Setup wrt. SCK       | MOSI           | 10   |      |      | ns   |

| t <sub>mh</sub> | Hold wrt. SCK        | MOSI           | 10   |      |      | ns   |

| t <sub>ss</sub> | Setup wrt. SCK       | SS             | 10   |      |      | ns   |

| t <sub>sh</sub> | Hold wrt. SCK        | SS             | 10   |      |      | ns   |

| t <sub>md</sub> | Output availability  | MISO           |      | 18   | 40   | ns   |

| R <sub>PU</sub> | Pull-up resistance   | SS, SCK, MOSI  | 50   |      | 200  | kΩ   |

| R <sub>PD</sub> | Pull-down resistance | CTLD           | 50   |      | 200  | kΩ   |

**Table 12. LED Driver**

| Symbol           | Parameter                             | Test Condition | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------------|----------------|------|------|------|------|

| I <sub>LED</sub> | Sink current base unit <sup>(1)</sup> | See Figure 10  | -10% | 0.5  | +10% | mA   |

<sup>1.</sup> The current supplied by each LED pin can be configured between 0 to 8 mA by LED1[3:0] and LED2[3:0] of LED register (address 0x07). One bit increment of LEDx[3:0] corresponds to +0.5 mA(typ).

**Table 13. Linear regulators**

| Symbol                 | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Test Condition                        | Min.                   | Тур.              | Max.                   | Unit |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------|-------------------|------------------------|------|

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DCDC</sub> =35 V,              |                        |                   |                        |      |

| I <sub>PLUSREV</sub>   | Power fail reverse leak                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>DCDC</sub> =D <sub>OUT</sub> , |                        |                   | 10                     | μA   |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>PLUS</sub> = GND               |                        |                   |                        |      |

| I <sub>OUT</sub>       | Regulator output capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V3V3 or V5V                           | 50                     |                   |                        | mA   |

| R <sub>START_MIN</sub> | Startup static capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       | 67                     |                   |                        | Ω    |

| V <sub>V3V3</sub>      | Regulator output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V3V3 0 mA <i<sub>OUT&lt;50 mA</i<sub> | 3.0                    | 3.3               | 3.6                    | V    |

| V <sub>V5V</sub>       | Regulator output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V5V 0 mA <i<sub>OUT&lt;50 mA</i<sub>  | 4.5                    | 5.0               | 5.5                    | V    |

| I <sub>PD5V</sub>      | Pull-down current of V5V pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       | 50                     | 100               | 200                    | μA   |

| \/                     | I lo do o o la constanta de la | see Table 29, V <sub>UV</sub> <10V    | UV <sub>SET</sub> -1   | UV <sub>SET</sub> | UV <sub>SET</sub> +1   | V    |

| V <sub>UV</sub>        | Undervoltage detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>UV</sub> ≥10V                  | UV <sub>SET</sub> -10% | UV <sub>SET</sub> | UV <sub>SET</sub> +10% | V    |

Table 14. DC-DC supply

| Symbol               | Parameter                  | Test Condition                                                                                           | Min. | Тур.                 | Max. | Unit |

|----------------------|----------------------------|----------------------------------------------------------------------------------------------------------|------|----------------------|------|------|

| V <sub>PLUS</sub>    | Supply voltage             | V <sub>PLUS</sub> > DC-DC target<br>Output (see<br>Table 31. DC-DC<br>output voltage, V <sub>SET</sub> ) |      |                      | 35   | V    |

| I <sub>OUT</sub>     | DC-DC Output current       |                                                                                                          | 50   |                      |      | mA   |

| V <sub>SET_TOL</sub> | V <sub>SET</sub> tolerance | see Table 31. DC-DC output voltage, V <sub>SET</sub>                                                     | -10% | V <sub>SET_NOM</sub> | +10% | V    |

DS13363 - Rev 2 page 9/55

| Symbol                  | Parameter                      | Test Condition                                               | Min.                    | Тур.             | Max.                    | Unit |

|-------------------------|--------------------------------|--------------------------------------------------------------|-------------------------|------------------|-------------------------|------|

| t <sub>VSET</sub>       | V <sub>SET</sub> step size     |                                                              |                         | 52               |                         | μs   |

| $\Delta t_{VSET}$       | V <sub>SET</sub> range delay   | V <sub>SET_MIN</sub>                                         | 7*t <sub>VSET_MIN</sub> |                  | 7*t <sub>VSET_MAX</sub> | μs   |

| R <sub>DCDC</sub>       | Output voltage load regulation | 0-50mA                                                       |                         |                  | 2                       | Ω    |

| I <sub>STARTUP</sub>    | Startup current                | urrent From pin V <sub>PLUS</sub> , See Section 16.3.1 50 80 |                         | 140              | mA                      |      |

| V <sub>STARTUP</sub>    | Startup voltage                | On pin V <sub>DCDC</sub> , See<br>Section 16.3.1             | 7.5                     | 8.0              | 8.5                     | V    |

| V <sub>VPLUSDCMIN</sub> | DC-DC operation start          |                                                              | 7.0                     | 8.0              | 9.0                     | V    |

| f <sub>DCDC</sub>       | Operating frequency            | see Table 30                                                 | -10%                    | f <sub>SET</sub> | +10%                    | kHz  |

| R <sub>HIGH</sub>       | High side resistance           |                                                              | 3.3                     | 6.6              | 20                      | Ω    |

| R <sub>LOW</sub>        | Low side resistance            |                                                              | 4.5                     | 7.2              | 20                      | Ω    |

| I <sub>LIMIT</sub>      | I <sub>LIMIT</sub> in inductor |                                                              | 70                      |                  | 90                      | mA   |

| R <sub>SHUNT</sub>      | Sense resistance               |                                                              | 0.6                     | 1                | 1.5                     | Ω    |

DS13363 - Rev 2 page 10/55

# 4 Startup

At startup, power is applied via the cable on V<sub>PLUS</sub>. The embedded Power-On-Reset (POR) circuit ensures the proper startup of the L6364 with the output switches initially in a high impedance state. The device core of the L6364, including the control for the 5 V regulator, is supplied by the V3V3 supply.

The SPI communication logic is reset whenever SS='1' and is independent of the L6364 power on reset itself. It is therefore possible to read the SPI register values even when the L6364 is in reset. In particular, the STATUS:RST bit is read as part of the STATUS byte on every SPI access.

This bit is cleared when the device is in reset, or when the device has been reset. This status information can be used as set out in Table 15 to determine the L6364 reset state, and also to react to unexpected reset conditions.

Device state STATUS:RST INT Comment L6364 is in power on reset (checked at the start of the SPI Power-On-Reset (POR) 0 0 access). Only the STATUS:RST bit is valid. The microcontroller may wait for a high level on INT before proceeding. L6364 has been reset, and the INT line is forced high. Write Device reset (post POR) 0 1 STATUS:RST='1' to allow normal operation of the L6364. Χ Operation 1 Normal operation

Table 15. L6364 Reset conditions

The microcontroller should initialize the state of the internal registers to the desired values after reset.

DS13363 - Rev 2 page 11/55

## 5 SPI Communication

Internal registers (see Figure 17 and Figure 18 Register map) are provided to observe and control the L6364 state.

These register settings are read and written via the SPI interface, where the L6364 is the SPI slave. The operating voltage level for inputs and outputs on the SPI interface is set by the VDIG pin. This pin is typically be directly connected either to the V5V or V3V3 supplies.

The detailed timing diagram is shown in Figure 3 Data is shifted into an internal shift register from input MOSI on each rising SCK edge. Data is made available on pin MISO at each falling SCK edge. Note that the MISO line is only driven when the slave specific select line is SS='0', which allows other SPI slaves to share the same SPI bus.

The MSB of the address byte is a WR/RDn bit, where a '1' indicates that each byte is written to the registers. Valid data is always made available on the MISO line independent of the WR/RDn bit.

Where a register is written and read in the same operation, then the read value is the old register value. During read operations, the level of the MOSI line is ignored for the data bytes.

The byte sequence for data transmission is shown in Figure 4 Each transmission sequence consists of a falling SS edge which synchronizes transmission, followed by a target register address byte.

During the transmission of the address byte from the microcontroller to the L6364, the status register contents are sent from the L6364 to the microcontroller.

Figure 3. Register programming.

## 5.1 Multiple byte exchange

Multiple registers at consecutive addresses can be read or written by extending the access as shown in Figure 4; bytes are written on the rising SCK clock edge of the eighth bit of each byte.

With the WR/RDn bit set, a simultaneous read/write operation is started. Now, with a multiple byte exchange, it is possible to both read and write the values of multiple register bytes in one operation.

This is particularly useful with larger M-sequence types where there is limited time available for the SPI exchange.

DS13363 - Rev 2 page 12/55

Figure 4. Single byte and sequential byte accesses

Consecutive access

MOSI: A DN DN+1 DN+2 DN+3 ...

MISO: S DN DN+1 DN+2 DN+3 ...

Single access

MOSI: A D

MISO: S D

MISO: S D

KEY: A: Address byte, D: Data byte, S: Status byte

DS13363 - Rev 2 page 13/55

# 6 DIO pin

The DIO pin is a fully protected I/O which is driven or sampled independently via SPI. This pin may be operated in one of two modes:

- DIO mode: If the DCTL:DIO bit is set, then the DIO Line functions as a digital input output pin, which is independently driven according to the setting of the LS and HS bits in the DCTL register. Setting bit DCTL:IEN in this mode, enables a signal level change interrupt, informing the microcontroller that a level change has occurred on the DIO line.

- JOIN mode: If the DCTL:DIO bit is cleared, then the DIO/CQ outputs function together to provide a single, double drive strength, IO-Link conformal output. The outputs, DIO and CQ, must be externally shorted together. When in this mode, the DCTL:HS and DCTL:LS no longer have any effect on the output state.

# 6.1 DIO mode output control

In DIO mode there are two alternatives for controlling the pin output state: via SPI (DCTL:EXT reset) or directly via pin CTLD (DCTL:EXT set). Table 16 and s Table 17 show how the output is controlled in both cases respectively.

| Mode    | DCTL:HS | DCTL:LS | DIO Channel Output State |

|---------|---------|---------|--------------------------|

| Off     | 0       | 0       | HiZ                      |

| Low     | 0       | 1       | 0                        |

| High    | 1       | 0       | 1                        |

| Illegal | 1       | 1       | HiZ                      |

Table 16, DIO control via SPI-DCTL:EXT='0'

If bit DCTL:EXT is set, bits DCTL:HS and DCTL:LS function as configuration bits, which configure the DIO output to be a PNP, NPN or Push-Pull driver.

|           |         |         | DIO Channel | Output State |

|-----------|---------|---------|-------------|--------------|

| Mode      | DCTL:HS | DCTL:LS | CTLD='1'    | CTLD='0'     |

| Inactive  | 0       | 0       | HiZ         | HiZ          |

| NPN       | 0       | 1       | 0           | HiZ          |

| PNP       | 1       | 0       | 1           | HiZ          |

| Push-Pull | 1       | 1       | 1           | 0            |

Table 17. Direct DIO control via pin CTLD - DCTL:EXT='1'

The high- and low-side switches are identical and have an on-state resistance of  $R_{SW.}$  Any inactive switch acts as a Zener diode limiting the voltage on the DIO line to  $V_{ZEN}$  above  $V_{PLUS}$  (high-side switch), or  $V_{ZEN}$  below GND (low-side switch). This allows rapid switch-off for inductive loads.

The DIO data level is monitored for signals, filtering out pulses with a duration of less than  $(1/16) * T_{BIT}$ , see Table 5.

The decision threshold for the DIO data level is determined by the CFG:RF bit. Where this is '0', the IO-link standard absolute levels are used, and where the bit is '1' the threshold is referred to  $V_{PLUS}$ /1.8.

DS13363 - Rev 2 page 14/55

# 6.2 SIO mode control

In the SIOActive state, the high-side or low-side switches are switched according to the CCTL:HS and CCTL:LS bits. It is not legal to switch on both simultaneously, and this register setting disables both switches.

The high-side and low-side switches are identical, and have an on-state resistance of R<sub>SW</sub>.

Any inactive switch acts as a Zener diode limiting the voltage on the CQ line to  $V_{ZEN}$  above  $V_{PLUS}$  (high-side switch), or  $V_{ZEN}$  below GND (low-side switch). This allows rapid switch-off for inductive loads.

DS13363 - Rev 2 page 15/55

# 7 IO-Link UART peripheral

The L6364 contains an IO-Link UART peripheral for bidirectional communication according to the IO-Link Standard.

The peripheral is controlled, and data is exchanged, via SPI register accesses. In an application where pins CQ and DIO are coupled together i.e. JOIN mode, then a reference to CQ in the following refers to the shorted pair.

#### 7.1 Multi-octet mode

#### 7.1.1 SIO Mode

Figure 5 shows the IO-Link UART peripheral state machine. When the CCTL:SIO bit is set, the L6364 is set to Single Input Output mode. In this mode the L6364 has the following states:

• SIOActive: The CQ line is driven according to the setting of the HS and LS bits of CCTL register.

The internal UART does not run in this state and so master messages are only detected if a wake-up request from the master is received, which switches the L6364 to the SIOListen state. If the output is set to high impedance (CCTL:HS=LS='0'), then the L6364 can not receive a wake-up request from the master. It is therefore necessary to switch to IO-Link mode (CCTL:SIO='0') if communication detection is required with a high impedance output.

SIOListen: The L6364 has experienced a short-circuit via a wake-up request from the master.

Both high-side and low-side switches are off, and the restart timer is running. Transitions on the CQ line are read as data, and stored in the data buffer (FR0 to FR14 registers). If a complete, valid, master message is received, then the state changes to Transmit, an interrupt is generated and the restart timer is reset. If the timer expires, then the L6364 returns to the SIOActive state and the CQ line is driven again after the transmission.

#### 7.1.2 IO-Link mode

At startup, and if the SIO bit is cleared, the L6364 enters IO-Link mode. In this mode the L6364 has the following states:

• **IOListen**: Transitions on the CQ line are read as data, and stored in the data buffers. Once a complete master message has been read, or an error is experienced in reception (e.g. bad parity, checksum or timeout), then the state changes to Transmit.

#### 7.1.3 Transmit mode

Following reception of an IO-Link master message the L6364 enters the following state:

Transmit: The L6364 is waiting on data from the microcontroller, or is in the process of transmitting data on the CQ channel. The L6364 reverts to IOListen or SIOActive on completion of the transmission, or if an abort is generated by the microcontroller by setting END bit in the LINK register.

If the L6364 has entered Transmit from an SIO mode, the microcontroller would normally now set the L6364 to IO-Link mode, such that the L6364 continues to listen for further information from the master.

If the L6364 experiences a short-circuit during Transmit, then the STATUS:SSC bit is set, and the L6364 returns to either IOListen or SIOListen.

DS13363 - Rev 2 page 16/55

#### IO-Link UART peripheral (Multi-octet mode) state machine 7.1.4

Transmission

aborted by

writing a

LINK:END

command

Initialization IO-Link mode **IOListen** +do : transitions on the CQ line are read as data and stored in the data buffer Notes : Transmission complete, short detected Master message read during transmission or aborted by writing a or error in reception LINK:END command [previous state was IO-Link mode] Transmit mode Transmit **IO-LINK** mode set by the Notes :waiting for data from microcontroller microcontroller or in the process of transmitting data on the CQ channel Valid master SIO mode message complete, short detected during **SIOListen** transmission or +entry : start restart timer (trestart) +entry : HS,LS switches are off : transitions on the CQ line are read +do as data, and stored in the data buffer [previous state Notes: the L6364 has received a short was SIO mode] circuit via a wake-up request from the master trestart Short circuit/ elapsed Wake-up **SIOActive** Notes : the CQ line is driven according to the setting of the CCTL:HS and CCTL:LS bits

Figure 5. IO-Link UART peripheral state machine

#### 7.1.5 Interrupt handling

The L6364 signals an event to the microcontroller using the INT pin, which is intended to be configured as a level sensitive interrupt.

DS13363 - Rev 2 page 17/55

#### 7.1.6 Data interrupt handling

If the STATUS:DAT bit is read as active (high) on an SPI access, then the L6364 is halted in a WAIT condition and is waiting for either a LINK:END or LINK:SND command from the microcontroller.

While the L6364 is in the WAIT condition the interrupt pin (INT), the STATUS:INT bit and the STATUS:DAT bit remain active continuously.

Data can be read and written to the L6364 registers while in the WAIT condition.

Typically the LINK register and FR registers are accessed to read the incoming data, and the FR registers are written to set up the outgoing data. As the L6364 is halted, it doesn't generate further data interrupts in the WAIT condition.

When the microcontroller sends either a LINK:END or LINK:SND command, the interrupt pin (INT), the STATUS:INT bit and the data bit, STATUS:DAT, are cleared within 220 ns of the last SCK edge of the SPI write access.

If the microcontroller detects an active interrupt after the SPI access, or if the STATUS:DAT bit is read as active (high) on a subsequent SPI access, then new data is available.

The LINK register is duplicated as LINK2 at address 0xF to optimize sequential SPI access:

- a sequential SPI read can be used to read the LINK2 register and then the frame registers in one SPI

operation.

- a sequential SPI write (including SND bit) can be used to write the LINK2 register and then the frame

registers. Transmission starts once the FR0 register is written and the micro-controller must ensure that the

subsequent registers have valid values before the start of transmission of the respective octets.

#### 7.1.7 Short-circuit, overtemperature and undervoltage interrupt handling

The INT pin and the STATUS:INT bit are additionally active (high) if the last value of the short-circuit, undervoltage or overtemperature status bits communicated on the SPI is different to the current value.

The L6364 handles short-circuit and overtemperature autonomously and does not require a reaction from the microcontroller.

It is possible for these status bits to change at any time, and so the interrupt may be removed between entering the interrupt service routine and reading the status on the SPI.

The interrupt is removed during the next SPI access to the L6364. If an SPI access is made without checking the value of these bits, as is typical during processing of a data interrupt, it is normal to record the status values from the final access, or to explicitly add an extra SPI access.

#### 7.1.8 Interrupt handler structure

The interrupt handler will typically have the following sequence:

read the L6364 status with a read access from the LINK register if (STATUS:DAT is active) *t*

analyze the STATUS:CHK bit, read the FR registers and write an appropriate response into the FR registers send LINK2:SND or LINK2:END as appropriate and write the response into the FR registers

update the microcontrollers copy of the short-circuit, undervoltage and overtemperature status based on the status bits received in the previous access. Take action if necessary.

#### 7.1.9 Changing to and from SIO mode

The L6364 should be placed into IO-Link mode as soon as communication with the master is established. Typically a switch from SIO mode (CCTL:SIO='1') to IO-Link mode (CCTL:SIO='0') is made during the WAIT condition when a valid message is detected from the master.

A switch from IO-Link mode to SIO mode is typically made shortly after the device response for the FALLBACK command has been sent. The switches themselves are, however, only activated by the microcontroller after the period defined in the IO-Link specification.

The L6364 may be switched from SIO mode to IO-Link mode at any time without disturbing data reception or transmission. A switch from IO-Link mode to SIO mode may disturb data reception if a master is in the process of transmitting, and the UART is therefore reset if this occurs.

DS13363 - Rev 2 page 18/55

#### 7.1.10 SPI register writes outside interrupt service routines

The interrupt service routine typically accesses the SPI, and so it is necessary to avoid a collision between an interrupt service routine SPI access and any other SPI access made from the microcontroller.

Accessing the SPI clears a short-circuit or overtemperature interrupt, and so the received value of these bits must be recorded by the microcontroller.

If a function makes a number of sequential SPI accesses, then it is reasonable to ignore these status bits on all but the last access, and record the values read on this last access.

It is not necessary to check the STATUS:DAT bit outside the interrupt service routine, since the data interrupt remains active until the microcontroller responds.

# 7.2 Single octet UART mode

The L6364 supports an operating mode called Single octet UART mode, which performs a simplified data transfer function, transferring one octet at a time in either direction.

In this mode, M-sequence type recognition (MSEQ:M2CNT), the number of on-demand data octets (MSEQ:OD1, MSEQ:OD2) and checksum verification/generation are disabled and, therefore, must be realized by the microcontroller.

Note, that an exchange is always triggered by the master. It is not possible to transmit data without first receiving valid data. Figure 6 shows the single octet UART mode state machine. When the CCTL:SGL bit is set by the microcontroller, the L6364 is set to single octet UART mode.

#### 7.2.1 Buffering

The FR0 register and the L6364 UART internal register together provide double buffering of data in receive and single buffering in transmit. In order to avoid buffer over- or under-runs it is necessary for the microcontroller to:

- read FR0 before the UART writes a new octet in Receive mode (delay ca. 11xT<sub>BIT</sub>), or

- write FR0 before the UART requires a new octet in Transmit mode (delay ca. 3xT<sub>BIT</sub>).

#### 7.2.2 Receive mode

In Receive mode the L6364 has the following states:

Receive wait: The L6364 has received a complete master octet via the CQ channel. A data interrupt is generated (STATUS:DAT='1') and the received octet is placed in the FR0 register.

The microcontroller has access to the FR0 register and reads the received octet. The state changes to Receive Interim

The L6364 is now waiting for a response from the microcontroller, which either writes LINK:END to continue receiving, or FR0 to initiate sending. (A LINK:END should not be sent after receiving the last octet.) The UART continues to run in this state receiving the following frame. A buffer over-run results if the microcontroller does not read FR0 before the frame completes.

A UART frame is 11 bits, which at 230.4kBaud gives a period of 47µs for the two SPI accesses, each of 16 bits. At 4 MHz SPI this corresponds to an SPI delay of 4 µs.

Error conditions: parity error, stop bit, time-out (more than 4xT<sub>BIT</sub> waiting for the next UART frame on the CQ line), or buffer under-run are signaled with a data interrupt (STATUS:DAT='1') with additionally STATUS:CHK='1'.

The microcontroller should respond by writing LINK:END and discarding any received octets. The master stops sending after the last master octet and so a time-out is generally detected by the L6364 in the delay while the microcontroller is preparing the response.

The condition is held internally in the L6364 and discarded by the L6364 when FR0 is written by the microcontroller, initiating transmission. The timeout is therefore not reported to the microcontroller in this case

• Receive interim: The UART receives data on the CQ line and copies this to the FR0 register, switching to Receive wait on completion.

Once the expected number of octets is received, the microcontroller initiates sending by writing the first octet in the response M-sequence to FR0, thereby switching the L6364 to Transmit mode (see Section 7.2.3 ). (In single octet UART mode the equivalent of a LINK:SND command is achieved by writing to FR0).

DS13363 - Rev 2 page 19/55

In SIOListen mode a received UART frame is only reported if the parity and stop bits are correct. The microcontroller must switch from SIO mode to IO-Link mode after reception of a valid UART frame before responding with LINK:END, otherwise the L6364 returns to SIO mode conflicting with the further master transmission.

#### 7.2.3 Transmit mode

Transmit mode is entered when the microcontroller writes FR0 while the L6364 is in the Receive wait state.

The UART reads this value from the FR0 register, emptying the buffer, and starts transmitting. The L6364 enters the Transmit wait state.

The L6364 provides a single octet data buffer and requests further data whenever this buffer is empty, including during the transmission of the previous octet. It is only necessary to ensure that this buffer is refilled before the UART needs to send the next octet.

The maximum allowed time between the starts of two subsequent frames on IO-Link is 11  $T_{BIT}$  frame + 3  $T_{BIT}$  pause = 14  $T_{BIT}$ , which at 230.4kBaud gives a period of 60  $\mu$ s for the 16 bit SPI access. At 4 MHz SPI this corresponds to an SPI delay of 4  $\mu$ s.

In Transmit mode the L6364 has the following states:

- Transmit wait: The L6364 requests a new octet by sending a data interrupt (STATUS:DAT='1').

- The L6364 is waiting for a response from the microcontroller, which either writes FR0 with a new octet to continue transmission, or LINK:END to terminate transmission.

- Transmitting (buffer empty): The UART sends the current octet.

- A further response is requested from the microcontroller, by sending a data interrupt (STATUS:DAT='1'). If the microcontroller provides a further octet, this is placed in the buffer and the state changes to Transmitting (buffer full), if the microcontroller writes LINK:END, then the state changes to Transmitting (terminating).

- If the microcontroller does not provide an octet before the UART transmission completes, then the state changes to Transmit wait.

- Transmitting (buffer full): The UART sends the current octet. On completion, it sources the next octet from the buffer, and the state changes to Transmitting (buffer empty).

- Transmitting (terminating): The UART sends the current octet. On completion, the PHY returns to idle.

#### 7.2.4 Timing errors in transmit

The microcontroller can cause a timing error in Transmit mode if the delay in response is too long. These errors are not monitored by the L6364. A minimum inter-frame time delay of 1xT<sub>BIT</sub> is, however, guaranteed by the L6364.

#### 7.2.5 Error condition in transmit

Error conditions are reported to the microcontroller as either short-circuit (STATUS:SSC='1', reported following a delay of t<sub>RETRY</sub>), or overtemperature (STATUS:SOT='1').

The conditions are handled autonomously by the L6364 and no intervention by the microcontroller is necessary. The normal data flow is preserved and the L6364 requests further octets from the microcontroller as if the error were not present.

These octets are silently dropped and no attempt is made to transmit them. Under error conditions, then transmission may be terminated by the microcontroller using LINK:END='1'.

DS13363 - Rev 2 page 20/55

#### 7.2.6 Single octet UART mode state machine

SIOActive Hotes : the CQ line is driven acco to the setting of the CCTL:HS and CTL:LS bits IO-Link mode set by Initialization CCTL:SGL='1' Short circuit/ IO-Link mode Wake-up IOI ister SIOListen do : UART in reads data on CQ ine, copies result to FR0 Parity error, stop error, timeout or buffer over-rur signaled with CHK='1'. Microcontroller responds w LINK:END and discards received octets octet received octet received Receive mode octet rc Transmitting (buffer full) Transmitting Transmitting wait +do : UART reads data in on CQ line and copies resul to FR0 Notes : : set data interrupt (STATUS:DAT='1') : UART reads data in on CQ line (buffer empty) : UART sends IIΔRT +entry : set data interrupt (STATUS:DAT='1' +do : UART waits Notes: waiting for response from microcont either read from or write to FRO. Notes : waiting for response from microcontroller, either write to FRO or LINK:END Notes : waiting for response from microcontroller, either write to FRO or LINK:END Transmitting FRO written (terminating) : UART sends FR0 END END written

Figure 6. Single octet UART mode state diagram

#### 7.2.7 Synchronization in single octet UART mode

The L6364 uses a PLL (phase-locked loop) to continuously lock the UART receive and transmit frequency to the master frequency.

A few octet values (00h, 80h, e0h, f8h and feh) do not provide information which can be used to correct the PLL frequency, and a continuous sequence of these values could prevent the PLL performing frequency tracking for some time.

In IO-Link operation, however, it is not possible to create such M-sequences as the defined format of the M-sequence, and in particular the checksum, guards against this.

A continuous sequence of these octets is possible when the single octet UART mode is used in a proprietary mode, eg. for code download.

In this case, the insertion of a synchronization octet (aa<sub>h</sub>) at least every 75 ms is required, taking into account a worst case dissipation change (1W) in combination with a worst case oscillator temperature drift. The interval of 75 ms is equivalent to 240 octets at 38.4kBaud assuming an inter-frame delay of 1 bit. We recommend the insertion of a synchronization octet every 32 octets.

### 7.3 Transparent mode

The L6364 supports an operating mode for transparent communication of UART frames.

In this mode, the frames are received and transmitted from a UART peripheral in the microcontroller, and the function of the DUAL PHY device is reduced to that of a physical level converter.

This mode is supported by dual use of the MOSI and MISO pins, maintaining the low overall pin-count and a restricted use of microcontroller resources.

Transparent mode is entered by setting the CCTL:TRNS register bit to '1' via the SPI. In this mode the IO-Link state machine in the L6364 and the PLL are placed in reset.

The interrupt line and status monitoring for reset, short-circuit, overtemperature and undervoltage events continue to function.

DS13363 - Rev 2 page 21/55

# 7.3.1 Pin functions in transparent mode

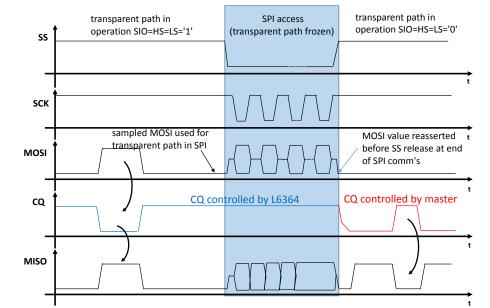

In transparent mode, the MOSI and MISO pins are used for both SPI communication, and for the transparent path. The SS pin controls the use of the MOSI and MISO pins, according to Table 18.

SPI comm's

Transparent path

MOSI

MISO

SS='0'

SPI comm's active

CQ output switch control frozen

SPI data in

SPI data out

SS='1'

SPI comm's frozen

Transparent path active

CQ output switch control

Filtered CQ line level

Table 18. Pin dual use in transparent mode

An SPI communication in transparent mode is shown in Figure 7. Initially the L6364 is driving the CQ line; an SPI exchange is then conducted in which the L6364 is instructed to stop driving the line, and finally the IO-Link master drives the CQ line.

Typically the microcontroller SPI access routine records the MOSI level in use before setting SS='0' to start an SPI access, and assert this value again on the MOSI line before setting SS='1'.

The microcontroller should preset the MOSI pin to the required level before the first SPI access enabling transparent mode.

Support for this may, however, be automatic depending on the microcontroller.

The SPI connection to the L6364 is not suitable for a bus connection of multiple SPI slaves in transparent mode as the MOSI line is permanently driven.

Figure 7. Illustration of operation in transparent mode

# 7.4 Transparent mode output path

With SS='1', the level of the MOSI pin controls the output switches according to the SIO, HS and LS bit settings as shown in Table 19. Where SS='0' for SPI access the level latched on the MOSI line is frozen, and used in the place of the MOSI line itself.

The CCTL:HS and CCTL:LS bits function as enables for the high-side and low-side switches respectively, and select operation as a high-side, low-side or push-pull device.

Note that the logical path from MOSI to CQ is inverting.

DS13363 - Rev 2 page 22/55

Table 19. Transparent mode operation

| CCTL:SIO | CCTL:HS | CCTL:LS | Operation                   | Short-circuit              |

|----------|---------|---------|-----------------------------|----------------------------|

| 1        | 0       | 0       | SIOListen operation         |                            |

| 1        | 0       | 1       | Low-side SIO operation      | Short reported after retry |

| 1        | 1       | 0       | High-side SIO operation     | Short reported after retry |

| 1        | 1       | 1       | Push-pull SIO operation     |                            |

| 0        | 0       | 0       | IOListen operation          | Short timers reset         |

| 0        | 0       | 1       | Do not use                  |                            |

| 0        | 1       | 0       | Do not use                  |                            |

| 0        | 1       | 1       | Push-pull IO-Link operation | Short reported immediately |

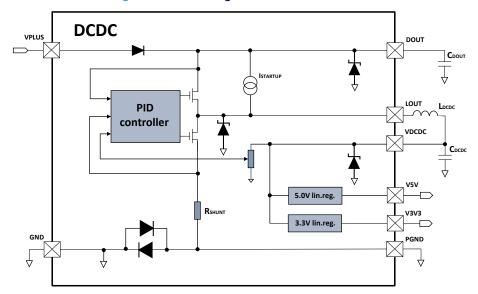

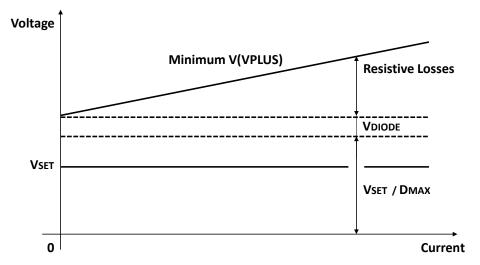

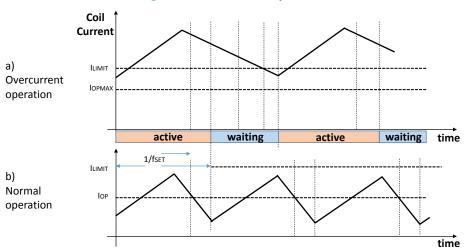

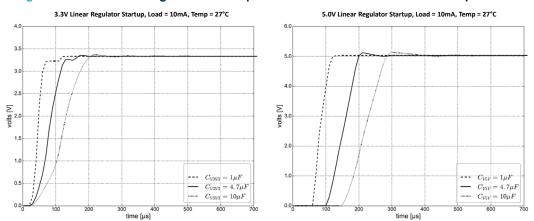

In transparent SIO operation (CCTL:TRNS='1', CCTL:SIO='1') a short is only reported after N retries, see t<sub>RETRY</sub>, which is suitable to indicate the presence of a valid IO-Link wake-up pulse.