## Automotive general purpose SPI to isolated SPI transceiver

#### **Features**

- AEC-Q100 qualified

- Full ISO26262 compliant, ASIL-D systems ready

- Compatible with both 3.3 V and 5 V logics

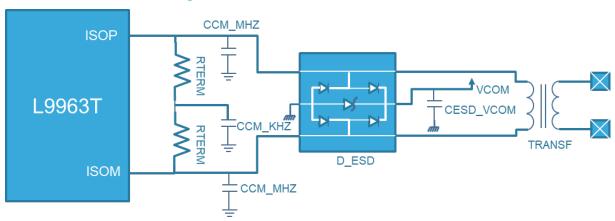

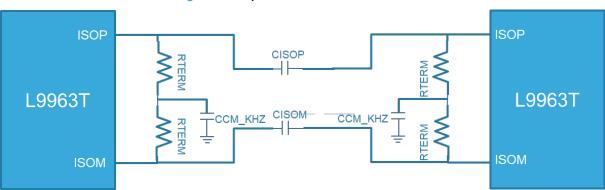

- Supports both XFMR and Capacitive isolation

- 10 MHz SPI peripheral for SPI Slave operation. Configurable SPI frequency (250 kHz to 8 MHz) for SPI Master operation

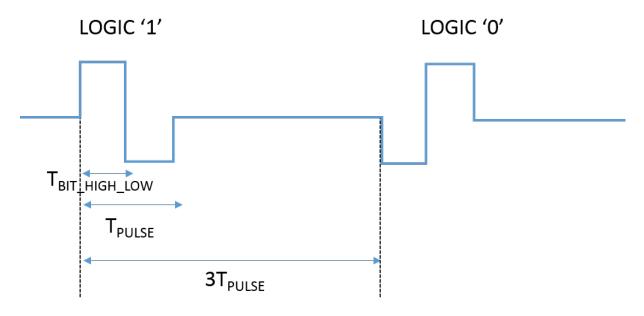

- 333 kbps and 2.66 Mbps Vertical InterFace (VIF) for isolated SPI communication

- · Low standby current

## **Application**

- · Automotive: 48 V and high-voltage systems

- Backup energy storage systems and UPS

- · Industrial communication networks

- · Portable and semi-portable equipment

- Remote sensors

## **Description**

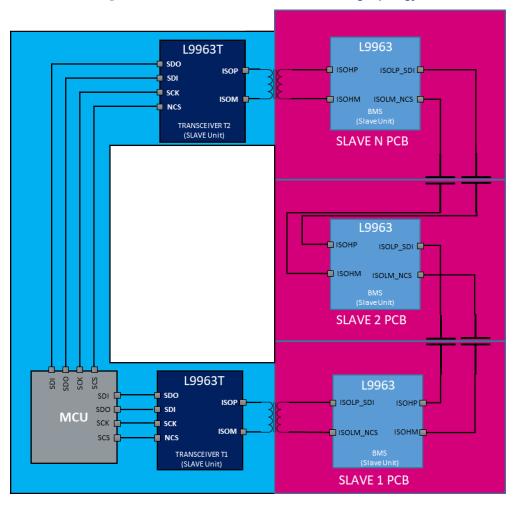

L9963T is a general purpose SPI to isolated SPI transceiver intended to create a communication bridge between devices located into different voltage domains.

L9963T is able to transfer communication data incoming from a classical 4-wire based SPI interface to a 2-wire isolated interface (and viceversa).

The transceiver supports both transformer and capacitive isolation, since the isolated signal generated according to a propetary protocol is suitable to be transmitted over both decoupling circuitries.

The device can be configured either as Slave or as Master of the SPI bus and supports any protocol made of SPI frames 8 to 64 bit long. The transceiver manages the transfer of the information without performing any protocol check.

SPI peripheral can work up to 10 MHz when configured as Slave. SPI clock frequency can be programmed among (250 kHz; 1 MHz; 4 MHz; 8 MHz) when configured as Master.

Isolated SPI peripheral features two different operating modes: slow @333 kbps and fast @2.66 Mbps.

The asynchronicity between the two sides is internally managed, allowing all possible configuration frequencies on both peripherals to be used in application.

L9963T features an internal queue of 3 slots for the frames received on the SPI port and a queue of 20 slots for the ones received on the isolated SPI side. This allows buffering and decoupling the two different clock domains.

The device is natively compatible with L9963 isolated SPI, allowing its usage in the BMS applications.

L9963T is compatible with both 3.3 V and 5 V logics.

## Product status link

L9963T

| Product summary            |        |           |  |  |  |

|----------------------------|--------|-----------|--|--|--|

| Order code Package Packing |        |           |  |  |  |

| L9963T                     | SO16N  | Tube      |  |  |  |

| L9963T-TR                  | 301010 | Tape&Reel |  |  |  |

## Product label

## 1 Block diagram and pin description

## 1.1 Block diagram

Figure 1. Block diagram VIO 16 VDD V3V3\_STBY SDO 15 ISOP SCK Main Logic Block 14 ISOM NCS V3V3\_STBY 13 GND DIS NSLAVE ISOFREQ TXEN/CPHA STBY LOGIC BNE/CPOL SPICLKFREQ TXAMP

1.2 Pin description

Figure 2. Pin connection diagram (top view)

DS13590 - Rev 1 page 2/46

Table 1. Pin list description

| Pin#      | 1                                              | Гуре                        | Local/<br>Global | Active  | Description                                                                                                                                                       |      |                                                                                                                                                                                                                |

|-----------|------------------------------------------------|-----------------------------|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                                |                             |                  | POWER   |                                                                                                                                                                   |      |                                                                                                                                                                                                                |

| VDD       | Р                                              | ower                        | Local            | -       | 5V supply input for internal logic and isolated SPI                                                                                                               |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  |         | Digital Output Buffer Supply.                                                                                                                                     |      |                                                                                                                                                                                                                |

| VIO       | P                                              | ower                        | Local            | -       | Connect either to 5 V or to 3.3 V supply.                                                                                                                         |      |                                                                                                                                                                                                                |

| GND       | G                                              | round                       | Local            | -       | Device Ground                                                                                                                                                     |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  | SPI     |                                                                                                                                                                   |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  |         | SPI Serial Data Output.                                                                                                                                           |      |                                                                                                                                                                                                                |

| SDO       | Digital Out                                    | put (Push-Pull)             | Local            | -       | Needs external pull up/pull down resistor to define inactive level.                                                                                               |      |                                                                                                                                                                                                                |

|           | Digital Input/                                 | NSLAVE = 0 → Digital Input  |                  |         | SPI Serial Clock.                                                                                                                                                 |      |                                                                                                                                                                                                                |

| SCK       | Output<br>(Push-Pull)                          | NSLAVE = 1 →                | Local            | -       | Internally pulled down with 100 k $\Omega$                                                                                                                        |      |                                                                                                                                                                                                                |

|           | (i dan-i dii)                                  | Digital Output              |                  |         | , ,                                                                                                                                                               |      |                                                                                                                                                                                                                |

| 0.01      | D                                              |                             |                  |         | SPI Serial Data Input.                                                                                                                                            |      |                                                                                                                                                                                                                |

| SDI       | Digit                                          | tal Input                   | Local            | -       | Internally pulled down with a 100 $k\Omega$ resistor for safety purposes.                                                                                         |      |                                                                                                                                                                                                                |

|           | Digital Input/                                 | NSLAVE = 0 → Digital Input  |                  |         | SPI Chip Select.                                                                                                                                                  |      |                                                                                                                                                                                                                |

| NCS       | Output<br>(Push-Pull)                          | NSLAVE = 1 → Digital Output | Local            | -       | Internally pulled up with a 100 $k\Omega$ resistor for safety purposes.                                                                                           |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  |         | SDO Buffer Not Empty flag.                                                                                                                                        |      |                                                                                                                                                                                                                |

|           | NSLAVE = 0 → BNE Digital<br>Output (Push-Pull) |                             |                  |         | Local                                                                                                                                                             | High | It is set high when at least one frame is in the RX buffer. It is set low when RX buffer is empty. When L9963T is configured as Slave, connect this pin to MCU GPIO for interrupt/polling based communication. |

|           |                                                |                             |                  |         | SPI Clock Polarity selection input.                                                                                                                               |      |                                                                                                                                                                                                                |

| BNE/CPOL  |                                                |                             |                  |         | Latched during Trimming & Config Latch.                                                                                                                           |      |                                                                                                                                                                                                                |

|           |                                                | → CPOL Digital nput         | Local            | _       | Connect either to VDD (CPOL = 1) or to GND (CPOL = 0).                                                                                                            |      |                                                                                                                                                                                                                |

|           |                                                | •                           |                  |         | Internally pulled down (active).                                                                                                                                  |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  |         | Input filtered with RC filter having f <sub>CUT_DIG_IN</sub> cut frequency.                                                                                       |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  |         | SPI Slave/Master selection.                                                                                                                                       |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  |         | Latched during Trimming & Config Latch                                                                                                                            |      |                                                                                                                                                                                                                |

| NSLAVE    | Digit                                          | tal Input                   | Local            | _       | Connect to GND to select Slave operation. Connect to VDD to select Master operation.                                                                              |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  |         | Internally pulled down (active).                                                                                                                                  |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  |         | Input filtered with RC filter having f <sub>CUT_DIG_IN</sub> cut frequency.                                                                                       |      |                                                                                                                                                                                                                |

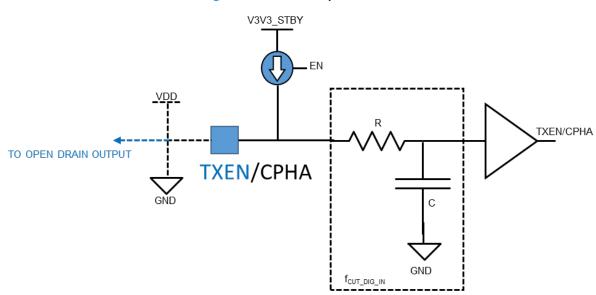

|           |                                                |                             |                  |         | Transmitter enable signal.                                                                                                                                        |      |                                                                                                                                                                                                                |

| TYPNIODUA | NSLAVE = 0 → TXEN Digital                      |                             | Local            | High    | Set high to enable the TX activity. Pull down to disable TX. Any data received on the SDI line while TXEN is low will be discarded and not stored into TX buffer. |      |                                                                                                                                                                                                                |

| TXEN/CPHA | I                                              | nput                        | Local            | l light | Internally pulled up (active).                                                                                                                                    |      |                                                                                                                                                                                                                |

|           |                                                |                             |                  |         | Input filtered with RC filter having f <sub>CUT_DIG_IN</sub> cut frequency.                                                                                       |      |                                                                                                                                                                                                                |

DS13590 - Rev 1 page 3/46

| Pin #      | Туре                              | Local/<br>Global | Active  | Description                                                                                                                                                          |       |       |       |       |   |                                                                                                  |

|------------|-----------------------------------|------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|---|--------------------------------------------------------------------------------------------------|

|            |                                   |                  |         | SPI Clock Phase selection input.                                                                                                                                     |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Latched during Trimming & Config Latch.                                                                                                                              |       |       |       |       |   |                                                                                                  |

| TXEN/CPHA  | NSLAVE = 0 → CPHA Digital Input   | Local            | _       | Connect either to VDD (CPHA = 1) or to GND (CPHA = 0).                                                                                                               |       |       |       |       |   |                                                                                                  |

|            | mpat                              |                  |         | Internally pulled up (active).                                                                                                                                       |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Input filtered with RC filter having f <sub>CUT_DIG_IN</sub> cut frequency.                                                                                          |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | SPI Master Clock selection.                                                                                                                                          |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Latched during Trimming & Config Latch.                                                                                                                              |       |       |       |       |   |                                                                                                  |

| SPICLKFREQ | Analog Input                      | Local            | -       | Leave open to set minimum frequency. Connect a pull down resistor to set a higher frequency.                                                                         |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Input filtered with RC filter having f <sub>CUT_DIG_IN</sub> cut frequency.                                                                                          |       |       |       |       |   |                                                                                                  |

|            |                                   | ISO              | LATED   | SPI                                                                                                                                                                  |       |       |       |       |   |                                                                                                  |

| ISOP       | Analog Input/Output               | Global           | -       | Isolated SPI Positive terminal                                                                                                                                       |       |       |       |       |   |                                                                                                  |

| ISOM       | Analog Input/Output               | Global           | -       | Isolated SPI Negative terminal                                                                                                                                       |       |       |       |       |   |                                                                                                  |

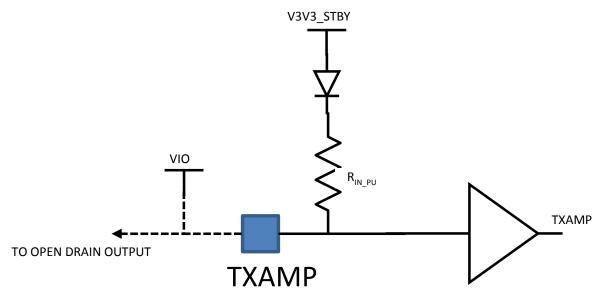

|            |                                   |                  |         | Isolated SPI TX amplitude selection.                                                                                                                                 |       |       |       |       |   |                                                                                                  |

| TXAMP      | Digital Input                     | Local            | Local   | Local                                                                                                                                                                | Local | Local | Local | Local | - | Set low to select low amplitude/low threshold. Set high to select high amplitude/high threshold. |

|            |                                   |                  |         | Internally pulled up with a 100 $k\Omega$ resistor.                                                                                                                  |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Isolated SPI operating frequency selection.                                                                                                                          |       |       |       |       |   |                                                                                                  |

| ISOFREQ    | Digital Input                     | Local            |         | Pull high to set high frequency.                                                                                                                                     |       |       |       |       |   |                                                                                                  |

| 1301 KLQ   | Digital Iliput                    | Lucai            | _       | Pull down to set low frequency.                                                                                                                                      |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Internally pulled down (active).                                                                                                                                     |       |       |       |       |   |                                                                                                  |

|            |                                   |                  | DISABLE |                                                                                                                                                                      |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Transceiver Disable Input.                                                                                                                                           |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Pull it up with external resistor connected to VIO. When DIS is high, L9963 enters in low power mode. When DIS is low, L9963T is enabled and working in Normal mode. |       |       |       |       |   |                                                                                                  |

| DIS        | Digital Input/Output (Open Drain) | Local            | High    | It can be either pulled-down by the MCU to enable the unit, or pulled down internally when a wakeup condition occurs, in order to interrupt the MCU.                 |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Pin is internally pulled up with 100 $k\Omega$ resistor.                                                                                                             |       |       |       |       |   |                                                                                                  |

|            |                                   |                  |         | Input filtered with RC filter having f <sub>CUT_DIG_IN</sub> cut frequency.                                                                                          |       |       |       |       |   |                                                                                                  |

DS13590 - Rev 1 page 4/46

## Product electrical and thermal ratings

#### 2.1 Supply ranges

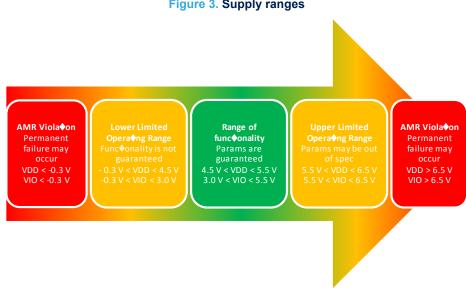

Figure 3 lists the product power supply ranges:

- Within the range of functionality the part operates as specified and without parameter deviations. All the functionalities and the electrical parameters are guaranteed.

- If either the upper or the lower limited operating range is reached, the device may not operate properly. Only a limited set of functionalities and electrical parameters are guaranteed. However, neither damage nor parameter deviation occurs, and the device will operate properly once returned to the range of functionality.

- If AMR are violated, permanent damage or parametric deviation may occur.

Figure 3. Supply ranges

Note: all voltages are related to the potential at substrate ground GND.

#### 2.2 **Operating range**

Table 2. Pin operating range

| Pin                                              | Condition                         | Min | Тур | Max | Unit |

|--------------------------------------------------|-----------------------------------|-----|-----|-----|------|

| VDD                                              | Supply pin                        | 4.5 | -   | 5.5 | V    |

| VIO                                              | Digital Output Buffers supply pin | 3.0 | -   | 5.5 | V    |

| DIS, ISOFREQ, BNE/CPOL, TXAMP, TXEN/CPHA, NSLAVE | Digital I/Os                      | 0   | -   | VIO | V    |

| ISOP + ISOM  / 2                                 | Isolated SPI Common Mode Voltage  | 1   | 1.2 | 1.4 | V    |

| ISOP - ISOM                                      | Isolated SPI Differential Voltage | 0   | -   | 2.5 | V    |

| SDO, SCK, SDI, NCS                               | SPI pins                          | 0   | -   | VIO | V    |

| SPICLKFREQ                                       | Analog Input                      | 0   | -   | VDD | V    |

Note: all voltages are related to the potential at substrate ground GND.

DS13590 - Rev 1 page 5/46

## 2.3 Absolute maximum rating

Table 3. Absolute maximum rating

| Symbol                                           | Parameter                                        | Min  | typ | Max       | Unit |

|--------------------------------------------------|--------------------------------------------------|------|-----|-----------|------|

| VIO, VDD                                         | Supply Input Voltage                             | -0.3 | -   | 6.5       | V    |

| BNE/CPOL, NSLAVE, DIS, TXEN/CPHA, ISOFREQ, TXAMP | Digital I/Os                                     | -0.3 | -   | 6.5       | V    |

| ISOP, ISOM                                       | Analog I/Oson isolated SPI side                  | -0.3 | -   | 6.5       | V    |

| SDO, SCK, SDI, NCS                               | Serial Peripheral Interface Communicati on Ports | -0.3 | -   | VIO + 0.3 | V    |

| SPICLKFRQ                                        | Analog Input for SPI clock frequency selection   | -0.3 | -   | 6.5       | V    |

Note: all voltages are related to the potential at substrate ground GND.

## 2.4 ESD protection

**Table 4. ESD protection**

| Item                                                                                        | Condition               | Min  | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------|-------------------------|------|-----|-----|------|

| All pins Except Isolated Communication Terminals and Global pins <sup>(1)</sup>             | HBM <sup>(2)</sup>      | -2   | -   | 2   | KV   |

| Isolated Communication Terminals <sup>(1)(2)</sup> and Global pins versus all GND connected |                         |      |     |     | KV   |

| All pins except Corner Pins                                                                 | CDM <sup>(3)</sup>      | -500 | -   | 500 | V    |

| Corner Pins                                                                                 | CDIVIC                  | -750 | -   | 750 | V    |

| All pins                                                                                    | Latch up <sup>(4)</sup> | -100 | -   | 100 | mA   |

- 1. Tested per AEC-Q100-002.

- 2. Isolated Communication Terminals: ISOP, ISOM.

- 3. Tested per AEC-Q100-011.

- 4. Tested per AEC-Q100-004, Class-2, Level-A.

Note: pins are all GND connected together.

## 2.5 Temperature ranges and thermal data

Table 5. Temperature ranges and thermal data

| Symbol               | Parameter                                           | Min | Тур | Max | Unit |

|----------------------|-----------------------------------------------------|-----|-----|-----|------|

| T <sub>amb</sub>     | Operating and testing temperature (ECU environment) | -40 | -   | 105 | °C   |

| T <sub>j</sub>       | Junction temperature for all parameters             | -40 | -   | 125 | °C   |

| T <sub>stg</sub>     | Storage temperature                                 | -65 | -   | 125 | °C   |

| R <sub>THj-amb</sub> | Thermal resistance junction-to-ambient              | -   | -   | 90  | °C/W |

DS13590 - Rev 1 page 6/46

## 2.6 Power mangement

All parameters are tested and guaranteed in the following conditions, unless otherwise specified: -40  $^{\circ}$ C < Tj < 125  $^{\circ}$ C

Table 6. Power management

| Symbol                         | Parameter          | Condition                                                    | Min | Тур | Max | Unit |  |

|--------------------------------|--------------------|--------------------------------------------------------------|-----|-----|-----|------|--|

|                                | Power Supply VDD   |                                                              |     |     |     |      |  |

| V <sub>VDD</sub>               | Supply Voltage     | FullyOperational                                             | 4.5 | -   | 5.5 | V    |  |

| I <sub>VDD</sub> (NORMAL_COMM) | Supply Current     | NormalMode, DIS = 0 and continuos communication              | -   | 9   | 14  | mA   |  |

| I <sub>VDD(NORMAL)</sub>       | Supply Current     | NormalMode, DIS = 0                                          | 5   | 6.5 | 8   | mA   |  |

| I <sub>VDD(SLEEP)</sub>        | Supply Current     | Sleep Mode, DIS = 1                                          | -   | -   | 64  | μA   |  |

|                                |                    | Power Supply VIO                                             |     |     |     |      |  |

| V <sub>VIO</sub>               | Supply Voltage     |                                                              | 3.0 | -   | 5.5 | V    |  |

| IVIO(NORMAL_COMM)              | VIO Supply Current | NormalMode, DIS = 0 and continuous communication Design info | -   | -   | 12  | mA   |  |

| I <sub>VIO(NORMAL)</sub>       | VIO Supply Current | NormalMode, DIS = 0                                          | 1.5 | 2.5 | 3.5 | mA   |  |

| I <sub>VIO(SLEEP)</sub>        | VIO Supply Current | Sleep Mode, DIS = 1                                          | -   | -   | 1   | μΑ   |  |

To optimize power consumption, the device selectively disables unnecessary peripherals according to FSM state and **NSLAVE** pin value latched at first power up.

Table 7. Device configuration according to NSLAVE pin

| FSM STATE                    | TRIMMING AND CONFIG   | STAND-BY                      | NORMAL                          |                            |  |

|------------------------------|-----------------------|-------------------------------|---------------------------------|----------------------------|--|

| Resource                     | NSLAVE not<br>latched | NSLAVE latched but don't care | NSLAVE = 0 (SPI<br>Slave)       | NSLAVE = 1 (SPI<br>Master) |  |

| Main Oscillator Monitor      | Disabled              | Disabled                      | Ena                             | bled                       |  |

| V3V3_MAIN Monitor            | Disabled              | Disabled                      | Ena                             | bled                       |  |

| V3V3_STBY Monitor            | Disabled              | Disabled                      | Ena                             | bled                       |  |

| BG STBY                      | Enabled               | Enabled                       | Ena                             | bled                       |  |

| BG Main (STBY Monitor)       | Disabled              | Disabled                      | Ena                             | bled                       |  |

| SDO Output Buffer            | Disabled              | Disabled                      | Enabled only when NCS is active |                            |  |

| SCK Output Buffer            | Disabled              | Disabled                      | Disabled                        | Enabled                    |  |

| SCK Input Buffer             | Disabled              | Disabled                      | Ena                             | bled                       |  |

| SDI Input Buffer             | Disabled              | Disabled                      | Ena                             | bled                       |  |

| NCS Output Buffer            | Disabled              | Disabled                      | Disabled                        | Enabled                    |  |

| NCS Input Buffer             | Disabled              | Disabled                      | Ena                             | bled                       |  |

| BNE/CPOL Output Buffer       | Disabled              | Disabled                      | Enabled                         | Disabled                   |  |

| BNE/CPOL Input Buffer        | Enabled               | Disabled                      | Enabled                         | Enabled                    |  |

| NSLAVE Input Buffer          | Enabled               | Disabled                      | Disabled                        |                            |  |

| TXEN/CPHA Input Buffer       | Enabled               | Disabled                      | Enabled Disabled                |                            |  |

| SPICLKFREQ Input Comparators | Enabled               | Disabled                      | Disabled                        |                            |  |

| ISOP TX                      | Disabled              | Disabled                      | Ena                             | bled                       |  |

DS13590 - Rev 1 page 7/46

| FSM STATE                    | TRIMMING AND<br>CONFIG | STAND-BY                      | NORMAL                    |                                     |  |

|------------------------------|------------------------|-------------------------------|---------------------------|-------------------------------------|--|

| Resource                     | NSLAVE not<br>latched  | NSLAVE latched but don't care | NSLAVE = 0 (SPI<br>Slave) | NSLAVE = 1 (SPI<br>Master)          |  |

| ISOM RX                      | Disabled               | Disabled                      | Ena                       | bled                                |  |

| ISOM RX Wake up              | Disabled               | Enabled                       | Disa                      | abled                               |  |

| TXAMP Input Buffer           | Disabled               | Disabled                      | Enabled                   |                                     |  |

| ISOFREQ Input Buffer         | Disabled               | Disabled                      | Enabled                   |                                     |  |

| DIS Input Buffer             | Disabled               | Enabled                       | Ena                       | bled                                |  |

| DIS Open Drain Driver        | Disabled               | Disabled                      |                           | from VIF detected, and DIS_PULLDOWN |  |

| NSLAVE Pull down             | Enabled                | Disabled                      | Disa                      | abled                               |  |

| BNE/CPOL Pull down           | Enabled                | Disabled                      | Enabled                   |                                     |  |

| TXEN/CPHA Pull up            | Enabled                | Disabled                      | Enabled                   |                                     |  |

| SPICLKFREQ Pull up & Divider | Enabled                | Disabled                      | Disabled                  |                                     |  |

DS13590 - Rev 1 page 8/46

## 3 Functional description

In the following paragraphs, the functionalities of the device are listed and described in detail.

#### 3.1 Internal oscillators

L9963T features two internal oscillators for both main and stanby functionalities.

Table 8. Device oscillators

| Symbol                | PARAMETER                          | MIN | TYP | MAX | UNIT |

|-----------------------|------------------------------------|-----|-----|-----|------|

| f <sub>MAIN_OSC</sub> | Internal MAIN Oscillator frequency | 15  | 16  | 17  | MHz  |

| f <sub>STBY_OSC</sub> | Internal STBY Oscillator frequency | 24  | 32  | 50  | kHz  |

### 3.2 Pin configuration

All device pins are hereby described.

#### 3.2.1 Digital I/Os

In the following paragraph, the functionality of the Digital I/Os is explained.

BNE/CPOL, TXEN/CHPA are used as standard digital input (Schmitt trigger) or digital output (Output buffer) configuration, depending on the configuration defined by digital NSLAVE pin.

DIS is used as standard digital input (Schmitt trigger) or digital output (Open Drain) configuration, depending on the state the device is in. When it's in STAND-BY state and a wake up comes from ISO line the DIS pin is driven low by L9963T.

NSLAVE, ISOFREQ, TXAMP are used as standard digital input (Schmitt trigger) for the configuration of device.

#### 3.2.1.1 SPI pin

**SDO, SCK, SDI, NCS** pins implement the SPI peripheral, whose configuration depends on the **NSLAVE** value latched at first power up:

- SDI is always configured as digital input. It is internally pulled down with RIN\_PD in order to generate a 0x0 frame in case of pin loss (purpose is to lead to CRC violation in safety applications). Its buffer is enabled only in **Normal state**.

- SDO is always configured as digital output. Its buffer is enabled only if **NCS** is asserted. An external pull up/pull down resistor defines the inactive level of the line.

- SCK, NCS can be either configured as digital input (NSLAVE = 0, SPI Slave) or as digital output (NSLAVE = 1, SPI Master):

- SCK pin is internally pulled down with RIN\_PD in order to stabilize clock signal to logic '0' in case of pin loss

- NCS pin is internally pulled up with RIN PU in order to disable SPI peripheral in case of pin loss.

- When SCK and NCS are configured as digital input (NSLAVE = 0), the output buffers are permanently disabled after Trimming & Config Latch is left.

- When SCK and NCS are configured as digital output (NSLAVE = 1), the NCS inactive level is high, and

it is actively forced by the output buffer while no SPI communication is ongoing. The SCK inactive level

depends on the CPOL value latched in **Trimming & Config Latch** state, and it is actively forced by the

output buffer while no SPI communication is ongoing.

The selective enable/disable of the buffers helps reducing the power consumption of the device when SPI works at high frequencies.

DS13590 - Rev 1 page 9/46

#### 3.2.1.2 **NSLAVE**

**NSLAVE** pin is latched by the standby logic in the **Trimming & Config Latch** state,  $3T_{OSC\_STBY}$  after POR\_MAIN release. It must be either shorted to VDD or to GND. The internal pull-down is enabled only while in **Trimming & Config Latch** state. This allows reducing power consumption. Once **Trimming & Config Latch** state is left, the **NSLAVE** input buffer is permanently disabled, since it is no longer needed.

**NSLAVE** selects SPI Master (**NSLAVE = 1**) or Slave (**NSLAVE = 0**) operation and determines the Digital I/Os configuration as described in Table 7.

To increase immunity to BCI and guarantee a correct latch of the **NSLAVE** pin during each poweup, the input is filtered with an integrated RC filter having  $f_{CUT\ DIG\ IN}$  cut frequency.

NSLAVE

R

NSLAVE

OF THE TRANSLAVE

NSLAVE

Figure 4. NSLAVE pin structure

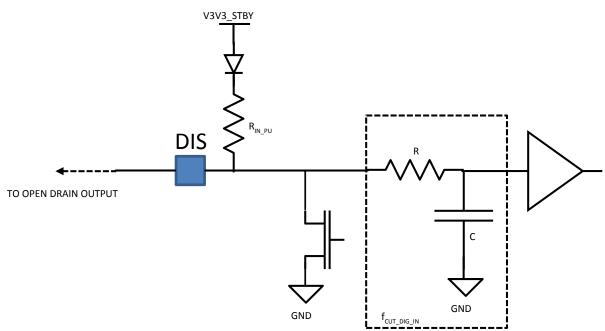

### 3.2.1.3 DIS

**DIS** is a Digital Input-Output pin featuring an internal pull-up resistor towards V3V3\_STBY. Its purpose is to be driven by open-drain outputs. Its functionality is summarized as follows:

- Input: it is an active high Disable input driven by the MCU:

- When DIS is released by the MCU longer than T<sub>RC\_DELAY</sub> +T<sub>DIS\_DEGLITCH</sub> the device starts the Go To Sleep sequence that will bring L9963T to **Stand-by state** (refer to **L9963T FSM**).

- When DIS is pulled down by the MCU longer than T<sub>RC\_DELAY</sub> + (1/ f<sub>STBY\_OSC</sub>) the device moves from Stand-by state to Regulators enabling state and then to Normal state.

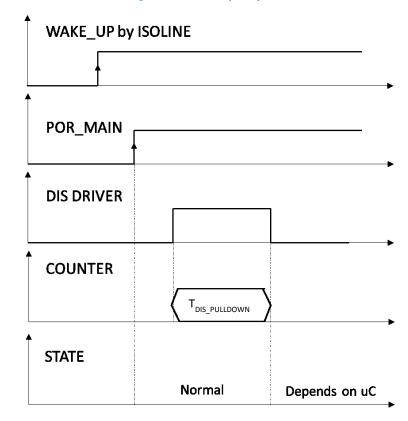

- Output: when L9963T is in Stand-by state, and a wakeup event by isolated SPI occurs, it moves to

Regulators enabling state and then to Normal state. Once the latter is reached, DIS is internally pulleddown by logic for T<sub>DIS\_PULLDOWN</sub> in order to trigger an interrupt in the MCU or a wake up event on a PMIC.

After T<sub>DIS\_PULLDOWN</sub> expires, DIS is released, and if not kept low by an external source, L9963T moves

back to Stand-by state.

To protect **DIS** internal open drain driver in case of external short to VDD, a current limitation circuitry limits the current to  $I_{DIS\ LIM}$ .

DS13590 - Rev 1 page 10/46

Figure 5. DIS pin structure

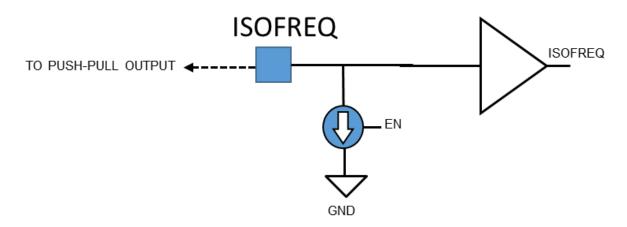

#### 3.2.1.4 ISOFREQ

**ISOFREQ** pin is a digital input used to switch ISOline bitrate:

- ISOFREQ = 1 selects fast operation: bit time is TBIT\_LENGTH\_FAST

- ISOFREQ = 0 selects slow operation: bit time is TBIT\_LENGTH\_SLOW

**ISOFREQ** sampling depends on device state and configuration:

Table 9. ISOFREQ sampling strategy

| L9963T<br>state | L9963T<br>configuration      | ISOFREQ sampling                                                                                                                                                                                                                                                                    | Note        |

|-----------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Normal<br>state | Slave (NSLAVE = 0)           | ·                                                                                                                                                                                                                                                                                   |             |

|                 | Master (NSLAVE = 1)          | The ISOFREQ setting is simply resynchronized (TISOFREQ_SETUP and TISOFREQ_HOLD requirements still apply) and deglitched (TISOFREQ_DEGLITCH filter still present), but it is not latched upon NCS assertion.                                                                         | supported). |

| Stand-by state  | Slave/Master<br>(NSLAVE = X) | The new ISOFREQ setting is latched during the wake up sequence. Hence, the ISOFREQ pin shall be stable $ \textbf{T}_{\textbf{ISOFREQ\_SETUP}} \text{ before the DIS high} \rightarrow \text{low transition is applied and shall not change during } \textbf{T}_{\textbf{WAKEUP}}. $ | -           |

| Reset<br>state  | Slave/Master<br>(NSLAVE = X) | The initial ISOFREQ setting is latched during the first power up sequence. Hence, the ISOFREQ pin shall be stable before VDD is applied and shall not change during T <sub>FIRST_POWERUP</sub> .                                                                                    | -           |

The new bitrate of L9963T must be compatible with the one of all other units communicating on the same bus.

DS13590 - Rev 1 page 11/46

The internal pull-down guarantees a limp home operation in low frequency in case of pin-loss.

Figure 6. ISOFREQ pin structure

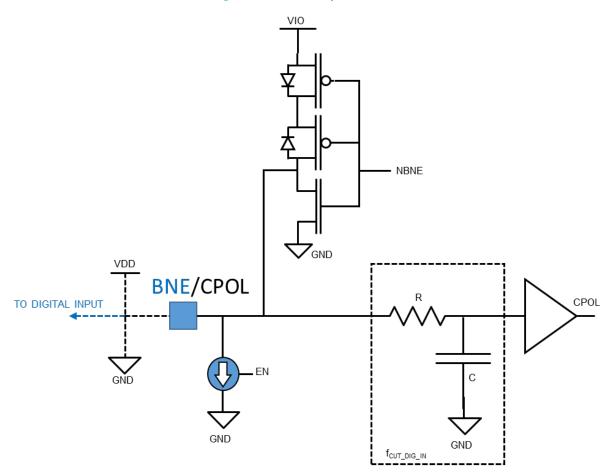

#### 3.2.1.5 BNE/CPOL

**BNE/CPOL** is a digital input/output pin whose configuration depends on the value of NSLAVE latched during **Trimming & Config Latch**:

- When NSLAVE = 0 (Slave configuration), this pin acts as BNE (Buffer Not Empty) digital output and its

purpose is to implement interrup-based communication with the MCU. When asserted high, it means that the

RX queue stores at least one frame.

- When NSLAVE = 1 (Master configuration), this pin acts as digital input for the selection of CPOL (Clock POLarity):

- CPOL = 0 (shorted to GND) implies that the clock inactive level (when NCS is high) is low.

- CPOL = 1 (shorted to VDD) implies that the clock inactive level (when NCS is high) is high.

The internal pull-down is always enabled during **Trimming & Config Latch** and in **Normal state**.

The **BNE** output buffer is disabled if NSLAVE = 1 has been latched during **Trimming & Config Latch**. The **CPOL** input buffer is permanently enabled.

In case NSLAVE = 0 has been latched during **Trimming & Config Latch**, **BNE** output buffer is kept enabled while in **Normal state**. A short to GND/VDD detection is implemented to protect the **BNE** output buffer. If the value forced on the BNE output buffer differs from the one sampled by the CPOL input buffer for more than T<sub>BNE\_SHORT\_DET</sub>, the BNE output buffer is put into HiZ. Automatic re-engagement of the BNE output buffer occurs upon next wakeup sequence (MCU needs to toggle DIS pin).

DS13590 - Rev 1 page 12/46

Figure 7. BNE/CPOL pin structure

#### 3.2.1.6 TXEN/CPHA

**TXEN\_CPHA** is a digital input pin whose configuration depends on the value of NSLAVE latched during **Trimming & Config Latch**:

- When NSLAVE = 0 (Slave Configuration) the pin works as transmitter enable input TXEN:

- MCU should release TXEN (or pull it up actively) prior to NCS assertion in order to enable the transmission of the data from SDI input buffer to the TX queue (and then to the isolated SPI interface).

- In case the communication protocol does not feature any burst read capability, each command sent by the master unit will generate a single answer from the addressed slave unit. Hence TXEN pin can be connected to VDD in order to keep the transmitter permanently enabled.

- In case of burst read operations, where user SW has to empty the RX queue without transmitting any

frame on the isolated SPI, the TXEN input must be pulled down before beginning the burst read.

- Even if data on the SDI line is discarded while TXEN = 0, it is highly recommended that MCU sends dummy frames (or intentionally corrupted frames) on the SDI line during the burst read. In the event of TXEN stuck high, such frames will generate errors according to the implemented communication protocol.

- To avoid chopping frames currently being transmitted, the TXEN pin is latched upon NCS assertion.

Therefore, it must be stable at least T<sub>TXEN\_DEGLITCH</sub> + T<sub>TXEN\_SETUP</sub> before NCS assertion. Moreover, TXEN must be kept stable T<sub>TXEN\_HOLD</sub> after NCS assertion in order to fulfil hold time constraints.

DS13590 - Rev 1 page 13/46

- When NSLAVE = 1 (Master configuration), this pin acts as digital input for the selection of CPHA (Clock PHAse). It is latched during Trimming & Config Latchand should be therefore either shorted to GND or to VDD:

- CPHA = 0 (shorted to GND) implies that the SDI signal will be sampled upon the first SCK edge after NCS assertion.

- CPHA = 1 (shorted to VDD) implies that the SDI signal will be sampled upon the second SCK edge after NCS assertion.

The internal pull-up is enabled when L9963T is in **Trimming & Config Latch** and is kept enabled in **Normal state** in order to allow a correct driving of the pin by the open-drain output of the MCU. Moreover, in case of pin loss, the pull-up guarantees a limp home operation where the transmitter is always enabled. To guarantee standby consumption requirements, the pull-up is disabled while in **Stand-by state**.

Figure 8. TXEN/CPHA pin structure

#### 3.2.1.7 TXAMP

**TXAMP** pin can be used to switch among the two possible ISOline TX amplitude configurations:

- TXAMP = 0 selects low TX amplitude (RDIFF\_ISO\_OUTL)

- TXAMP = 1 selects high TX amplitude (RDIFF\_ISO\_OUTH)

**TXAMP** sampling depends on device state and configuration:

Table 10. TXAMP sampling strategy

| L9963T<br>state | L9963T<br>configuration | TXAMP sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Note                                                                                                                                          |

|-----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Normal<br>state | Slave (NSLAVE = 0)      | The <b>TXAMP</b> pin is latched upon <b>NCS</b> assertion. Therefore, it must be stable at least <b>T</b> <sub>TXAMP_DEGLITCH</sub> + <b>T</b> <sub>TXAMP_SETUP</sub> before NCS assertion. Moreover, TXAMP must be kept stable <b>T</b> <sub>TXAMP_HOLD</sub> after NCS assertion in order to fulfil hold time constraints.  The new amplitude setting is applied to the TX interface after the SPI frame has been completely transmitted over the isolated SPI interface. This allows <b>Managing ISOFREQ And TXAMP Pins For Communicating With L9963</b> . | In case several SPI frames are being pushed into the TX queue, the setting applied depends on the last one latched (no pipelining supported). |

DS13590 - Rev 1 page 14/46

| L9963T<br>state   | L9963T<br>configuration      | TXAMP sampling                                                                                                                                                                                                                                                                                                                                                                    | Note                                                                                                                                          |

|-------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Normal<br>state   | Master (NSLAVE = 1)          | The TXAMP setting is simply resynchronized (T <sub>TXAMP_SETUP</sub> and T <sub>TXAMP_HOLD</sub> requirements still apply) and deglitched (T <sub>TXAMP_HOLD</sub> filter still present), but it is not latched upon NCS assertion. The new amplitude setting is applied to the TX interface as soon as the transmission of the SPI frame over the isolated SPI interface begins. | In case several SPI frames are being pushed into the TX queue, the setting applied depends on the last one latched (no pipelining supported). |

| Stand-by<br>state | Slave/Master<br>(NSLAVE = X) | The new TXAMP setting is latched during the wakeup sequence. Hence, the TXAMP pin shall be stable $T_{TXAMP\_SETUP}$ before the DIS high $\rightarrow$ low transition is applied and shall not change during $T_{WAKEUP}$ .                                                                                                                                                       | -                                                                                                                                             |

| Reset<br>state    | Slave/Master<br>(NSLAVE = X) | The initial TXAMP setting is latched during the first power up sequence. Hence, the TXAMP pin shall be stable before VDD is applied and shall not change during TFIRST_POWERUP.                                                                                                                                                                                                   | -                                                                                                                                             |

It is recommended to apply the same TXAMP setting to all the devices communicating on the bus, in order to keep a constant SNR in every communication phase.

In order to meet standby consumption requirements, MCU must release the open drain output connected to **TXAMP** while L9963T is in **Stand-by state**.

Figure 9. TXAMP pin structure

### 3.2.1.8 Electrical parameters - Digital I/O

### 3.2.1.8.1 Digital input

All parameters are tested and guaranteed in the following conditions, unless otherwise specified:  $4.5 \text{ V} \leq V_{VDD} \leq 5.5 \text{ V}$ ; -40 °C < Tj < 125 °C

Table 11. Digital input electrical characteristics

| Symbol            | Parameters                | Test conditions | Min | Тур | Max | Unit |

|-------------------|---------------------------|-----------------|-----|-----|-----|------|

| V <sub>IN_L</sub> | Logic input low voltage.  | -               | -   | -   | 8.0 | V    |

| V <sub>IN_H</sub> | Logic input high voltage. | -               | 1.8 | -   | -   | V    |

DS13590 - Rev 1 page 15/46

| Symbol                         | Parameters                                                                                                                                                                                                                                                             | Test conditions                        | Min   | Тур | Max   | Unit |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------|-----|-------|------|

| V <sub>IN_HYS</sub>            | Input hysteresis.                                                                                                                                                                                                                                                      | Calculation<br>V <sub>IN_H-VIN_L</sub> | 0.15  | -   | 0.4   | V    |

| f <sub>CUT_DIG_IN</sub>        | Input Buffer RC filter. Applies to BNE_CPOL, NSLAVE, TXEN_CPHA, SPICLKFREQ, DIS.                                                                                                                                                                                       | Design info, not tested in ATE         | 0.7   | -   | 1     | MHz  |

| T <sub>RC_DELAY</sub>          | Analog delay introduced by the f <sub>CUT_DIG_IN</sub> RC filter.                                                                                                                                                                                                      | VIO = 3.3 V                            | -     | -   | 700   | ns   |

| R <sub>IN_PD</sub>             | Input pull down resistor. Applies to SCK, SDI.                                                                                                                                                                                                                         | -                                      | 70    | 100 | 130   | kΩ   |

| R <sub>IN_PU</sub>             | Input pull up resistor. Applies to NCS, TXAMP, DIS.                                                                                                                                                                                                                    | -                                      | 70    | 100 | 130   | kΩ   |

| T <sub>TXEN_DEGLITCH</sub>     | Up/Reset counter to avoid glitches on TXEN input. The counter counts up if TXEN is stable. The counter is reset upon a TXEN glitch (whatever slope). TXEN must be stable at least T <sub>TXEN_DEGLITCH</sub> before the NCS assertion.                                 | Guaranteed by<br>SCAN                  | 562.5 | 625 | 687.5 | ns   |

| T <sub>TXEN_HOLD</sub>         | TXEN hold time after the NCS assertion.                                                                                                                                                                                                                                |                                        | -     | -   | 300   | ns   |

| T <sub>TXAMP_DEGLITCH</sub>    | Up/Reset counter to avoid glitches on TXAMP input. The counter counts up if TXAMP is stable. The counter is reset upon a TXAMP glitch (whatever slope). TXAMP must be stable at least T <sub>TXAMP_DEGLITCH</sub> + T <sub>TXAMP_SETUP</sub> before the NCS assertion. |                                        | 562.5 | 625 | 687.5 | ns   |

| T <sub>TXAMP_HOLD</sub>        | TXAMP hold time after the NCS assertion.                                                                                                                                                                                                                               | -                                      | -     | -   | 300   | ns   |

| T <sub>ISOFREQ_</sub> DEGLITCH | Up/Reset counter to avoid glitches on ISOFREQ input. The counter counts up if ISOFREQ is stable. The counter is reset upon a ISOFREQ glitch (whatever slope). ISOFREQ must be stable at least TISOFREQ_DEGLITCH+TISOFREQ_SETUP before the NCS assertion.               |                                        | 562.5 | 625 | 687.5 | ns   |

| T <sub>ISOFREQ_HOLD</sub>      | ISOFREQ hold time after the NCS assertion.                                                                                                                                                                                                                             |                                        | -     | -   | 300   | ns   |

| I <sub>IN_PD</sub>             | Input pull down current. Applies to NSLAVE, ISOFREQ, BNE/CPOL.                                                                                                                                                                                                         | V <sub>PIN</sub> = 5 V                 | 35    | 50  | 65    | μA   |

| I <sub>IN_PU</sub>             | Input pull up current. Applies to TXEN/CPHA.                                                                                                                                                                                                                           | V <sub>PIN</sub> = 0 V                 | 35    | 50  | 65    | μA   |

## 3.2.1.8.2 Digital output

### **3.2.1.8.2.1** Output buffer

All parameters are tested and guaranteed in the following conditions, unless otherwise specified:  $4.5 \text{ V} \leq V_{VDD} \leq 5.5 \text{ V}$ ; -40 °C < Tj < 125 °C

Table 12. Output buffer electrical characteristics

| Symbol                     | Parameters                                               | Test conditions                                                                   | Min     | Тур | Max | Unit |

|----------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------|---------|-----|-----|------|

| V <sub>OUT_L</sub>         | Low output level.                                        | I = 2 mA                                                                          | 0       | -   | 0.4 | V    |

| V <sub>OUT_H</sub>         | High output level.                                       | I = -2 mA                                                                         | VIO-0.4 | -   | VIO | V    |

| T <sub>OUT_trans</sub>     | Digital output Rise and Fall time.<br>Not valid for SDO. | Cload = 12 0pF 20-80% on rising edge of DIG_OUT 80-20% on falling edge of DIG_OUT | 5       | -   | 400 | ns   |

| T <sub>BNE_SHORT_DET</sub> | BNE output short detection filter time.                  | Guaranteed by SCAN                                                                | -       | 5   | -   | μs   |

DS13590 - Rev 1 page 16/46

#### 3.2.1.8.2.2 Open drain (DIS)

All parameters are tested and guaranteed in the following conditions, unless otherwise specified:  $4.5 \text{ V} \leq V_{VDD} \leq 5.5 \text{ V}$ ; -40 °C < Tj < 125 °C

**Parameters** Min Max Unit **Symbol Test conditions** Тур DIS output level when the pull **VDISL** ٧ 0.4 down stage is ON I<sub>DIS</sub> = 5 mA DIS output current limitation for 8 I<sub>DIS\_LIM</sub> 18 mΑ  $V_{DIS} = 5 V$ Time interval after POR\_MAIN when DIS pin is internally pulled-down, upon a wake up by VIF. T<sub>DIS\_PULLDOWN</sub> Guaranteed by SCAN 800 ms Purpose is to trigger interrupt in the MCU or wake up on a PMIC. Up/Reset counter to avoid positive glitches on DIS input when the L9963T is in Normal state. The T<sub>DIS</sub> DEGLITCH Guaranteed by SCAN 1 2 3 μs counter counts up if DIS = 1, while it is reset if DIS =

Table 13. Open drain electrical characteristics

#### 3.2.2 Analog input

#### 3.2.2.1 SPICLKFREQ

**SPICLKFREQ** pin is an analog input, compared to four thresholds by a set of analog comparators.

An external resistor  $R_{CLKPD}$  must be connected between SPICLKFREQ and GND, in order to generate a voltage  $V_{SPICLKFREQPU}$ .

[UR8M\_0401190]The code obtained from these 4 comparators outputs (as indicated in the following table) is latched in the **Trimming & Config Latch** to determine the SPI Clock frequency when L9963T works in Master mode (**NSLAVE = 1**).

250 kHz 1 MHz 4 MHz 8 MHz 250 kHz SCLK Frequency

VCLKTH1 VCLKTH2 VCLKTH3 VCLKTH4 VSPICLKFREQ [V]

Figure 10. SPICLKFREQ thresholds

Table 14. SPICLKFREQ thresholds

| V <sub>SPICLKFREQ</sub> [V] (typ.)                                  | Vcode [3:0] | SCLK Frequency |

|---------------------------------------------------------------------|-------------|----------------|

| V <sub>SPICLKFREQ</sub> ≥ V <sub>CLKTH4</sub>                       | 1111        | 250 kHz        |

|                                                                     | 1110        | 250 kHz        |

|                                                                     | 1101        | 250 kHz        |

|                                                                     | 1100        | 250 kHz        |

| Circuit malfunction                                                 | 1011        | 250 kHz        |

|                                                                     | 1010        | 250 kHz        |

|                                                                     | 1001        | 250 kHz        |

|                                                                     | 1000        | 250 kHz        |

| V <sub>CLKTH3</sub> ≤ V <sub>SPICLKFREQ</sub> < V <sub>CLKTH4</sub> | 0111        | 8 MHz          |

| O'considerate Manager and Constant                                  | 0110        | 250 kHz        |

| Circuit malfunction                                                 | 0101        | 250 kHz        |

DS13590 - Rev 1 page 17/46

| V <sub>SPICLKFREQ</sub> [V] (typ.)                                  | Vcode [3:0] | SCLK Frequency |

|---------------------------------------------------------------------|-------------|----------------|

| Circuit malfunction                                                 | 0100        | 250 kHz        |

| V <sub>CLKTH2</sub> ≤ V <sub>SPICLKFREQ</sub> < V <sub>CLKTH3</sub> | 0011        | 4 MHz          |

| Circuit malfunction                                                 | 0010        | 250 kHz        |

| V <sub>CLKTH1</sub> ≤ V <sub>SPICLKFREQ</sub> < V <sub>CLKTH2</sub> | 0001        | 1 MHz          |

| V <sub>SPICLKFREQ</sub> < V <sub>CLKTH1</sub>                       | 0000        | 250 kHz        |

Refer to Table 15 for the recommended selection of the external pull down resistor.

Table 15. Recommended components for SPI clock frequency selection in master mode

| SCLK Frequency | Recommended R <sub>SPICLKFREQ</sub> [kΩ] | R <sub>SPICLKFREQ</sub> Tolerance [%] |

|----------------|------------------------------------------|---------------------------------------|

| 250 kHz        | Short to GND                             | -                                     |

| 1 MHz          | 9.31                                     | 10                                    |

| 4 MHz          | 16.2                                     | 5                                     |

| 8 MHz          | 22.9                                     | 1                                     |

The 4 analog comparators are BISTed during **Trimming & Config Latch** and, in case the BIST fails, the slowest SCLK configuration is chosen (250 kHz).

MCU is supposed to implement a communication timeout mechanism able to detect slower than normal communication bitrate.

The biasing current ISPICLKFREQPU, the comparators and voltage divider are disabled once **Trimming & Config Latch** is left, in order to avoid unnecessary power consumption.

V3V3 MAIN ISPICLKFREQPU V3V3\_MAIN  $R_{\text{DIV}}$ V3V3 MAIN Vcode [3] QΒ QΒ R<sub>DIV</sub> V3V3 MAIN D **STBY** Vcode [2] QΒ V3V3 MAIN RDIV LOGIC ΕN QΒ Vcode [1] QΒ V3V3\_MAIN\_ RDIV Vcode [0] R<sub>DIV</sub>

**▽**GND

Figure 11. SPICLKFREQ pin structure

DS13590 - Rev 1 page 18/46

## 3.2.2.2 Electrical parameters - Analog input

All parameters are tested and guaranteed in the following conditions, unless otherwise specified:  $4.5 \text{ V} \leq V_{VDD} \leq 5.5 \text{ V}$ ; -40 °C < Tj < 125 °C

Table 16. Analog input electrical characteristics

| Symbol                    | Parameters                                                            | Test conditions                          | Min   | Тур  | Max   | Unit |

|---------------------------|-----------------------------------------------------------------------|------------------------------------------|-------|------|-------|------|

| V <sub>CLKTH4</sub>       | Input Voltage Thresold                                                | Ramp on SPICLKFREQ                       | -2.5% | 2.64 | +2.5% | V    |

| V <sub>CLKTH3</sub>       | Input Voltage Thresold                                                | Ramp on SPICLKFREQ                       | -2.5% | 1.98 | +2.5% | V    |

| V <sub>CLKTH2</sub>       | Input Voltage Thresold                                                | Ramp on SPICLKFREQ                       | -3%   | 1.32 | +3%   | V    |

| V <sub>CLKTH1</sub>       | Input Voltage Thresold                                                | Ramp on SPICLKFREQ                       | -7%   | 0.66 | +7%   | V    |

| I <sub>SPICLKFREQPU</sub> | Bias current on SPICLKFREQ, active only in<br>Trimming & Config Latch | 0.75 V < V <sub>SPICLKFREQ</sub> < 2.5 V | -11%  | 100  | +11%  | μA   |

DS13590 - Rev 1 page 19/46

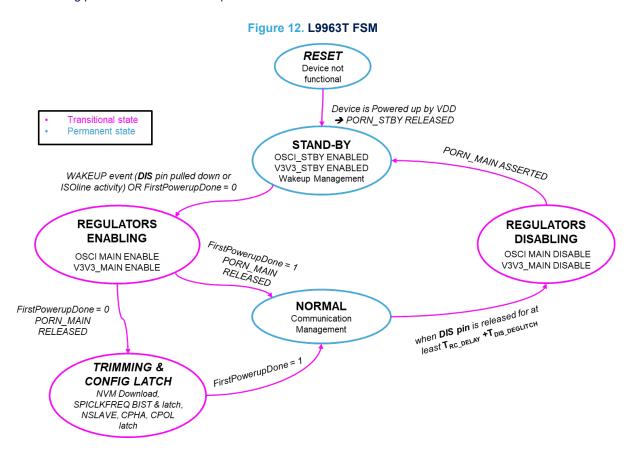

#### 3.3 Device functional states

#### 3.3.1 L9963T FSM

The following picture shows all L9963T possible states.

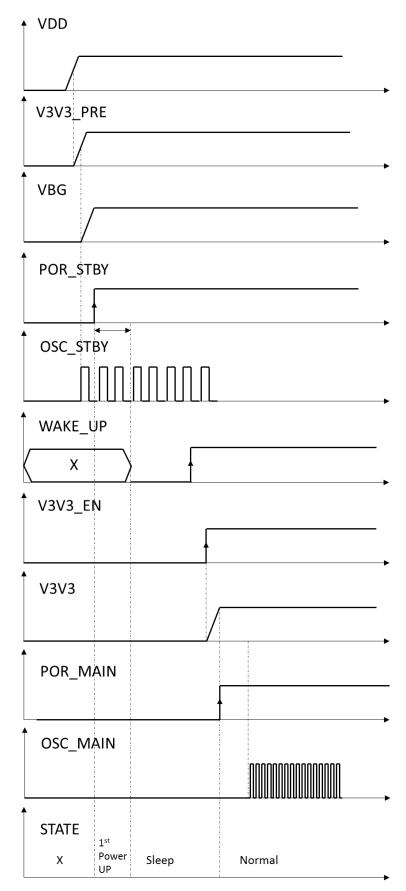

Different state transition sequences occur according to the following different scenarios:

- First power up: Reset state → Stand-by state → Regulators enabling state → Trimming & Config Latch → Normal state (see Figure 13). The first power up sequence lasts T<sub>FIRST POWERUP</sub>.

- Wake up: Stand-by state → Regulators enabling state → Normal state. See Figure 14 for an example of wake up sequence triggered by a frame received on the vertical interface. In case of wake up triggered by DIS release, the state transition is the same. The wake up sequence lasts T<sub>WAKEUP</sub>.

- Go To Sleep: Normal state  $\rightarrow$  Regulators disabling state  $\rightarrow$  Stand-by state. The go to sleep sequence lasts  $T_{GO2SLP}$ .

DS13590 - Rev 1 page 20/46

DS13590 - Rev 1 page 21/46

Figure 14. Wake up sequence

#### 3.3.2 Reset state

When VDD is below the value triggering the power up, the device is not functional. No operation is possible while under reset.

### 3.3.3 Stand-by state

This state is entered either from Reset state or from Regulators disabling state:

- Transition from Regulators disabling state only occurs upon DIS low → high transition while L9963T is in Normal state. DIS input signal is filtered in both analog (T<sub>RC\_DELAY</sub>) and digital (T<sub>DIS\_DEGLITCH</sub>) domains.

- Transition from Reset state only occurs upon first power up, after POR\_STBY release.

While in standby, the logic checks the FirstPowerupDone latch, whose reset value is '0' upon first power up:

- In case **FirstPowerupDone = 0**, the first power up has never been accomplished. Hence, the device moves to **Regulators enabling state**, regardless of any wake up source state.

- In case **FirstPowerupDone = 1**, the first power up has already been accomplished. Hence, the device is kept in **Stand-by state** and eventual transitions are determined by the wake up sources.

When a wake up source is asserted, it triggers the wake up sequence that will move L9963 to **Regulators enabling state**. The possible wakeup sources are:

- The deassertion of DIS pin, pulled down by an external open drain source (T<sub>RC\_DELAY</sub> + (1/ f<sub>STBY\_OSC</sub>) filter applies).

- The detection of at least N<sub>MIN\_ISO\_WUP\_EDGES</sub> pulses within T<sub>WAKEUP\_TIMEOUT\_ISO</sub> on the ISOline.

### 3.3.4 Regulators enabling state

This is a transitional state reached from **Stand-by state**.

While L9963T is in this state, it enables the V3V3 regulator and the OSCI\_MAIN.

During this process lasting  $T_{WAKEUP}$  the device must not be sensitive to **DIS** pin, SPI interface and ISOline sources. Once a wake up sequence is started, it cannot be interrupted.

DS13590 - Rev 1 page 22/46

The **Regulators enabling state** is left upon POR\_MAIN release. Next state depends on **FirstPowerupDone** latch:

- In case FirstPowerupDone = 0, the first power up has never been accomplished. Hence, the device moves toTrimming & Config Latch.