TLK2711-SP

ZHCSHO9P - JULY 2006-REVISED FEBRUARY 2018

# TLK2711-SP 1.6Gbps 至 2.5Gbps V 类收发器

### 1 特性

- 1.6Gbps 至 2.5Gbps (千兆位/秒) 串行器/解串器

- 热插拔保护

- 高性能 68 引脚陶瓷四方扁平封装 (HFG)

- 低功耗操作

- 串行输出上的可编程预加重水平

- 连接到背板、铜电缆或光学转换器的接口

- 片上 8 位/10 位编码/解码、逗点检测

- 片上 PLL 利用低速参考提供时钟合成

- 低功耗: < 500mW

- 并行数据输入信号上的 3-V 容差

- 16 位并行 TTL 兼容数据接口

- 高速背板互连和点对点数据链路的理想之选

- 军用级温度范围(-55°C 至 125°C case)

- 信号损失 (LOS) 检测

- RX 上的集成 50Ω 终端电阻器

- 可提供工程评估 (/EM) 样品 (1)

### 2 应用

- 点对点高速 I/O

- 数据采集

- 数据处理

### 3 说明

TLK2711-SP 属于数千兆位收发器的 WizardLink 收发器系列,专用于超高速双向点对点数据传输系统。

TLK2711-SP 支持 1.6Gbps 至 2.5Gbps 的有效串行接口速度,可提供高达

#### 2Gbps 的数据带宽。

(1) 这些部件只用于工程评估。以非合规性流程对其进行了处理 (例如,未进行老化处理等操作),并且仅在 25°C 的额定温 度下进行了测试。这些部件不适用于质检、生产、辐射测试或 飞行。这些零部件无法在 -55°C 至 125°C 的完整 MIL 额定温 度范围内或运行寿命中保证其性能。 TLK2711-SP 的主要应用是,通过约 50Ω 的控制阻抗介质针对点对点基带数据传输提供高速 I/O 数据通道。传输介质可以是印刷电路板、铜缆或光纤电缆。数据传输的最大速率和距离取决于介质的衰减特性和环境的噪声耦合。

### 器件信息(1)

| 器件型号       | 封装       | 封装尺寸(标称值)         |

|------------|----------|-------------------|

| TLK2711-SP | CFP (68) | 13.97mm × 13.97mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

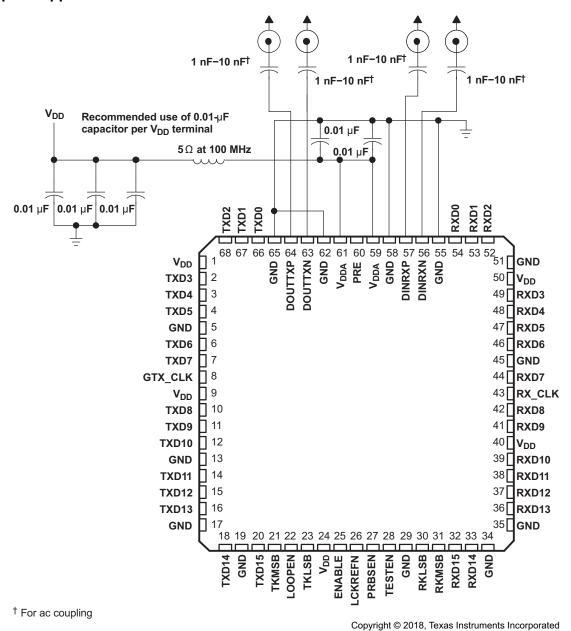

#### 外部组件互连

Зорун

|   | 月                                                     | 录  |                                |    |

|---|-------------------------------------------------------|----|--------------------------------|----|

| 1 | 特性                                                    |    | 8.2 Functional Block Diagram   | 13 |

| 2 | 应用 1                                                  |    | 8.3 Feature Description        | 14 |

| 3 | 说明 1                                                  |    | 8.4 Device Functional Modes    | 20 |

| 4 | 修订历史记录 2                                              | 9  | Application and Implementation | 21 |

| 5 | 说明(续)4                                                |    | 9.1 Application Information    | 21 |

| 6 | Pin Configuration and Functions                       |    | 9.2 Typical Application        | 22 |

| 7 | Specifications                                        | 10 | 0 Power Supply Recommendations | 24 |

| ′ | 7.1 Absolute Maximum Ratings                          | 11 | 1 Layout                       | 24 |

|   | 7.1 Absolute Maximum Ratings                          |    | 11.1 Layout Guidelines         | 24 |

|   | 7.3 Recommended Operating Conditions8                 |    | 11.2 Layout Example            | 24 |

|   | 7.4 Thermal Information                               | 12 | marks at 1 to 1 to 1 to        |    |

|   | 7.5 TTL Input Electrical Characteristics              |    | 12.1 接收文档更新通知                  | 25 |

|   | 7.6 Transmitter/Receiver Electrical Characteristics 9 |    | 12.2 社区资源                      | 25 |

|   | 7.7 Reference Clock (TXCLK) Timing Requirements 10    |    | 12.3 商标                        | 25 |

|   | 7.8 TTL Output Switching Characteristics              |    | 12.4 静电放电警告                    | 25 |

|   | 7.9 Typical Characteristics                           |    | 12.5 Glossary                  | 25 |

| Q | Detailed Description 13                               | 13 | <b>3</b> 机械、封装和可订购信息           | 25 |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Changes from Revision O (March 2016) to Revision P                                                                                                                                              | Page         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| <ul> <li>Changed column header of Table 4 indicating correct order of receive data bus bits</li> <li>已添加 接收文档更新通知 部分</li> </ul>                                                                 |              |

| Changes from Revision N (December 2015) to Revision O                                                                                                                                           | Page         |

| Changed reference to table note (2) Internal 10-kΩ pulldown for TKLSB and TKMSB                                                                                                                 | 6            |

| Changes from Revision M (October 2014) to Revision N                                                                                                                                            | Page         |

| <ul> <li>Updated the frequency range of TXCLK</li> <li>Updated Handling Ratings table to an ESD Ratings table and moved T<sub>stg</sub> to the Absolute Maximum Rating       添加了社区资源</li> </ul> | atings table |

| Changes from Revision L (August 2014) to Revision M                                                                                                                                             | Page         |

| Updated Power-On Reset description     Removed option 2 from Power-On Reset                                                                                                                     |              |

| Changes from Revision K (July 2014) to Revision L                                                                                                                                               | Page         |

| Updated Power-On/Reset Timing Diagram options                                                                                                                                                   | 19           |

| Changes from Revision J (May 2014) to Revision K                                            | Page |

|---------------------------------------------------------------------------------------------|------|

| Updated pin description for ENABLE                                                          | 5    |

| Updated pin voltages in Absolute Maximum Ratings                                            | 7    |

| Added more information to <i>Power-On Reset</i> detailing two power-on/reset timing options | 18   |

| Changes from Revision I (January 2014) to Revision J                                        | Page |

| • 已更改格式符合最新的数据表标准;添加了新的部分并移动了现有部分                                                           |      |

| • 己更改 说明                                                                                    | 4    |

| • 己更改 有关 LCKREFN 的段落: <i>说明 (续)</i>                                                         |      |

| Changed Description of LCKREFN in                                                           | 5    |

| Changed Power-On Reset section                                                              | 18   |

| Changes from Revision H (December 2013) to Revision I                                       | Page |

| • 已添加 将 /EM 列表项添加到了特性                                                                       | 1    |

| Deleted Ordering Information table                                                          | 13   |

### 5 说明 (续)

该器件还可通过减少线迹、连接器引脚和发送/接收引脚的数量,来取代并行数据传输架构。加载到发送器的并行数据通过串行通道传送到接收器,串行通道可以是同轴铜缆、控制阻抗背板或光纤链路。然后将其重构为其原始并行格式。与并行解决方案相比,它可以节省大量的功耗和成本,并且可以面向未来提供可扩展性,以提高数据速率。

TLK2711-SP 可执行并行至串行和串行至并行的数据转换。时钟提取充当物理层 (PHY) 接口器件。串行收发器接口的最高速度为 2.5Gbps。发送器以基于所提供的参考时钟 (TXCLK) 的速率锁存 16 位并行数据。使用 8 位/10 位 (8b/10b) 编码格式将 16 位并行数据内部编码为 20 位。然后以 20 倍的参考时钟 (TXCLK) 速率以差动方式发送所生成的 20 位字。接收器部分对输入数据执行串行至并行转换,将产生的 20 位宽的并行数据同步到恢复时钟 (RXCLK)。然后它使用 8 位/10 位解码格式解码 20 位宽数据,从而在接收数据引脚 (RXD0-RXD15) 产生 16 位的并行数据。结果产生 1.28Gbps 至 2Gbps(16 位数据 × 频率)的有效数据负载。

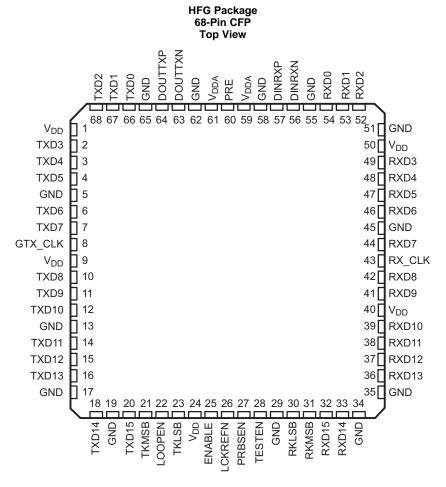

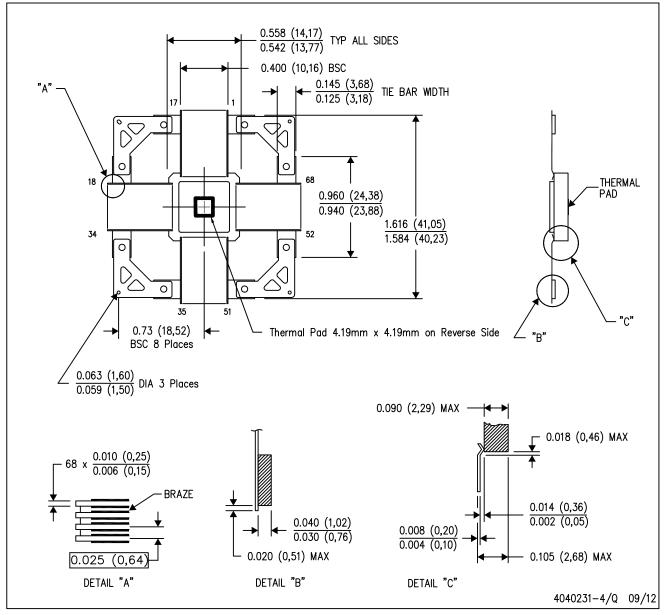

TLK2711-SP 采用 68 引脚陶瓷非导电连接杆封装 (HFG)。

注

商业 TLK2711 器件中所示的名为 *TLK2711、1.6GBPS 至 2.7GBPS 收发器数据表 – PLL* 错误锁定问题勘误表不适用于 TLK2711-SP 器件。TLK2711-SP 在功能上等同于 TLK2711A 商用器件。

TLK2711-SP 提供了用于自测用途的内部回送功能。来自串行器的串行数据直接传递给解串器,为协议器件提供对物理接口的功能性自检。

TLK2711-SP 有一个 LOS 检测电路,用于传入信号不再具有足够的电压幅度以确保时钟恢复电路处于锁定状态的情况。

TLK2711-SP 通过将来自两个 TLK2711-SP 器件的接收数据总线引脚连接在一起,从而允许用户实施冗余端口。如果启用器件 (ENABLE = H),则将 LCKREFN 激活至低电平状态会导致接收数据总线引脚(RXD0 - RXD15、RXCLK、RKLSB 和 RKMSB)进入高阻抗状态。这样会将器件置于仅发送模式,因为接收器未跟踪数据。在上电复位期间必须将 LCKREFN 取消置位为高电平状态(请参阅上电复位部分)。如果器件已被禁用 (ENABLE = L),则 RKMSB 将输出 LOS 检测器的状态(低电平有效 = LOS)。所有其他接收输出均将保持高阻抗状态。

TLK2711-SP I/O 为 3V 兼容。TLK2711-SP 可在 -55°C 至 125° 的 C case 温度下正常运行。

TLK2711-SP 设计为支持热插拔。片上上电复位电路将 RXCLK 保持为低电平,并在通电期间在并行端输出信号引脚以及 TXP 和 TXN 上变为高阻抗状态。

### 6 Pin Configuration and Functions

### **Pin Functions**

| PIN                |                                                            | 1/0              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|--------------------|------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME               | NO.                                                        | 1/0              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DOUTTXN<br>DOUTTXP | 63<br>64                                                   | 0                | Serial transmit outputs. TXP and TXN are differential serial outputs that interface to copper or an optical I/F module. These pins transmit NRZ data at a rate of 20x the TXCLK value. TXP and TXN are put in a high-impedance state when LOOPEN is high and are active when LOOPEN is low. During power-on reset, these pins are high impedance.                                                                                                                                                                               |  |

| ENABLE             | 25                                                         | J(1)             | evice enable. When this pin is held low, the device is placed in power-down mode. Only the signal etect circuit on the serial receive pair is active. When in power-down mode, RKMSB will output the eatus of signal detect circuit (LOS). When asserted high while the device is in power-down mode, we transceiver is reset before beginning normal operation.                                                                                                                                                                |  |

| GND                | 5, 13, 17, 19,<br>29, 34, 35,<br>45, 51, 55,<br>58, 62, 65 | _                | Analog and digital logic ground. Provides a ground for the logic circuits, digital I/O buffers, and the high-speed analog circuits.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| LCKREFN            | 26                                                         | I <sup>(1)</sup> | Lock to reference. When LCKREFN is low, the receiver clock is frequency locked to TXCLK. This places the device in a transmit-only mode since the receiver is not tracking the data. When LCKREFN is asserted low, the receive data bus pins (RXD0 through RXD15, RXCLK, RKLSB, and RKMSB) are in a high-impedance state if device is enabled (ENABLE = H). If device is disabled (ENABLE = L), then RKMSB will output the status of the LOS detector (active low = LOS). All other receive outputs will remain high-impedance. |  |

|                    |                                                            |                  | When LCKREFN is deasserted high, the receiver is locked to the received data stream. LCKREFN must be deasserted to a high state during power-on reset. See <i>Power-On Reset</i> .                                                                                                                                                                                                                                                                                                                                              |  |

### (1) Internal 10-kΩ pullup.

### Pin Functions (continued)

| P                                                                                                                                           | riN                                                                                          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                                                                                                        | NO.                                                                                          | 1/0              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| LOOPEN                                                                                                                                      | 22                                                                                           | J <sup>(2)</sup> | Loop enable. When LOOPEN is active high, the internal loopback path is activated. The transmitted serial data is directly routed internally to the inputs of the receiver. This provides a self-test capability in conjunction with the protocol device. The TXP and TXN outputs are held in a high-impedance state during the loopback test. LOOPEN is held low during standard operational state, with external serial outputs and inputs active.                          |  |  |

| PRE                                                                                                                                         | 60                                                                                           | I <sup>(2)</sup> | Preemphasis control. Selects the amount of preemphasis to be added to the high-speed serial output drivers. Left low or unconnected, 5% preemphasis is added. Pulled high, 20% preemphasis is added.                                                                                                                                                                                                                                                                         |  |  |

| PRBSEN                                                                                                                                      | 27                                                                                           | I <sup>(2)</sup> | PRBS test enable. When asserted high, results of pseudo-random bit stream (PRBS) tests can be monitored on the RKLSB pin. A high on RKLSB indicates that valid PRBS is being received.                                                                                                                                                                                                                                                                                       |  |  |

| RKLSB                                                                                                                                       | 30                                                                                           | 0                | K-code indicator/PRBS test results. When RKLSB is asserted high, an 8-bit/10-bit K code was received and is indicated by data bits RXD0 through RXD7. When RKLSB is asserted low, an 8-bit/10-bit D code is received and is presented on data bits RXD0 through RXD7. When PRBSEN is asserted high, this pin is used to indicate status of the PRBS test results (high = pass).                                                                                              |  |  |

| RKMSB                                                                                                                                       | 31                                                                                           | 0                | K-code indicator. When RKMSB is asserted high an 8-bit/10-bit K code was received and is indicated by data bits RXD8 through RXD15. When RKMSB is asserted low an 8-bit/10-bit D code was received and is presented on data bits RXD8 through RXD15. If the differential signal on RXN and RXP drops below 200 mV, RXD0–RXD15, RKLSB, and RKMSB are all asserted high. When device is disabled (ENABLE = L), RKMSB will output the status of LOS. Active low = LOS detected. |  |  |

| RXCLK<br>RX_CLK                                                                                                                             | 43                                                                                           | 0                | Recovered clock. Output clock that is synchronized to RXD0 through RXD9, RKLSB, and RKMSB. RXCLK is the recovered serial data rate clock divided by 20. RXCLK is held low during power-on reset.                                                                                                                                                                                                                                                                             |  |  |

| RXD0<br>RXD1<br>RXD2<br>RXD3<br>RXD4<br>RXD5<br>RXD6<br>RXD7<br>RXD8<br>RXD9<br>RXD10<br>RXD11<br>RXD12<br>RXD12<br>RXD13<br>RXD14<br>RXD15 | 54<br>53<br>52<br>49<br>48<br>47<br>46<br>44<br>42<br>41<br>39<br>38<br>37<br>36<br>33<br>32 | 0                | Receive data bus. These outputs carry 16-bit parallel data output from the transceiver to the protocol device, synchronized to RXCLK. The data is valid on the rising edge of RXCLK as shown in Figure 10. These pins are in high-impedance state during power-on reset.                                                                                                                                                                                                     |  |  |

| DINRXN<br>DINRXP                                                                                                                            | 56<br>57                                                                                     | I                | Serial receive inputs. RXP and RXN together are the differential serial input interface from a copper or an optical I/F module.                                                                                                                                                                                                                                                                                                                                              |  |  |

| TESTEN                                                                                                                                      | 28                                                                                           | I <sup>(2)</sup> | Test mode enable. This pin should be left unconnected or tied low.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| TKLSB                                                                                                                                       | 23                                                                                           | I <sup>(2)</sup> | K-code generator (LSB). When TKLSB is high, an 8-bit/10-bit K code is transmitted as controlled by data bits TXD0 through TXD7. When TKLSB is low, an 8-bit/10-bit D code is transmitted as controlled by data bits TXD0 through TXD7.                                                                                                                                                                                                                                       |  |  |

| TKMSB                                                                                                                                       | 21                                                                                           | I <sup>(2)</sup> | K-code generator (MSB). When TKMSB is high, an 8-bit/10-bit K code is transmitted as controlled by data bits TXD8 through TXD15. When TKMSB is low, an 8-bit/10-bit D code is transmitted as controlled by data bits TXD8 through TXD15.                                                                                                                                                                                                                                     |  |  |

| TXCLK<br>GTX_CLK                                                                                                                            | 8                                                                                            | I                | Reference clock. TXCLK is a continuous external input clock that synchronizes the transmitter interface signals TKMSB, TKLSB, and TXD0–TXD15. The frequency range of TXCLK is 80 to 125 MHz. The transmitter uses the rising edge of this clock to register the 16-bit input data TXD0 through TXD15 for serialization.                                                                                                                                                      |  |  |

<sup>(2)</sup> Internal 10-k $\Omega$  pulldown.

#### Pin Functions (continued)

| PIN   |                     | 1/0 | DESCRIPTION                                                                                                                                                                                                |  |  |  |  |

|-------|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME  | NO.                 | 1/0 | DESCRIPTION                                                                                                                                                                                                |  |  |  |  |

| TXD0  | 66                  |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD1  | 67                  |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD2  | 68                  |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD3  | 2                   |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD4  | 3                   |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD5  | 4                   |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD6  | 6                   |     | ransmit data bus. These inputs carry the 16-bit parallel data output from a protocol device to the                                                                                                         |  |  |  |  |

| TXD7  | 7                   |     | ransmit data bus. These inputs carry the 16-bit parallel data output from a protocol device to the ransceiver for encoding, serialization, and transmission. This 16-bit parallel data is clocked into the |  |  |  |  |

| TXD8  | 10                  | '   |                                                                                                                                                                                                            |  |  |  |  |

| TXD9  | 11                  |     | ransceiver on the rising edge of TXCLK as shown in Figure 7.                                                                                                                                               |  |  |  |  |

| TXD10 | 12                  |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD11 | 14                  |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD12 | 15                  |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD13 | 16                  |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD14 | 18                  |     |                                                                                                                                                                                                            |  |  |  |  |

| TXD15 | 20                  |     |                                                                                                                                                                                                            |  |  |  |  |

| VDD   | 1, 9, 24, 40,<br>50 |     | Digital logic power. Provides power for all digital circuitry and digital I/O buffers.                                                                                                                     |  |  |  |  |

| VDDA  | 59, 61              |     | Analog power. VDDA provides a supply reference for the high-speed analog circuits, receiver, and transmitter.                                                                                              |  |  |  |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating temperature (unless otherwise noted)(1)

|                  |                                                                          |                                                                                  | MIN   | MAX              | UNIT  |

|------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------|------------------|-------|

| $V_{DD}$         | Supply voltage (2)                                                       |                                                                                  | -0.3  | 3                | V     |

|                  | Voltage                                                                  | TXD0 to TXD15, ENABLE, TXCLK, TKMSB, TKLSB, LOOPEN, PRBSEN, LCKREFN, PRE, TESTEN | -0.3  | 4                |       |

|                  |                                                                          | RXD0 to RXD15, RKMSB, RKLSB, RXCLK                                               | -0.3  | $V_{DD} + 0.35$  | V     |

|                  |                                                                          | DINRXP, DINRXN, DOUTTXP, DOUTTXN                                                 | -0.35 | $V_{DDA} + 0.35$ |       |

|                  | Maximum cumulative exposure of unpowered receiver to external inputs (3) |                                                                                  |       | 10               | hours |

| T <sub>C</sub>   | T <sub>C</sub> Characterized case operating temperature                  |                                                                                  | -55   | 125              | °C    |

| T <sub>stg</sub> | Storage temperature                                                      | •                                                                                | -65   | 150              | °C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                         |                                                                             | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> All voltage values, except differential I/O bus voltages, are stated with respect to network ground.

<sup>(3)</sup> The TLK2711-SP shows no performance degradation when an external powered transmitter sends a signal to an unpowered receiver for short periods of time (up to 10 hours of lifetime of the device). Characterization was performed using maximum V<sub>OD</sub>, minimum frequency and typical V<sub>CM</sub> from recommended operating conditions for the specified period of time.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                            |                                                       | MIN   | NOM  | MAX   | UNIT |  |

|----------------|----------------------------|-------------------------------------------------------|-------|------|-------|------|--|

| V              | O contributed to the       | Frequency range 1.6 Gbps to 2 Gbps                    | 2.375 | 2.5  | 2.625 | V    |  |

| $V_{DD}$       | Supply voltage             | Frequency range 1.6 Gbps to 2.5 Gbps                  | 2.5   | 2.6  | 2.7   | V    |  |

|                | Complex company            | Frequency = 1.6 Gbps, PRBS pattern                    |       | 110  |       |      |  |

| ICC            | Supply current             | Frequency = 2.5 Gbps, PRBS pattern                    |       | 160  |       | mA   |  |

|                | Power dissipation          | Frequency = 1.6 Gbps, PRBS pattern                    |       | 275  |       |      |  |

| $P_D$          |                            | Frequency = 2.5 Gbps, PRBS pattern                    |       | 400  |       | mW   |  |

|                |                            | Frequency = 2.5 Gbps, PRBS pattern                    |       |      | 550   |      |  |

|                | Shutdown current           | Enable = 0, $V_{DDA}$ , $V_{DD}$ pins, $V_{DD}$ = MAX |       | 3    |       | mA   |  |

|                | PLL startup lock time      | V <sub>DD</sub> , V <sub>DDC</sub> = 2.375 V          |       | 0.1  | 0.4   | ms   |  |

|                | Data acquisition time      |                                                       |       | 1024 |       | bits |  |

| T <sub>c</sub> | Operating case temperature |                                                       | -55   |      | 125   | °C   |  |

#### 7.4 Thermal Information

see (1)

|                 |                                        | TLK2711-SP |      |

|-----------------|----------------------------------------|------------|------|

|                 | THERMAL METRIC <sup>(2)</sup>          | HFG (CFP)  | UNIT |

|                 |                                        | 68 PINS    |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance | 31.5       | °C/W |

| $R_{\theta JC}$ | Junction-to-case thermal resistance    | 2.96       | °C/W |

- (1) This CFP package has built-in vias that electrically and thermally connect the bottom of the die to a pad on the bottom of the package. To efficiently remove heat and provide a low-impedance ground path, a thermal land is required on the surface of the PCB directly underneath the body of the package. During normal surface mount flow solder operations, the heat pad on the underside of the package is soldered to this thermal land creating an efficient thermal path. Normally, the PCB thermal land has a number of thermal vias within it that provide a thermal path to internal copper areas (or to the opposite side of the PCB) that provide for more efficient heat removal. TI typically recommends an 11.9-mm x 11.9-mm board-mount thermal pad with a 4.2-mm x 4.2-mm solder mask defined pad attach opening. This allows maximum area for thermal dissipation, while allowing leads pad to solder pad clearance. A sufficient quantity of thermal or electrical vias must be included to keep the device within *Recommended Operating Conditions*. This pad must be electrically ground potential.

- (2) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 7.5 TTL Input Electrical Characteristics

over recommended operating conditions (unless otherwise noted),

TTL signals: TXD0-TXD15, TXCLK, LOOPEN, LCKREFN, ENABLE, PRBS\_EN, TKLSB, TKMSB, PRE

|                 | PARAMETER                                     | TEST CONDITIONS                         | MIN | TYP      | MAX | UNIT |

|-----------------|-----------------------------------------------|-----------------------------------------|-----|----------|-----|------|

| $V_{IH}$        | High-level input voltage                      | See Figure 1                            | 1.7 |          |     | V    |

| $V_{IL}$        | Low-level input voltage                       | See Figure 1                            |     |          | 8.0 | V    |

| I <sub>IH</sub> | Input high current                            | $V_{DD} = MAX, V_{IN} = 2 V$            |     |          | 40  | μΑ   |

| $I_{\rm IL}$    | Input low current                             | $V_{DD} = MAX$ , $V_{IN} = 0.4 V$       | -40 |          |     | μA   |

| $C_{l}$         | Receiver input capacitance                    |                                         |     | 6        |     | pF   |

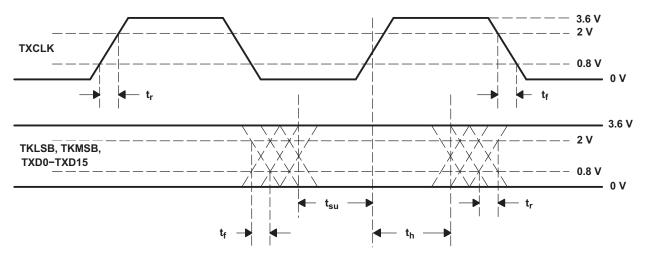

| t <sub>r</sub>  | Rise time, TXCLK, TKMSB, TKLSB, TXD0 to TXD15 | 0.7 to 1.9 V, C = 5 pF,<br>See Figure 1 |     | 1        |     | ns   |

| t <sub>f</sub>  | Fall time, TXCLK, TKMSB, TKLSB, TXD0 to TXD15 | 1.9 to 0.7 V, C = 5 pF,<br>See Figure 1 |     | 1        |     | ns   |

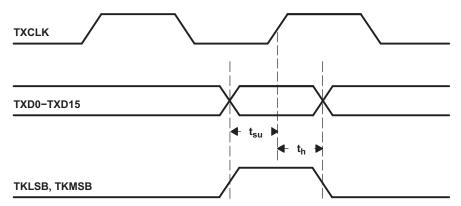

| t <sub>su</sub> | TXD0 to TXD15, TKMSB, TKLSB setup to ↑ TXCLK  | See Figure 1 <sup>(1)</sup>             | 1.5 |          |     | ns   |

| t <sub>h</sub>  | TXD, TKMSB, TKLSB hold to ↑ TXCLKS            | See Figure 1 <sup>(1)</sup>             | 0.4 | <u>'</u> |     | ns   |

(1) Nonproduction tested parameters.

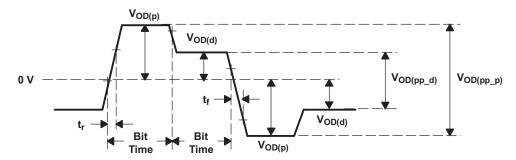

# 7.6 Transmitter/Receiver Electrical Characteristics

|                                 | PARAMETER                                                                      | TEST CONDITIONS                                                                                 | MIN  | TYP  | MAX  | UNIT              |  |

|---------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------------------|--|

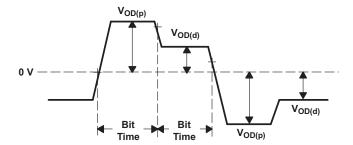

| \/                              | Preemphasis VOD, direct,                                                       | Rt = 50 $\Omega$ , PREM = high, DC coupled, see Figure 3                                        | 655  | 800  | 1100 | mV                |  |

| $V_{OD(p)}$                     | $V_{OD(p)} =  VTXP - VTXN $                                                    | Rt = 50 $\Omega$ , PREM = low, DC coupled, see Figure 3                                         | 590  | 740  | 1050 |                   |  |

| V                               | Differential, peak-to-peak output voltage with                                 | Rt = 50 $\Omega$ , PREM = high, DC coupled, see Figure 3                                        | 1310 | 1600 | 2200 | mV <sub>p-p</sub> |  |

| $V_{OD(pp\_p)}$                 | preemphasis                                                                    | Rt = 50 $\Omega$ , PREM = low, DC coupled, see Figure 3                                         | 1180 | 1480 | 2100 |                   |  |

| V <sub>OD(d)</sub>              | Deemphais output voltage,<br> V <sub>TXP</sub> - V <sub>TXN</sub>              | Rt = 50 Ω, DC coupled, see Figure 3                                                             | 540  | 650  | 950  | mV                |  |

| $V_{OD(pp\_d)}$                 | Differential, peak-to-peak output voltage with deemphasis                      | Rt = 50 $\Omega$ , DC coupled, see Figure 3                                                     | 1080 | 1300 | 1900 | $mV_{p-p}$        |  |

| V <sub>(cmt)</sub>              | Transmit common mode voltage range, (V <sub>TXP</sub> + V <sub>TXN</sub> ) / 2 | Rt = 50 $\Omega$ , see Figure 3                                                                 | 1000 | 1250 | 1450 | mV                |  |

| V <sub>ID</sub>                 | Receiver input voltage differential,  V <sub>RXP</sub> - V <sub>RXN</sub>      | See (1)                                                                                         | 220  |      | 1600 | mV                |  |

| V <sub>(cmr)</sub>              | Receiver common mode voltage range, (V <sub>RXP</sub> + V <sub>RXN</sub> ) / 2 | See (1)                                                                                         | 1000 | 1250 | 2250 | mV                |  |

| I <sub>lkg</sub>                | Receiver input leakage current                                                 |                                                                                                 | -10  |      | 10   | μΑ                |  |

| Cı                              | Receiver input capacitance                                                     |                                                                                                 |      | 4    |      | pF                |  |

|                                 | 0                                                                              | Differential output jitter at 2.5 Gbps,<br>Random + deterministic, PRBS pattern                 |      | 0.28 |      | UI <sup>(2)</sup> |  |

|                                 | Serial data total jitter (peak to peak)                                        | Differential output jitter at 1.6 Gbps,<br>Random + deterministic, PRBS pattern                 |      | 0.32 |      | UI\-              |  |

| t <sub>t</sub> , t <sub>f</sub> | Differential output signal rise, fall time (20% to 80%)                        | RL = 50 $\Omega$ , CL = 5 pF, see Figure 3                                                      |      | 150  |      | ps                |  |

|                                 | Jitter tolerance eye closure                                                   | Differential input jitter, random + deterministic, PRBS pattern at zero crossing <sup>(1)</sup> | 0.4  |      |      | UI                |  |

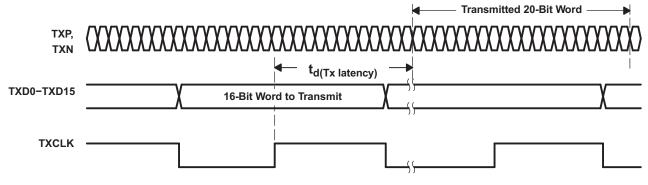

| t <sub>d(Tx latency)</sub>      | Tx latency                                                                     | See Figure 8                                                                                    | 34   |      | 38   | bits              |  |

| t <sub>d(Rx latency)</sub>      | Rx latency                                                                     | See Figure 11                                                                                   | 76   |      | 107  | bits              |  |

<sup>(1)</sup> Nonproduction tested parameters.(2) UI is the time interval of one serialized bit.

### 7.7 Reference Clock (TXCLK) Timing Requirements

over recommended operating conditions (unless otherwise noted)

| PARAMETER           | TEST CONDITIONS         | MIN  | NOM | MAX | UNIT |

|---------------------|-------------------------|------|-----|-----|------|

| Frequency           | Receiver data rate / 20 | -100 |     | 100 | ppm  |

| Frequency tolerance |                         | -100 |     | 100 | ppm  |

| Duty cycle          |                         | 40%  | 50% | 60% |      |

| Jitter              | Peak to peak            |      |     | 40  | ps   |

### 7.8 TTL Output Switching Characteristics

over recommended operating conditions (unless otherwise noted)

|                 | PARAMETER                                                            | TEST CONDITIONS                                                                                  | MIN       | TYP  | MAX | UNIT |

|-----------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------|------|-----|------|

| V <sub>OH</sub> | High-level output voltage                                            | $I_{OH} = -2 \text{ mA}, V_{DD} = \text{MIN}$                                                    | 2.1       | 2.3  |     | V    |

| $V_{OL}$        | Low-level output voltage                                             | $I_{OL} = 2 \text{ mA}, V_{DD} = \text{MIN}$                                                     |           | 0.25 | 0.5 | V    |

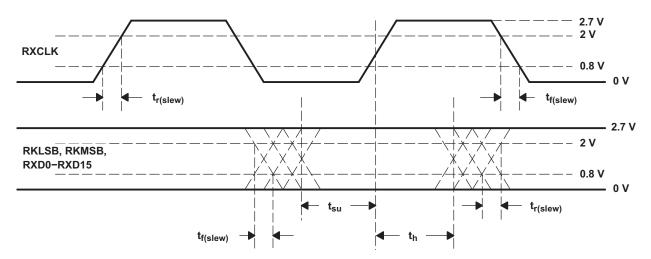

| $t_{r(slew)}$   | Slew rate (rising), magnitude of RXCLK, RKLSB, RKMSB, RXD0 to RXD15  | 0.8 V to 2 V, C = 5 pF, see Figure 2                                                             | 0.5       |      |     | V/ns |

| $t_{f(slew)}$   | Slew rate (falling), magnitude of RXCLK, RKLSB, RKMSB, RXD0 to RXD15 | 0.8 V to 2 V, C = 5 pF, see Figure 2                                                             | 0.5       |      |     | V/ns |

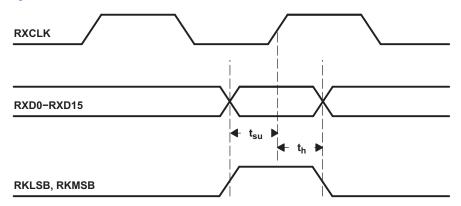

|                 | RXD0 to RXD15, RKMSB, RKLSB setup to ↑                               | 50% voltage swing, TXCLK = 80 MHz, to RXD15. RKMSB. RKLSB setup to ↑ see Figure 2 <sup>(1)</sup> |           |      |     |      |

| t <sub>su</sub> | RXCLK                                                                | 50% voltage swing, TXCLK = 125 MHz, see Figure 2 <sup>(1)</sup>                                  | 2.5       |      |     | ns   |

| t <sub>h</sub>  | DVD042 DVD45 DVMCD DVI CD balda a DVOLV                              | 50% voltage swing, TXCLK = 80 MHz, see Figure 2 <sup>(1)</sup>                                   | 30 MHz, 3 |      |     | ns   |

|                 | RXD0 to RXD15, RKMSB, RKLSB hold to ↑ RXCLK                          | 50% voltage swing, TXCLK = 125 MHz, see Figure 2 <sup>(1)</sup>                                  | 2         |      |     |      |

### (1) Nonproduction tested parameters.

Figure 1. TTL Data Input Valid Levels for AC Measurements

Figure 2. TTL Data Output Valid Levels for AC Measurements

Figure 3. Differential and Common-Mode Output Voltage

Figure 4. Common-Mode Output Voltage Definitions

# TEXAS INSTRUMENTS

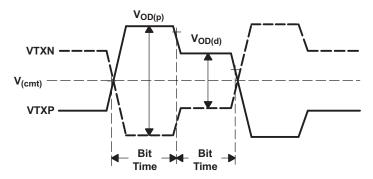

# 7.9 Typical Characteristics

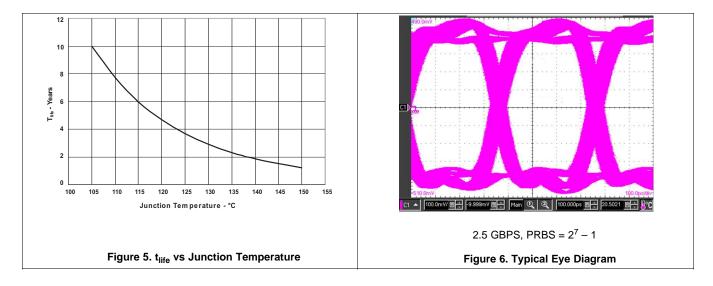

### 8 Detailed Description

#### 8.1 Overview

The TLK2711-SP is a member of the WizardLink transceiver family of multigigabit transceivers, intended for use in ultra-high-speed bidirectional point-to-point data transmission systems. The TLK2711-SP supports an effective serial interface speed of 1.6 Gbps to 2.5 Gbps, providing up to 2 Gbps of data bandwidth.

The following sections describe block-by-block features and operation of the TLK2711-SP transceiver.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Transmit Interface

The transmitter interface registers valid incoming 16-bit-wide data (TXD0 to TXD15) on the rising edge of the TXCLK. The data is then 8-bit/10-bit encoded, serialized, and transmitted sequentially over the differential high-speed I/O channel. The clock multiplier multiplies the reference clock (TXCLK) by a factor of 10x, creating a bit clock. This internal bit clock is fed to the parallel-to-serial shift register, which transmits data on both the rising and falling edges of the bit clock, providing a serial data rate that is 20x the reference clock. Data is transmitted least significant bit (LSB) (TXD0) first.

#### 8.3.2 Transmit Data Bus

The transmit data bus interface accepts 16-bit single-ended TTL parallel data at the TXD0–TXD15 pins. Data and K-code control is valid on the rising edge of the TXCLK. The TXCLK is used as the word clock. The data, K-code, and clock signals must be properly aligned as shown in Figure 7. Detailed timing information can be found in the *Transmitter/Receiver Electrical Characteristics*.

Figure 7. Transmit Timing Waveform

#### 8.3.3 Data Transmission Latency

The data transmission latency of the TLK2711-SP is defined as the delay from the initial 16-bit word load to the serial transmission of bit 0. The transmit latency is fixed after the link is established. However, due to silicon process variations and implementation variables such as supply voltage and temperature, the exact delay varies slightly. The minimum transmit latency  $t_{d(Tx | latency)}$  is 34 bit times; the maximum is 38 bit times. Figure 8 shows the timing relationship between the transmit data bus, TXCLK, and serial transmit pins.

Figure 8. Transmitter Latency

### **Feature Description (continued)**

#### 8.3.4 8-Bit/10-Bit Encoder

All true serial interfaces require a method of encoding to ensure minimum transition density, so that the receiving phase-locked loop (PLL) has a minimal number of transitions to stay locked on. The encoding scheme maintains the signal DC balance by keeping the number of 1s and 0s the same. This provides good transition density for clock recovery and improves error checking. The TLK2711-SP uses the 8-bit/10-bit encoding algorithm that is used by fibre channel and gigabit ethernet. This is transparent to the user, as the TLK2711-SP internally encodes and decodes the data such that the user reads and writes actual 16-bit data.

The 8-bit/10-bit encoder converts 8-bit-wide data to a 10-bit-wide encoded data character to improve its transmission characteristics. Because the TLK2711-SP is a 16-bit-wide interface, the data is split into two 8-bit-wide bytes for encoding. Each byte is fed into a separate encoder. The encoding is dependent upon two additional input signals, TKMSB and TKLSB.

| TKLSB | TKMSB | 16-BIT PARALLEL INPUT      |                             |  |  |  |  |  |  |  |

|-------|-------|----------------------------|-----------------------------|--|--|--|--|--|--|--|

| 0     | 0     | Valid data on TXD0 to TXD7 | Valid data TXD8 to TXD15    |  |  |  |  |  |  |  |

| 0     | 1     | Valid data on TXD0 to TXD7 | K code on TXD8 to TXD15     |  |  |  |  |  |  |  |

| 1     | 0     | K code on TXD0 to TXD7     | Valid data on TXD8 to TXD15 |  |  |  |  |  |  |  |

| 1     | 1     | K code on TXD0 to TXD7     | K code on TXD8 to TXD15     |  |  |  |  |  |  |  |

**Table 1. Transmit Data Controls**

### 8.3.5 Pseudo-Random Bit Stream (PRBS) Generator

The TLK2711-SP has a built-in  $2^7 - 1$  PRBS function. When the PRBSEN pin is forced high, the PRBS test is enabled. A PRBS is generated and fed into the 10-bit parallel-to-serial converter input register. Data from the normal input source is ignored during the PRBS mode. The PRBS pattern is then fed through the transmit circuitry as if it were normal data and sent out to the transmitter. The output can be sent to a bit error rate tester (BERT), the receiver of another TLK2711-SP, or looped back to the receive input. Because the PRBS is not really random, but a predetermined sequence of 1s and 0s, the data can be captured and checked for errors by a BERT.

#### 8.3.6 Parallel to Serial

The parallel-to-serial shift register takes in the 20-bit-wide data word multiplexed from the two parallel 8-bit/10-bit encoders and converts it to a serial stream. The shift register is clocked on both the rising and falling edge of the internally generated bit clock, which is 10x the TXCLK input frequency. The LSB (TXD0) is transmitted first.

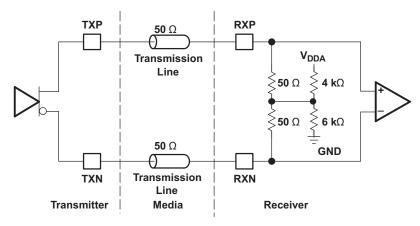

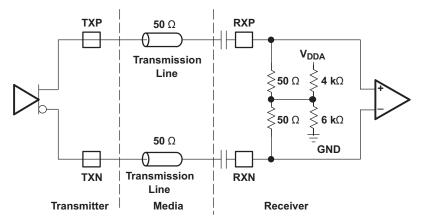

### 8.3.7 High-Speed Data Output

The high-speed data output driver consists of a voltage mode logic (VML) differential pair optimized for a  $50-\Omega$  impedance environment. The magnitude of the differential-pair signal swing is compatible with pseudo emitter coupled logic (PECL) levels when AC coupled. The line can be directly coupled or AC coupled. See Figure 13 and Figure 14 for termination details. The outputs also provide preemphasis to compensate for AC loss when driving a cable or PCB backplane trace over a long distance (see Figure 9). The level of preemphasis is controlled by PRE (see Table 2).

Figure 9. Output Voltage Under Preemphasis (VTXP to VTXN)

**Table 2. Programmable Preemphasis**

| PRE | PREEMPHASIS LEVEL (%) V <sub>OD(P)</sub> , V <sub>OD(D)</sub> <sup>(1)</sup> |  |  |  |

|-----|------------------------------------------------------------------------------|--|--|--|

| 0   | 5%                                                                           |  |  |  |

| 1   | 20%                                                                          |  |  |  |

V<sub>OD(p)</sub>: Voltage swing when there is a transition in the data stream.

$V_{\text{OD(d)}}\!\!:\!\text{Voltage}$  swing when there is no transition in the data stream.

#### 8.3.8 Receive Interface

The receiver interface of the TLK2711-SP accepts 8-bit/10-bit encoded differential serial data. The interpolator and clock recovery circuit locks to the data stream and extracts the bit-rate clock. This recovered clock is used to retime the input data stream. The serial data is then aligned to two separate 10-bit word boundaries, 8-bit/10-bit decoded, and output on a 16-bit-wide parallel bus synchronized to the extracted receive clock. The data is received LSB (RXD0) first.

#### 8.3.9 Receive Data Bus

The receive bus interface drives 16-bit-wide single-ended TTL parallel data at the RXD0 to RXD15 pins. Data is valid on the rising edge of the RXCLK. The RXCLK is used as the recovered word clock. The data, RKLSB, RKMSB, and clock signals are aligned as shown in Figure 10. Detailed timing information can be found in the TTL Output Switching Characteristics.

Figure 10. Receive Timing Waveform

#### 8.3.10 Data Reception Latency

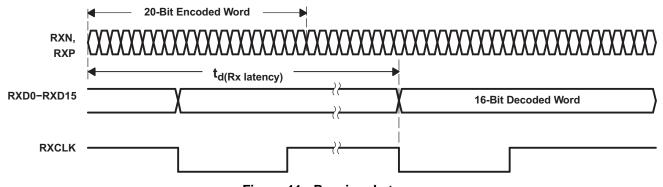

The serial-to-parallel data receive latency is the time from when the first bit arrives at the receiver until it is output in the aligned parallel word. The receive latency is fixed after the link is established. However, due to silicon process variations and implementation variables such as supply voltage and temperature, the exact delay varies slightly. The minimum receive latency  $t_{d(Rx\ latency)}$  is 76-bit times; the maximum is 107-bit times. Figure 11 shows the timing relationship between the serial receive pins, the recovered word clock (RXCLK), and the receive data bus

Figure 11. Receiver Latency

#### 8.3.11 Serial to Parallel

Serial data is received on the RXP and RXN pins. The interpolator and clock recovery circuit locks to the data stream if the clock to be recovered is within 200 PPM of the internally generated bit rate clock. The recovered clock is used to retime the input data stream. The serial data is then clocked into the serial-to-parallel shift registers. The 10-bit-wide parallel data is then multiplexed and fed into two separate 8-bit/10-bit decoders, where the data is then synchronized to the incoming data stream word boundary by detection of the comma 8-bit/10-bit synchronization pattern.

#### 8.3.12 Comma Detect and 8-Bit/10-Bit Decoding

The TLK2711-SP has two parallel 8-bit/10-bit decode circuits. Each 8-bit/10-bit decoder converts 10-bit encoded data (half of the 20-bit received word) back into 8 bits. The comma-detect circuit is designed to provide for byte synchronization to an 8-bit/10-bit transmission code. When parallel data is clocked into a parallel-to-serial converter, the byte boundary that was associated with the parallel data is now lost in the serialization of the data. When the serial data is received and converted to parallel format again, a method is needed to recognize the byte boundary. Typically, this is accomplished through the use of a synchronization pattern. This is typically a unique pattern of 1s and 0s that either cannot occur as part of valid data or is a pattern that repeats at defined intervals. The 8-bit/10-bit encoding contains a character called the comma (b0011111 or b1100000), which is used by the comma-detect circuit on the TLK2711-SP to align the received serial data back to its original byte boundary. The decoder detects the comma, generating a synchronization signal aligning the data to their 10-bit boundaries for decoding; the comma is mapped into the LSB. The decoder then converts the data back into 8-bit data. The output from the two decoders is latched into the 16-bit register synchronized to the recovered parallel data clock (RXCLK) and output valid on the rising edge of the RXCLK.

#### NOTE

The TLK2711-SP only achieves byte alignment on the 0011111 comma.

Decoding provides two additional status signals, RKLSB and RKMSB. When RKLSB is asserted, an 8-bit/10-bit K code is received and the specific K code is presented on the data bits RXD0 to RXD7; otherwise, an 8-bit/10-bit D code is received. When RKMSB is asserted, an 8-bit/10-bit K code is received and the specific K-code is presented on data bits RXD8 to RXD15; otherwise, an 8-bit/10-bit D code is received (see Table 3). The valid K codes the TLK2711-SP; decodes are provided in Table 4. An error detected on either byte, including K codes not in Table 4, causes that byte only to indicate a K0.0 code on the RKxSB and associated data pins, where K0.0 is known to be an invalid 8-bit/10-bit code. A loss of input signal causes a K31.7 code to be presented on both bytes, where K31.7 is also known to be an invalid 8-bit/10-bit code.

**Table 3. Receive Status Signals**

| RKLSB | RKMSB | DECODED 20-BIT OUTPUT      |                             |  |  |  |  |  |  |

|-------|-------|----------------------------|-----------------------------|--|--|--|--|--|--|

| 0     | 0     | Valid data on RXD0 to RXD7 | Valid data RXD8 to RXD15    |  |  |  |  |  |  |

| 0     | 1     | Valid data on RXD0 to RXD7 | K code on RXD8 to RXD15     |  |  |  |  |  |  |

| 1     | 0     | K code on RXD0 to RXD7     | Valid data on RXD8 to RXD15 |  |  |  |  |  |  |

| 1     | 1     | K code on RXD0 to RXD7     | K code on RXD8 to RXD15     |  |  |  |  |  |  |

Table 4. Valid K Characters

| K CHARACTER          | RECEIVE DATA BUS<br>RXD7:RXD0 OR RXD15:RXD8 |

|----------------------|---------------------------------------------|

| K28.0                | 000 11100                                   |

| K28.1 <sup>(1)</sup> | 001 11100                                   |

| K28.2                | 010 11100                                   |

| K28.3                | 011 11100                                   |

| K28.4                | 100 11100                                   |

| K28.5 <sup>(1)</sup> | 101 11100                                   |

| K28.6                | 110 11100                                   |

| K28.7 <sup>(1)</sup> | 111 11100                                   |

| K23.7                | 111 10111                                   |

| K27.7                | 111 11011                                   |

| K29.7                | 111 11101                                   |

| K30.7                | 111 11110                                   |

<sup>(1)</sup> Should only be present on RXD0 to RXD7 when in running disparity < 0.

#### 8.3.13 LOS Detection

The TLK2711-SP has a LOS detection circuit for conditions where the incoming signal no longer has a sufficient voltage level to keep the clock recovery circuit in lock. The signal detection circuit is intended to be an indication of gross signal error conditions, such as a detached cable or no signal being transmitted, and not an indication of signal coding health. The TLK2711-SP reports this condition by asserting RKLSB, RKMSB, and RXD0 to RXD15 pins to a high state. As long as the differential signal is above 200 mV in differential magnitude, the LOS circuit does not signal an error condition. When the device is disabled (ENABLE = L), RKMSB will output the status of LOS. Active low = LOS detected.

#### 8.3.14 PRBS Verification

The TLK2711-SP also has a built-in BERT function in the receiver side that is enabled by the PRBSEN. It can check for errors and report the errors by forcing the RKLSB pin low.

#### 8.3.15 Reference Clock Input

The reference clock (TXCLK) is an external input clock that synchronizes the transmitter interface. The reference clock is then multiplied in frequency 10x to produce the internal serialization bit clock. The internal serialization bit clock is frequency locked to the reference clock and used to clock out the serial transmit data on both its rising and falling edges, providing a serial data rate that is 20x the reference clock.

### 8.3.16 Operating Frequency Range

The TLK2711-SP operates at a serial data rate from 1.6 to 2.5 Gbps. To achieve these serial rates, TXCLK must be within 80 to 125 MHz. The TXCLK must be within ±100 PPM of the desired parallel data rate clock.

#### 8.3.17 Testability

The TLK2711-SP has a comprehensive suite of built-in self-tests. The loopback function provides for at-speed testing of the transmit/receive portions of the circuitry. The enable pin allows for all circuitry to be disabled so that a quiescent current test can be performed. The PRBS function allows for built-in self-test (BIST).

#### 8.3.18 Loopback Testing

The transceiver can provide a self-test function by enabling (LOOPEN) the internal loopback path. Enabling this pin causes serial-transmitted data to be routed internally to the receiver. The parallel data output can be compared to the parallel input data for functional verification. The external differential output is held in a high-impedance state during the loopback testing.

#### 8.3.19 BIST

The TLK2711-SP has a BIST function. By combining PRBS with loopback, an effective self-test of all the circuitry running at full speed can be realized. The successful completion of the BIST is reported on the RKLSB pin.

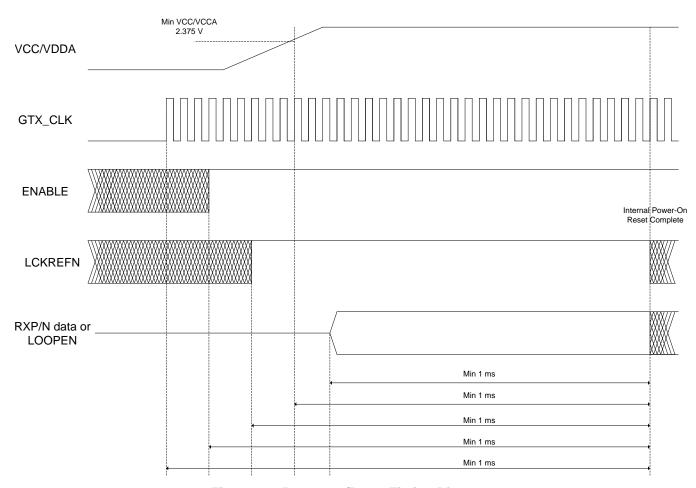

#### 8.3.20 Power-On Reset

Upon application of minimum valid power and valid GTX\_CLK with device enabled (ENABLE = HIGH), the TLK2711-SP generates a power-on reset. During the power-on reset the RXD0 to RXD15, RKLSB, and RKMSB signal pins go to a high-impedance state. The RXCLK is held low. LCKREFN must be deasserted (logic high state) with active transitions on the receiver during the power-on reset period. Active transitions on receiver can be accomplished with transitions on RXP/N or by assertion of LOOPEN. For TX-only applications, LOOPEN and LCKREFN can be driven logic high together. The receiver circuit requires this to properly reset. After power-up reset period, LCKREFN can be asserted for transmit only applications. The length of the power-on reset cycle depends on the TXCLK frequency, but is less than 1 ms. See Figure 12 . TI recommends that the receiver be reset immediately after power up. In some conditions, it is possible for the receiver circuit to power up in state with internal contention.

If LCKREFN cannot be deasserted high during or for the complete power-on reset period, it can be deasserted high at the end of or after the power-on reset period for minimum of 1  $\mu$ s with active transitions on receiver to properly complete reset of receiver.

Figure 12. Power-On/Reset Timing Diagram

#### 8.4 Device Functional Modes

#### 8.4.1 Power-Down Mode

The TLK2711-SP goes into power-down mode when the ENABLE pin is pulled low. In the power-down mode, the serial transmit pins (TXN), the receive data bus pins (RXD0 to RXD15), and RKLSB goes into a high-impedance state. In the power-down condition, the signal detection circuit draws less than 15 mW. When the TLK2711-SP is in the power-down mode, the clock signal on the TXCLK pin must be provided if LOS functionality is needed.

### 8.4.2 High-Speed I/O Directly-Coupled Mode

Figure 13. High-Speed I/O Directly-Coupled Mode Schematic

### 8.4.3 High-Speed I/O AC-Coupled Mode

Figure 14. High-Speed I/O AC-Coupled Mode Schematic

# 9 Application and Implementation

#### **NOTE**

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The TLK2711-SP may be operated as full link with send/receive functions or each end of link may be transmit only or receive only.

The transmitter is always operational in either case as GTX\_CLK is required to source the PLL. In transmit only cases, LCKREFN can be pulled low to disable the RX interface. See *Power-On Reset* for requirements.

### 9.2 Typical Application

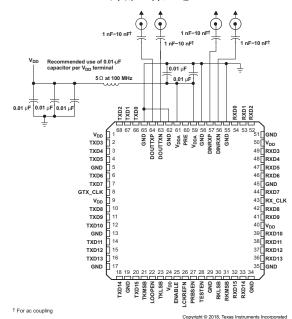

Figure 15. External Component Interconnection

### **Typical Application (continued)**

### 9.2.1 Design Requirements

Input conditions in the data sheet were created and validated to achieve a bit error rate (BER) of 1 error in 1E12 bits or better. Other aspects that affect BER are power supply noise, quality (loss), and matching of  $50-\Omega$ controlled impedance for transmit and receive differential pins.

#### 9.2.2 Detailed Design Procedure

Detailed design procedures involve careful examination of system properties, design, and error rate goals. Understanding these properties allows for creation of jitter budget to ensure design BER goals are achieved. Application note SLLA071 is based on the TLK2500. The TLK2500 shares the same architecture and similar jitter properties.

### 9.2.3 Application Curves

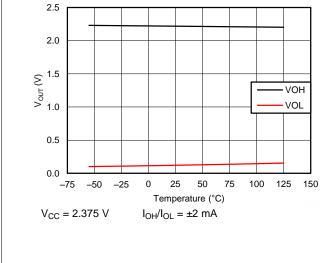

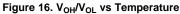

Figure 16 shows typical TTL output voltage characteristics at maximum 2-mA load at minimum  $V_{CC} = 2.375 \text{ V}$ . Figure 17 shows typical differential output voltage VOD(p) across temperature for each preemphasis condition at minimum  $V_{CC} = 2.375 \text{ V}.$

V<sub>OD</sub> (1) represents 20% emphasis enabled.

Figure 17.  $V_{OD}$  (0),  $V_{OD}$  (1) vs Temperature

### 10 Power Supply Recommendations

Power supplies must be within recommended operating range and should have less than 100 mV of ripple. Exceeding 100-mV ripple can impact transmitted jitter and receiver jitter tolerance.

VDDA should be filtered from VDD. Filter values should be set to minimize any frequency components from power supply and/or digital logic that may exist in the system in the range of the PLL jitter transfer characteristics. The PLL is sensitive to noise in the range of 300 kHz to 3 MHz.

### 11 Layout

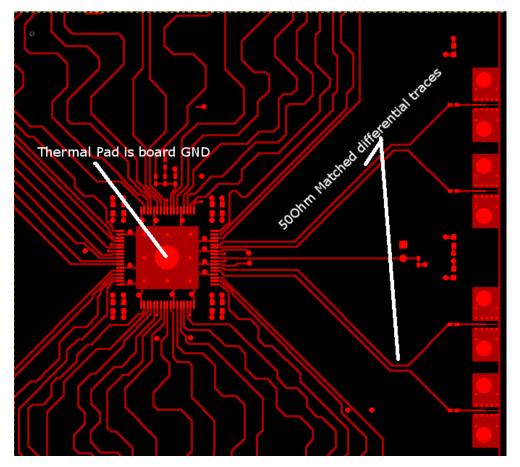

### 11.1 Layout Guidelines

Standard high-speed differential routing best practices must be employed. Routing should be  $50-\Omega$  matched impedance and length for differential transmit and receive. Minimize layer transitions and stubs to reduce any impedance mismatches. Connecting the thermal pad to board ground improves device performance by supplying lower impedance path to ground minimizing ground bounce and improves thermal dissipation.

### 11.2 Layout Example

Figure 18. Layout Recommendation

### 12 器件和文档支持

### 12.1 接收文档更新通知

要接收文档更新通知,请导航至 Tl.com 上的器件产品文件夹。请单击右上角的提醒我 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

### 12.2 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的 《使用条款》。

TI E2E™ 在线社区 TI 的工程师对工程师 (E2E) 社区。此社区的创建目的在于促进工程师之间的协作。在 e2e.ti.com 中,您可以咨询问题、分享知识、拓展思路并与同行工程师一道帮助解决问题。

设计支持 TI 参考设计支持 可帮助您快速查找有帮助的 E2E 论坛、设计支持工具以及技术支持的联系信息。

#### 12.3 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.4 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 13 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知和修订此文档。如欲获取此数据表的浏览器版本,请参阅左侧的导航。

### PACKAGE OPTION ADDENDUM

4-Feb-2021

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5)               | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|---------------------------------------|---------|

| 5962-0522101VXC  | ACTIVE     | CFP          | HFG                | 68   | 1              | RoHS & Green | Call TI                       | N / A for Pkg Type | -55 to 125   | 5962-<br>0522101VXC<br>TLK2711HFGQMLV | Samples |

| TLK2711HFG/EM    | ACTIVE     | CFP          | HFG                | 68   | 1              | RoHS & Green | Call TI                       | N / A for Pkg Type | 25 to 25     | TLK2711HFG/EM<br>EVAL ONLY            | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

### **PACKAGE OPTION ADDENDUM**

4-Feb-2021

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

HFG (S-CQFP-F68)

### CERAMIC QUAD FLATPACK WITH NCTB

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Ceramic quad flatpack with flat leads brazed to non-conductive tie bar carrier.

- D. This package is hermetically sealed with a metal lid.

- E. The leads are gold plated and can be solderdipped.

- F. Leads not shown for clarity purposes.

- G. Thermal dissipation enhancement provided by vias to external bottom pad.

- H. Lid and Thermal pad are connected to GND leads.

### 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 (https://www.ti.com.cn/zh-cn/legal/termsofsale.html) 或 ti.com.cn 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码:200122 Copyright © 2021 德州仪器半导体技术(上海)有限公司