ZHCS830-MARCH 2012

# 超低噪声、高电源抑制比 (PSRR)、快速、射频 (RF)、1A

# 低压差线性稳压器

查询样品: TPS796xx-Q1

## 特性

- 符合汽车应用要求

- 具有下列结果的 AEC-Q100 测试指南:

- 器件温度 1 级: -40℃ 至 125℃ 的环境运行温 度范围

- 器件人体模型 (HBM) 静电放电 (ESD) 分类等级

H2

- 器件充电器件模型 (CDM) ESD 分类等级 C3A

- 具有使能端的 1A 低压差稳压器

- 提供固定和可调节(1.2V至 5.5V)版本

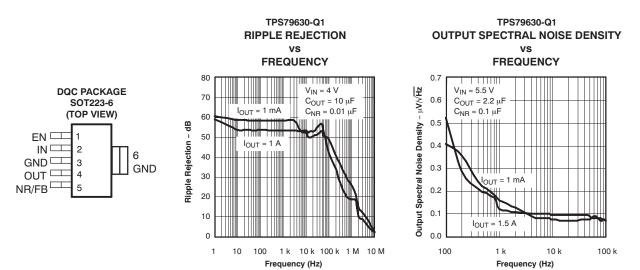

- 高 PSRR (频率为 10kHz 时为53dB)

- 超低噪声 (40µV<sub>RMS</sub>, TPS79630-Q1)

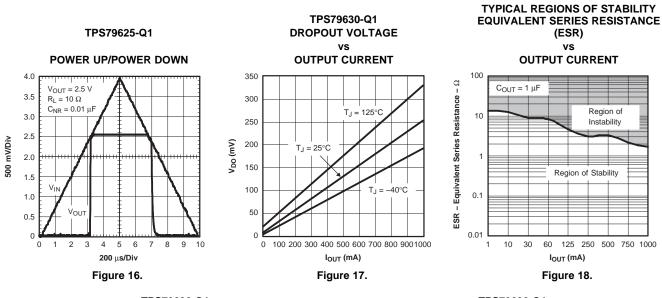

- 快速启动时间 (50µs)

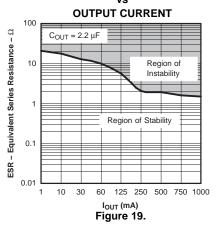

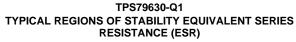

- 与 1µF 陶瓷电容器一起工作时保持稳定

- 出色的负载/线路瞬态响应

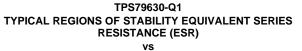

- 极低压差电压(全负载时为 250mV, TPS79630-Q1)

- SOT223-6 封装

应用范围

- RF: VOC、接收器、数模转换器 (ADC)

- 音频

- 蓝牙™、无线局域网 **(LAN)** 说明

TPS796xx-Q1 是低压差 (LDO)、低功率、线性电压稳 压器系列产品,此产品在一个小外形尺寸 SOT223-6 封装内特有高电源抑制比 (PSRR)、超低噪声、快速软 启动、以及出色的线路和负载瞬态响应功能。 此系列 产品中的每一个器件在输出上与一个小型 1µF 陶瓷电 容器一起工作时保持稳定。此系列产品使用一个高级 的、私有 BiCOMS 制造工艺以生成极低的压差电 压(例如,1A时为250mV)。每个器件可实现快速 启动时间(使用一个 0.001µF 旁路电容器时大约为 50µs)同时消耗非常低的静态电流(典型值 265µA)。而且,当此器件被置于待机模式下时,电 源电流被减少至少于 1µA。 当使用一个 0.1µF 旁路电 容器时, TPS79630-Q1 在 3V 输出上的输出电压噪声 大约为 40µV<sub>RMS</sub> 。 对于诸如便携式 RF 电子器件等使 用噪声敏感模拟部件的应用,得益于高 PSRR、低噪 声特性和快速响应时间等特性。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. 蓝牙 is a trademark of Bluetooth SIG, Inc.

All other trademarks are the property of their respective owners.

## TPS796xx-Q1

#### ZHCS830-MARCH 2012

www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT     | SPECIFIED<br>TEMPERATURE<br>RANGE, T <sub>A</sub> | PACKAGE TYPE,<br>PACKAGE<br>DESIGNATOR <sup>(2)</sup> | PACKAGE<br>MARKING | ORDERING NUMBER | TRANSPORT<br>MEDIA,<br>QUANTITY |  |  |  |  |  |  |  |

|-------------|---------------------------------------------------|-------------------------------------------------------|--------------------|-----------------|---------------------------------|--|--|--|--|--|--|--|

| TPS79633-Q1 | -40°C to +125°C                                   | SOT223-6, DCQ                                         | 79633Q             | TPS79633QDCQRQ1 | Reel, 2500                      |  |  |  |  |  |  |  |

| TPS79630-Q1 | -40°C to 125°C                                    | SOT223-6, DCQ                                         | PREVIEW            | TPS79630QDCQRQ1 | Reel, 2500                      |  |  |  |  |  |  |  |

| TPS79625-Q1 | -40°C to 125°C                                    | SOT223-6, DCQ                                         | PREVIEW            | TPS79625QDCQRQ1 | Reel, 2500                      |  |  |  |  |  |  |  |

| TPS79628-Q1 | -40°C to 125°C                                    | SOT223-6, DCQ                                         | PREVIEW            | TPS79628QDCQRQ1 | Reel, 2500                      |  |  |  |  |  |  |  |

#### ORDERING INFORMATION<sup>(1)</sup>

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating temperature range (unless otherwise noted).

|                                |                                                              | UNIT                              |  |  |

|--------------------------------|--------------------------------------------------------------|-----------------------------------|--|--|

| V <sub>IN</sub> range          |                                                              | –0.3 V to 6 V                     |  |  |

| V <sub>EN</sub> range          |                                                              | –0.3 V to V <sub>IN</sub> + 0.3 V |  |  |

| V <sub>OUT</sub> range         |                                                              | 6 V                               |  |  |

| Peak output current            | Internally limited                                           |                                   |  |  |

| Continuous total power dissipa | Continuous total power dissipation See Thermal Info          |                                   |  |  |

| ESD rotings                    | Human Body Model (HBM) AEC-Q100 Classification Level H2      | 2 kV                              |  |  |

| ESD ratings                    | Charged Device Model (CDM) AEC-Q100 Classification Level C3A | 500 V                             |  |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

ZHCS830-MARCH 2012

## **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range (unless otherwise noted).

|                                     | MIN  | NOM | MAX | UNIT |

|-------------------------------------|------|-----|-----|------|

| Ambient temperature, T <sub>A</sub> | -40° |     | 125 | °C   |

#### **THERMAL INFORMATION**

|                         |                                              | TPS796xx-Q1 |       |  |

|-------------------------|----------------------------------------------|-------------|-------|--|

|                         | THERMAL METRIC <sup>(1)(2)</sup>             | DCQ         | UNIT  |  |

|                         |                                              | 6 PINS      |       |  |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 70.4        | °C/W  |  |

| θ <sub>JCtop</sub>      | Junction-to-case (top) thermal resistance    | 70          | °C/W  |  |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | N/A         | °C/W  |  |

| Ψ <sub>JT</sub>         | Junction-to-top characterization parameter   | 6.8         | °C/W° |  |

| Ψ <sub>JB</sub>         | Junction-to-board characterization parameter | 30.1        | °C/W  |  |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 6.3         | °C/W  |  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953A.

(2) For thermal estimates of this device based on PCB copper area, see the TI PCB Thermal Calculator.

#### ZHCS830-MARCH 2012

## **ELECTRICAL CHARACTERISTICS**

Over recommended operating temperature range ( $T_A = -40^{\circ}$ C to 125°C),  $V_{EN} = V_{IN,}$ ,  $V_{IN} = V_{OUT(nom)} + 1 V^{(1)}$ ,  $I_{OUT} = 1 \text{ mA}$ ,  $C_{OUT} = 10 \mu$ F, and  $C_{NR} = 0.01 \mu$ F, unless otherwise noted. Typical values are at +25°C.

|                                                      | PARAMET                                          | ER                              | TEST CON                                                         | MIN                                                                                                                     | TYP  | MAX             | UNIT |               |

|------------------------------------------------------|--------------------------------------------------|---------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|-----------------|------|---------------|

| V <sub>IN</sub> Input voltage <sup>(1)</sup>         |                                                  |                                 |                                                                  | 2.7                                                                                                                     |      | 5.5             | V    |               |

| I <sub>OUT</sub> Continuous output current           |                                                  |                                 |                                                                  |                                                                                                                         | 0    |                 | 1    | А             |

| Output<br>voltage                                    | Accuracy                                         | Fixed<br>V <sub>OUT</sub> < 5 V | 0 µA ≤ $I_{OUT}$ ≤ 1 A, $V_{OUT}$ + 1                            | 0 $\mu$ A $\leq$ I <sub>OUT</sub> $\leq$ 1 A, V <sub>OUT</sub> + 1 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V <sup>(1)</sup> |      |                 | +2.0 | %             |

| Output volta<br>(ΔV <sub>OUT</sub> %/V <sub>II</sub> | ige line regula<br><sub>N</sub> ) <sup>(1)</sup> | ation                           | $V_{OUT} + 1 V \le V_{IN} \le 5.5 V$                             |                                                                                                                         |      | 0.05            | 0.12 | %/V           |

| Load regulat                                         | tion (ΔV <sub>OUT</sub> %                        | /ΔI <sub>OUT</sub> )            | 0 µA ≤ I <sub>OUT</sub> ≤ 1 A                                    |                                                                                                                         |      | 5               |      | mV            |

| Dropout volt                                         | tage <sup>(2)</sup>                              | TPS79628-Q1                     | I <sub>OUT</sub> = 1 A                                           |                                                                                                                         |      | 270             | 365  | mV            |

| $(V_{IN} = V_{OUT})$                                 |                                                  | TPS79630-Q1                     | I <sub>OUT</sub> = 1 A                                           |                                                                                                                         |      | 250             | 345  | mV            |

| V)                                                   |                                                  | TPS79633-Q1                     | I <sub>OUT</sub> = 1 A                                           |                                                                                                                         |      | 220             | 325  | mV            |

| Output curre                                         | ent limit                                        |                                 | $V_{OUT} = 0 V$                                                  |                                                                                                                         | 2.4  |                 | 4.2  | А             |

| Ground pin current                                   |                                                  |                                 | $0 \ \mu A \le I_{OUT} \le 1 \ A$                                |                                                                                                                         |      | 265             | 385  | μA            |

| Shutdown current <sup>(3)</sup>                      |                                                  |                                 | $V_{EN} = 0 V, 2.7 V \le V_{IN} \le 5.5$                         |                                                                                                                         | 0.07 | 1               | μA   |               |

| FB pin current                                       |                                                  |                                 | V <sub>FB</sub> = 1.225 V                                        |                                                                                                                         |      | 1               | μA   |               |

|                                                      | pply ripple                                      | TPS79630-Q1                     | f = 100 Hz, I <sub>OUT</sub> = 10 mA                             |                                                                                                                         | 59   |                 | dB   |               |

| Power-suppl                                          |                                                  |                                 | f = 100 Hz, I <sub>OUT</sub> = 1 A                               |                                                                                                                         | 54   |                 | dB   |               |

| rejection                                            |                                                  |                                 | f = 10 Hz, I <sub>OUT</sub> = 1 A                                |                                                                                                                         | 53   |                 | dB   |               |

|                                                      |                                                  |                                 | f = 100 Hz, I <sub>OUT</sub> = 1 A                               |                                                                                                                         | 42   |                 | dB   |               |

|                                                      |                                                  |                                 |                                                                  | $C_{NR} = 0.001 \ \mu F$                                                                                                |      | 54              |      | $\mu V_{RMS}$ |

|                                                      | e voltage (TP                                    | S79630-01)                      | BW = 100 Hz to 100 kHz,                                          | $C_{NR} = 0.0047 \ \mu F$                                                                                               |      | 46              |      | $\mu V_{RMS}$ |

| Output hoise                                         | e voltage (11                                    | G79030-Q1)                      | I <sub>OUT</sub> = 1 A                                           | $C_{NR} = 0.01 \ \mu F$                                                                                                 |      | 41              |      | $\mu V_{RMS}$ |

|                                                      |                                                  |                                 |                                                                  | C <sub>NR</sub> = 0.1 μF                                                                                                | 40   |                 |      | $\mu V_{RMS}$ |

|                                                      |                                                  |                                 |                                                                  | $C_{NR} = 0.001 \ \mu F$                                                                                                |      | 50              |      | μs            |

| Time, start-u                                        | up (TPS79630                                     | )-Q1)                           | $R_L = 3 \ \Omega, \ C_{OUT} = 1 \ \mu F$                        | $C_{NR} = 0.0047 \ \mu F$                                                                                               |      | 75              |      | μs            |

|                                                      |                                                  |                                 | $C_{NR} = 0.01 \ \mu F$                                          |                                                                                                                         | 110  |                 | μs   |               |

| EN pin current                                       |                                                  | V <sub>EN</sub> = 0 V           | -1                                                               |                                                                                                                         | 1    | μA              |      |               |

| UVLO threshold                                       |                                                  |                                 | V <sub>CC</sub> rising                                           |                                                                                                                         | 2.25 |                 | 2.65 | V             |

| UVLO hyste                                           | eresis                                           |                                 |                                                                  |                                                                                                                         |      | 100             |      | mV            |

| High-level e                                         | nable input vo                                   | oltage                          | $2.7~\textrm{V} \leq \textrm{V}_\textrm{IN} \leq 5.5~\textrm{V}$ | 1.7                                                                                                                     |      | V <sub>IN</sub> | V    |               |

| Low-level er                                         | nable input vo                                   | ltage                           | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5.5 \text{ V}$     | 0                                                                                                                       |      | 0.7             | V    |               |

Minimum V<sub>IN</sub> = V<sub>OUT</sub> + V<sub>DO</sub> or 2.7 V, whichever is greater. TPS79650-Q1 is tested at V<sub>IN</sub> = 5.5 V. V<sub>DO</sub> is not measured for TPS79625-Q1 because minimum V<sub>IN</sub> = 2.7 V. For adjustable version, this applies only after V<sub>IN</sub> is applied; then V<sub>EN</sub> transitions high to low. (1)

(2) (3)

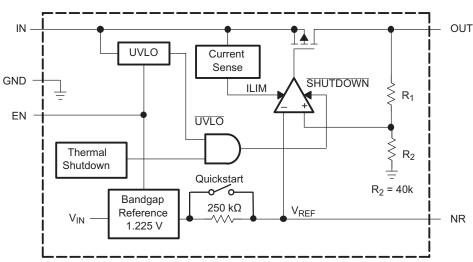

#### FUNCTIONAL BLOCK DIAGRAM

#### **Table 1. Terminal Functions**

| TERMINAL<br>SOT223<br>NAME (DCQ) |        |                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|----------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                  |        | DESCRIPTION                                                                                                                                                                                                                             |  |  |  |  |  |  |

| NR                               | 5      | Connecting an external capacitor to this pin bypasses noise generated by the internal bandgap. This improves power-supply rejection and reduces output noise.<br>This terminal is the feedback input voltage for the adjustable device. |  |  |  |  |  |  |

| FB                               | 5      |                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| EN 1                             |        | Driving the enable pin (EN) high turns on the regulator. Driving this pin low puts the regulator into shutdown mode. EN can be connected to IN if not used.                                                                             |  |  |  |  |  |  |

| GND                              | 3, Tab | Regulator ground                                                                                                                                                                                                                        |  |  |  |  |  |  |

| IN 2                             |        | Unregulated input to the device.                                                                                                                                                                                                        |  |  |  |  |  |  |

| OUT 4                            |        | Output of the regulator.                                                                                                                                                                                                                |  |  |  |  |  |  |

ZHCS830-MARCH 2012

TEXAS INSTRUMENTS

www.ti.com.cn

ZHCS830-MARCH 2012

www.ti.com.cn

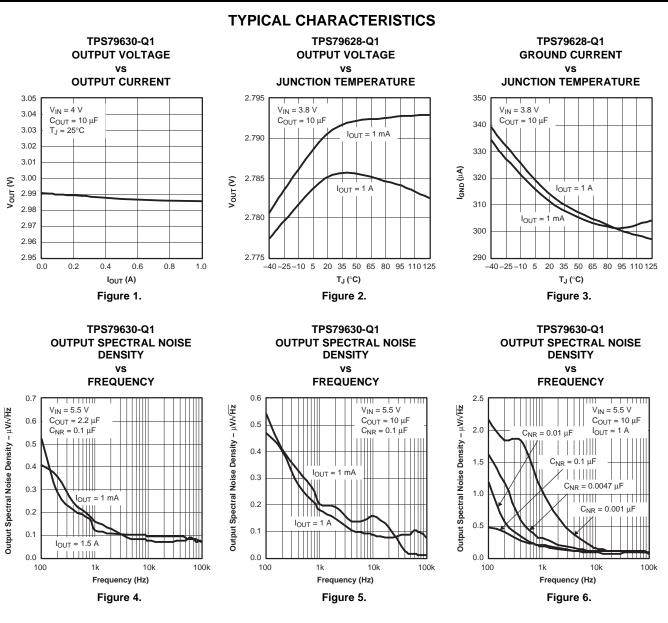

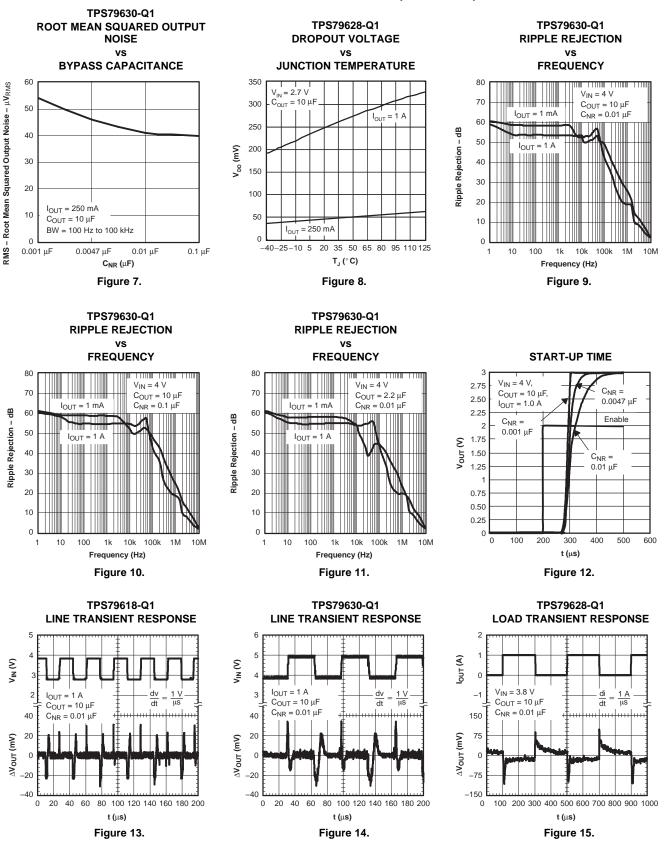

### **TYPICAL CHARACTERISTICS (continued)**

ZHCS830-MARCH 2012

TPS79630-Q1

www.ti.com.cn

### **TYPICAL CHARACTERISTICS (continued)**

### **APPLICATION INFORMATION**

The TPS796xx-Q1 family of low-dropout (LDO) regulators has been optimized for use in noise-sensitive equipment. The device features extremely low dropout voltages, high PSRR, ultralow output noise, low quiescent current (265  $\mu$ A typically), and enable input to reduce supply currents to less than 1  $\mu$ A when the regulator is turned off.

A typical application circuit is shown in Figure 21.

Figure 21. Typical Application Circuit

#### **External Capacitor Requirements**

Although not required, it is good analog design practice to place a 0.1-µF to 2.2-µF capacitor near the input of the regulator to counteract reactive input sources. A 2.2-µF or larger ceramic input bypass capacitor, connected between IN and GND and located close to the TPS796xx-Q1, is required for stability and improves transient response, noise rejection, and ripple rejection. A higher-value input capacitor may be necessary if large, fast-rise-time load transients are anticipated and the device is located several inches from the power source.

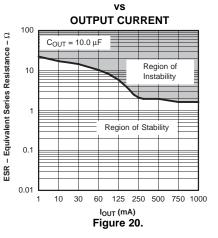

As with most LDO regulators, the TPS796xx-Q1 requires an output capacitor connected between OUT and GND to stabilize the internal control loop. The minimum recommended capacitor is 1  $\mu$ F. Any 1- $\mu$ F or larger ceramic capacitor is suitable.

The internal voltage reference is a key source of noise in an LDO regulator. The TPS796xx-Q1 has an NR pin that is connected to the voltage reference through a 250-k $\Omega$  internal resistor. The 250-k $\Omega$  internal resistor, in conjunction with an external bypass capacitor connected to the NR pin, creates a low-pass filter to reduce the voltage reference noise and, therefore, the noise at the regulator output. In order for the regulator to operate properly, the current flow out of the NR pin must be at a minimum, because any leakage current creates an IR drop across the internal resistor, thus creating an output error. Therefore, the bypass capacitor must have minimal leakage current. The bypass capacitor should be no more than 0.1  $\mu$ F in order to ensure that it is fully charged during the quickstart time provided by the internal switch shown in the Functional Block Diagram.

For example, the TPS79630-Q1 exhibits 40  $\mu V_{RMS}$  of output voltage noise using a 0.1- $\mu$ F ceramic bypass capacitor and a 10- $\mu$ F ceramic output capacitor. Note that the output starts up slower as the bypass capacitance increases because of the RC time constant at the bypass pin that is created by the internal 250-k $\Omega$  resistor and external capacitor.

#### **Board Layout Recommendation to Improve PSRR and Noise Performance**

To improve ac measurements such as PSRR, output noise, and transient response, it is recommended that the board be designed with separate ground planes for  $V_{IN}$  and  $V_{OUT}$ , with each ground plane connected only at the ground pin of the device. In addition, the ground connection for the bypass capacitor should connect directly to the ground pin of the device.

#### **Regulator Mounting**

The tab of the SOT223-6 package is electrically connected to ground. For best thermal performance, the tab of the surface-mount version should be soldered directly to the printed circuit board (PCB) copper area. Increasing the copper area improves heat dissipation.

Solder pad footprint recommendations for the devices are presented in an application bulletin *Solder Pad Recommendations for Surface-Mount Devices*, literature number AB-132, available for download from the TI web site (www.ti.com).

Copyright © 2012, Texas Instruments Incorporated

# ZHCS830-MARCH 2012

#### **Regulator Protection**

The TPS796xx-Q1 PMOS-pass transistor has a built-in back diode that conducts reverse current when the input voltage drops below the output voltage (for example, during power-down). Current is conducted from the output to the input and is not internally limited. If extended reverse voltage operation is anticipated, external limiting might be appropriate.

The TPS796xx-Q1 features internal current limiting and thermal protection. During normal operation, the TPS796xx-Q1 limits output current to approximately 2.8 A. When current limiting engages, the output voltage scales back linearly until the overcurrent condition ends. While current limiting is designed to prevent gross device failure, care should be taken not to exceed the power dissipation ratings of the package. If the temperature of the device exceeds approximately +165°C, thermal-protection circuitry shuts it down. Once the device has cooled down to below approximately +140°C, regulator operation resumes.

#### THERMAL INFORMATION

#### POWER DISSIPATION

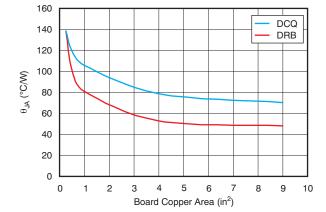

Knowing the device power dissipation and proper sizing of the thermal plane that is connected to the tab or pad is critical to avoiding thermal shutdown and ensuring reliable operation.

Power dissipation of the device depends on input voltage and load conditions and can be calculated using Equation 1:

$$\mathsf{P}_{\mathsf{D}} = \left(\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}\right) \times \mathsf{I}_{\mathsf{OUT}}$$

Power dissipation can be minimized and greater efficiency can be achieved by using the lowest possible input voltage necessary to achieve the required output voltage regulation.

On the SON (DRB) package, the primary conduction path for heat is through the exposed pad to the PCB. The pad can be connected to ground or be left floating; however, it should be attached to an appropriate amount of copper PCB area to ensure the device does not overheat. On the SOT-223 (DCQ) package, the primary conduction path for heat is through the tab to the PCB. That tab should be connected to ground. The maximum junction-to-ambient thermal resistance depends on the maximum ambient temperature, maximum device junction temperature, and power dissipation of the device and can be calculated using Equation 2:

$$R_{\theta JA} = \frac{(+125^{\circ}C - T_A)}{P_D}$$

Knowing the maximum  $R_{\theta JA}$ , the minimum amount of PCB copper area needed for appropriate heatsinking can be estimated using Figure 22.

Note:  $\theta_{JA}$  value at board size of 9 in<sup>2</sup> (that is, 3 in x 3 in) is a JEDEC standard.

Figure 22.  $\theta_{JA}$  vs Board Size

Figure 22 shows the variation of  $\theta_{JA}$  as a function of ground plane copper area in the board. It is intended only as a guideline to demonstrate the effects of heat spreading in the ground plane and should not be used to estimate actual thermal performance in real application environments.

**NOTE:** When the device is mounted on an application PCB, it is strongly recommended to use  $\Psi_{JT}$  and  $\Psi_{JB}$ , as explained in the *Estimating Junction Temperature* section.

ZHCS830-MARCH 2012

(2)

### ESTIMATING JUNCTION TEMPERATURE

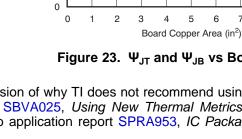

Using the thermal metrics  $\Psi_{JT}$  and  $\Psi_{JB}$ , as shown in the *Thermal Information* table, the junction temperature can be estimated with corresponding formulas (given in Equation 3). For backwards compatibility, an older  $\theta_{JC}$ , Top parameter is listed as well.

$$\Psi_{JT}: T_J = T_T + \Psi_{JT} \bullet P_D$$

$$\Psi_{\mathsf{JB}}: \quad \mathsf{T}_{\mathsf{J}} = \mathsf{T}_{\mathsf{B}} + \Psi_{\mathsf{JB}} \bullet \mathsf{P}_{\mathsf{D}}$$

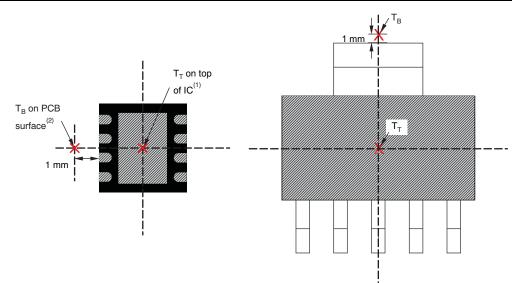

Where  $P_D$  is the power dissipation shown by Equation 2,  $T_T$  is the temperature at the center-top of the IC package, and  $T_B$  is the PCB temperature measured 1 mm away from the IC package *on the PCB surface* (as Figure 24 shows).

NOTE: Both T<sub>T</sub> and T<sub>B</sub> can be measured on actual application boards using a thermo-gun (an infrared thermometer).

For more information about measuring  $T_T$  and  $T_B$ , see the application note SBVA025, Using New Thermal Metrics, available for download at www.ti.com.

By looking at Figure 23, the new thermal metrics ( $\Psi_{JT}$  and  $\Psi_{JB}$ ) have very little dependency on board size. That is, using  $\Psi_{JT}$  or  $\Psi_{JB}$  with Equation 3 is a good way to estimate  $T_J$  by simply measuring  $T_T$  or  $T_B$ , regardless of the application board size.

DRB  $\Psi_{JB}$

Figure 23.  $\Psi_{JT}$  and  $\Psi_{JB}$  vs Board Size

6

7 8 9 10

-DRB  $\Psi_{JT}$

For a more detailed discussion of why TI does not recommend using  $\theta_{JC(top)}$  to determine thermal characteristics, refer to application report SBVA025, Using New Thermal Metrics, available for download at www.ti.com. For further information, refer to application report SPRA953, IC Package Thermal Metrics, also available on the TI website.

DCQ  $\Psi_{JT}$

35

30 25

20 15 10

5

$\Psi_{JT}$  and  $\Psi_{JB}$  (°C/W)

$\mathsf{DCQ}\,\Psi_{\mathsf{JB}}$

12

(3)

# TPS796xx-Q1

#### www.ti.com.cn

(a) Example DRB (SON) Package Measurement

(b) Example DCQ (SOT-223) Package Measurement

(1)  $T_T$  is measured at the center of both the X- and Y-dimensional axes.

(2)  $\ \ T_B$  is measured below the package lead on the PCB surface.

Figure 24. Measuring Points for  $T_T$  and  $T_B$

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

|                  |               |              |                    | _    |                |                 | (6)                           |                      |              |                         |         |

| TPS79633QDCQRQ1  | ACTIVE        | SOT-223      | DCQ                | 6    | 2500           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR  | -40 to 125   | 79633Q                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(<sup>6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

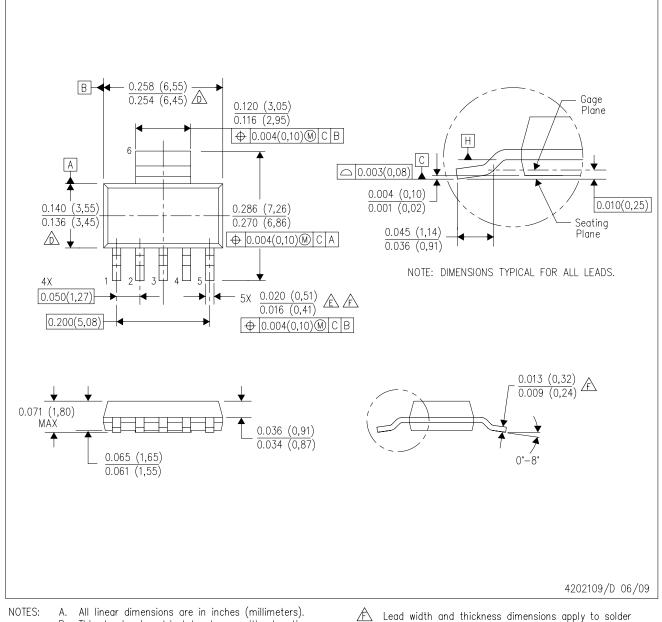

DCQ (R-PDSO-G6)

PLASTIC SMALL-OUTLINE

- Β. This drawing is subject to change without notice. Controlling dimension in inches.

- C.

- Body length and width dimensions are determined at the outermost extremes of the plastic body exclusive of mold flash, tie bar burrs, gate burrs, and interlead flash, but including any mismatch between the top and the bottom of the plastic body.

- 🖄 Lead width dimension does not include dambar protrusion.

- plated leads.

- Interlead flash allow 0.008 inch max. G.

- H. Gate burr/protrusion max. 0.006 inch.

- Ι. Datums A and B are to be determined at Datum H.

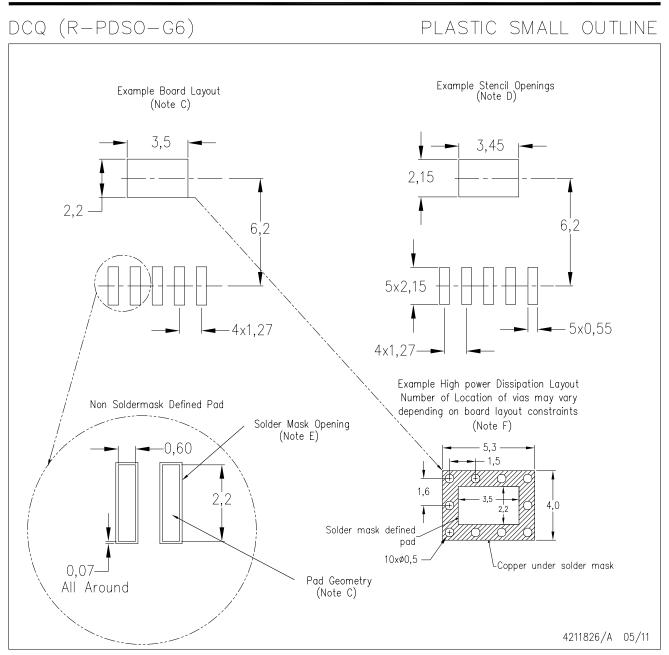

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-SM-782 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

- F. Please refer to the product data sheet for specific via and thermal dissipation requirements.

#### 重要声明和免责声明

Ⅱ 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任:(1)针对您的应用选择合适的TI产品;(2)设计、 验证并测试您的应用;(3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用 所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权 许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI所提供产品均受TI的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2020 德州仪器半导体技术(上海)有限公司