# LMH7322 Dual 700 ps High Speed Comparator with RSPECL Outputs

Check for Samples: LMH7322

DESCRIPTION

### **FEATURES**

- $(V_{CCI} = +5V, V_{CCO} = +5V)$

- Propagation Delay 700 ps

- Overdrive Dispersion 20 mV-1V 75 ps

- · Fast Rise and Fall Times 160 ps

- Wide Supply Range 2.7V to 12V

- Input Common Mode Range Extends 200 mV Below Negative Rail

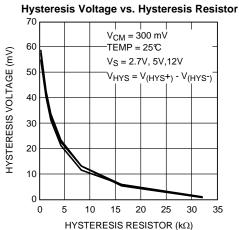

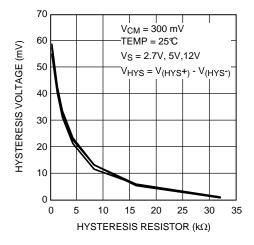

- · Adjustable Hysteresis

- (RS)PECL Outputs (see Application Information)

- (RS)PECL Latch Inputs (see Application Information)

# **APPLICATIONS**

- Digital Receivers

- High-Speed Signal Restoration

- Zero-Crossing Detectors

- High-Speed Sampling

- Window Comparators

- High-Speed Signal Triggering

The LMH7322 is a dual comparator with 700 ps propagation delay, low dispersion of 75 ps and an input voltage range that extends from  $V_{\rm CC}\text{-}1.5\text{V}$  to  $V_{\rm EE}$ . The devices can be operated from a wide supply voltage range of 2.7V to 12V. The adjustable hysteresis adds flexibility and prevents oscillations. Both the outputs and latch inputs of the LMH7322 are RSPECL compatible. When used in combination with a  $V_{\rm CCO}$  supply voltage of 2.5V the outputs have LVDS compatible levels.

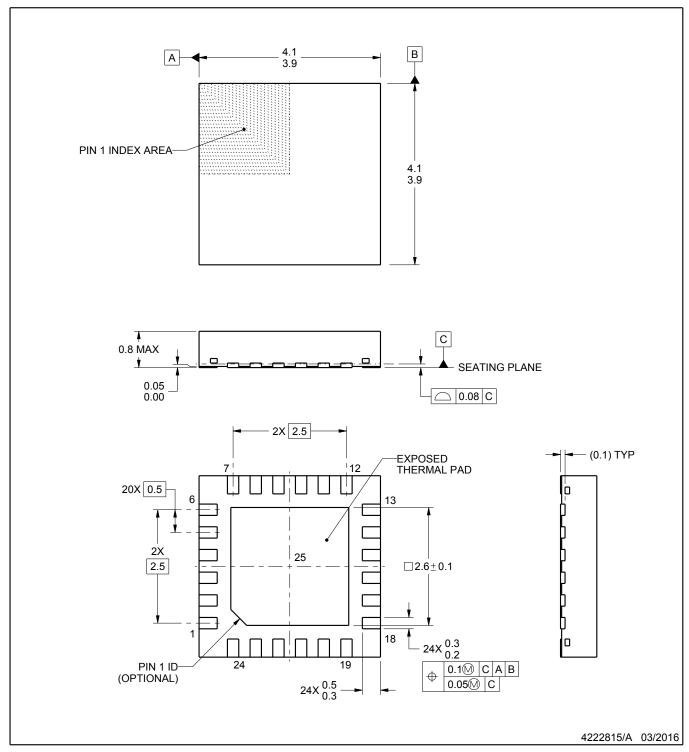

The LMH7322 is available in a 24-pin WQFN package.

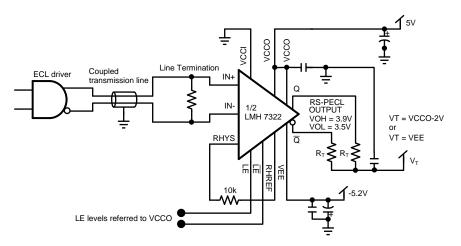

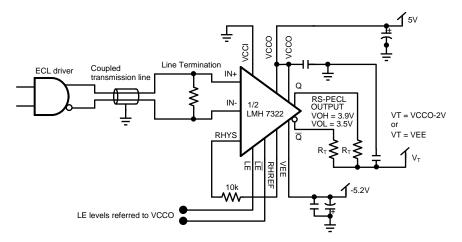

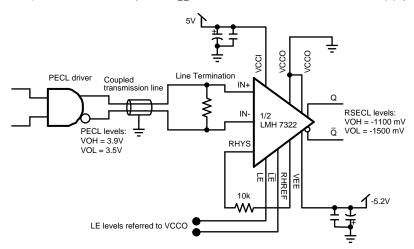

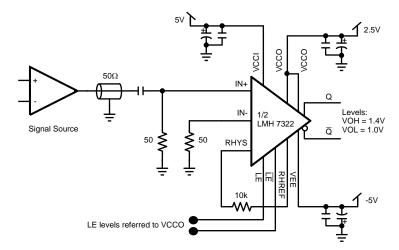

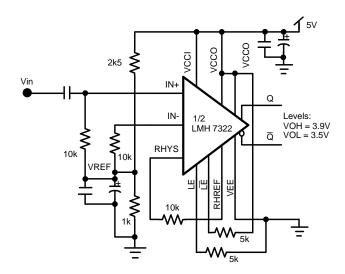

# **Typical Application**

Figure 1. (RS)ECL to RSPECL Converter

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)

| - 1000 c c c c c c c c c c c c c c c c c             |                                                  |

|------------------------------------------------------|--------------------------------------------------|

| ESD Tolerance (3)                                    |                                                  |

| Human Body Model                                     | 2.5 kV                                           |

| Machine Model                                        | 250V                                             |

| Output Short Circuit Duration                        | See (4)(5)(6)                                    |

| Supply Voltages (V <sub>CCx</sub> -V <sub>EE</sub> ) | 13.2V                                            |

| Differential Voltage at Input Pins                   | ±13V                                             |

| Voltage at Input Pins                                | $V_{\text{EE}}$ -0.2V to $V_{\text{CCI}}$ + 0.2V |

| Voltage at LE Pins                                   | $V_{\text{EE}}$ -0.2V to $V_{\text{CCO}}$ +0.2V  |

| Current at Output Pins                               | 25mA                                             |

| Soldering Information:                               |                                                  |

| See Product Folder at www.ti.com and SNOA549         |                                                  |

| Storage Temperature Range                            | −65°C to +150°C                                  |

| Junction Temperature (7)                             | +150°C                                           |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC). Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

- (4) Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

- (5) Short circuit test is a momentary test. See next note.

- The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

- (7) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

# Operating Conditions (1)

| _ 1                                                 |                 |

|-----------------------------------------------------|-----------------|

| Supply Voltage (V <sub>CCx</sub> -V <sub>EE</sub> ) | 2.7V to 12V     |

| Operating Temperature Range (2)(3)                  | −40°C to +125°C |

| Package Thermal Resistance (2)(3)                   |                 |

| 24-Pin WQFN                                         | 38°C/W          |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

- (2) The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>D</sub> = (T<sub>J(MAX)</sub> T<sub>A</sub>)/ θ<sub>JA</sub>. All numbers apply for packages soldered directly onto a PC Board.

(3) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very

- (3) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>. See Applications section for information on temperature de-rating of this device.

#### 12V DC Electrical Characteristics

Unless otherwise specified, all limits are specified for  $T_J$  = 25°C,  $V_{CCI}$  =  $V_{CCO}$  = 12V,  $V_{EE}$  = 0V,  $R_L$  = 50 $\Omega$  to  $V_{CCO}$ -2V,  $V_{CM}$  = 300 mV,  $R_{HYS}$  = 1 k $\Omega$ . **Boldface** limits apply at temperature extremes.

| Symbol              | Parameter                                  | Conditions                                                              | <b>Min</b> (1)       | <b>Typ</b> (2)        | Max<br>(1)            | Units |

|---------------------|--------------------------------------------|-------------------------------------------------------------------------|----------------------|-----------------------|-----------------------|-------|

| INPUT CHARACT       | TERISTICS                                  |                                                                         |                      | <u>I</u>              |                       |       |

| I <sub>B</sub>      | Input Bias Current                         | $V_{IN}$ Differential = 0V; $R_{HYS}$ = 8 k $\Omega$ Biased at $V_{CM}$ | -5                   | -2.9                  |                       | μA    |

| I <sub>OS</sub>     | Input Offset Current                       | V <sub>IN</sub> Differential = 0V                                       | -250                 | 40                    | +250                  | nA    |

| TC I <sub>OS</sub>  | Input Offset Current TC                    | V <sub>IN</sub> Differential = 0V                                       |                      | 0.2                   |                       | nA/°C |

| $V_{OS}$            | Input Offset Voltage                       |                                                                         | -8                   | -2                    | +8                    | mV    |

| TC V <sub>OS</sub>  | Input Offset Voltage TC                    |                                                                         |                      | 12                    |                       | μV/°C |

| V <sub>RI</sub>     | Input Voltage Range                        | for CMRR ≥ 50 dB                                                        | V <sub>EE</sub> -0.2 |                       | V <sub>CCI</sub> -1.5 | V     |

| $V_{RID}$           | Input Differential Voltage Range           |                                                                         | -1                   |                       | +1                    | V     |

| CMRR                | Common Mode Rejection Ratio                | $0V \le V_{CM} \le V_{CC1} - 0.2$                                       |                      | 80                    |                       | dB    |

| PSRR                | Power Supply Rejection Ratio               |                                                                         |                      | 80                    |                       | dB    |

| A <sub>V</sub>      | Active Gain                                |                                                                         |                      | 53                    |                       | dB    |

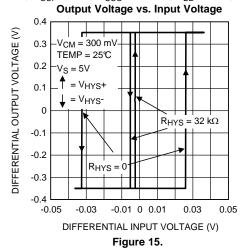

| Hyst                | Hysteresis                                 | $V_{HYS} = V_{(HYS^+)} - V_{(HYS^-)}$ , $R_{HYS} = 0\Omega$             | 25                   | 50                    | 75                    | mV    |

| LATCH ENABLE        | CHARACTERISTICS                            |                                                                         |                      |                       |                       |       |

| I <sub>B-LE</sub>   | Latch Enable Bias Current                  | Biased at RSPECL Level                                                  |                      | 3                     | 10                    | μA    |

| V <sub>OS-LE</sub>  | Latch Enable Offset Voltage                | Biased at RSPECL Level                                                  |                      | -5                    |                       | mV    |

| V <sub>RI-LE</sub>  | Latch Enable Voltage Range                 | for CMRR ≥ 50 dB                                                        | V <sub>EE</sub> +1.4 |                       | V <sub>CCO</sub> -0.8 | V     |

| V <sub>RID-LE</sub> | Latch Enable Differential Voltage<br>Range |                                                                         |                      | ±0.4                  |                       | V     |

| OUTPUT CHARA        | CTERISTICS                                 |                                                                         |                      |                       |                       |       |

| V <sub>OH</sub>     | Output Voltage High                        | V <sub>IN</sub> Differential = 50 mV                                    |                      | V <sub>CCO</sub> -1.1 |                       | mV    |

| V <sub>OL</sub>     | Output Voltage Low                         | V <sub>IN</sub> Differential = 50 mV                                    |                      | V <sub>CCO</sub> -1.5 |                       | mV    |

| V <sub>OD</sub>     | Output Voltage Differential                | V <sub>IN</sub> Differential = 50 mV                                    |                      | 360                   |                       | mV    |

| POWER SUPPLI        | ES                                         |                                                                         | -                    |                       |                       |       |

| I <sub>VCCI</sub>   | V <sub>CCI</sub> Supply Current/ Channel   |                                                                         |                      | 6.5                   | 10<br><b>12</b>       | mA    |

| Ivcco               | V <sub>CCO</sub> Supply Current/ Channel   | Load Current Excluded                                                   |                      | 16.3                  | 20<br><b>25</b>       | mA    |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

### 12 AC Electrical Characteristics

Unless otherwise specified, all limits are specified for  $T_J$  = 25°C,  $V_{CCI}$  =  $V_{CCO}$  = 12V,  $V_{EE}$  = 0V,  $R_L$  = 50 $\Omega$  to  $V_{CCO}$ -2V,  $V_{CM}$  = 300 mV,  $R_{HYS}$  = none. **Boldface** limits apply at temperature extremes.

| Symbol | Parameter           | Conditions                                                         | <b>Min</b><br>(1) | Typ<br>(2) | Max<br>(1) | Units |

|--------|---------------------|--------------------------------------------------------------------|-------------------|------------|------------|-------|

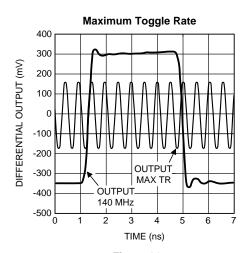

| TR     | Maximum Toggle Rate | Overdrive = ±50 mV; C <sub>L</sub> = 2 pF<br>@ 50% of Output Swing |                   | 4          |            | Gb/s  |

|        | Minimum Pulse Width | Overdrive = ±50 mV; C <sub>L</sub> = 2 pF<br>@ 50% of Output Swing |                   | 255        |            | ps    |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

# 12 AC Electrical Characteristics (continued)

Unless otherwise specified, all limits are specified for  $T_J = 25^{\circ}\text{C}$ ,  $V_{CCI} = V_{CCO} = 12\text{V}$ ,  $V_{EE} = 0\text{V}$ ,  $R_L = 50\Omega$  to  $V_{CCO}$ -2V,  $V_{CM} = 300$  mV,  $R_{HYS} = \text{none.}$ **Boldface** limits apply at temperature extremes.

| Symbol                  | Parameter                                                               | Conditions                                                                                           | <b>Min</b><br>(1) | <b>Typ</b> (2) | Max<br>(1) | Units |

|-------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------|----------------|------------|-------|

| t <sub>jitter-RMS</sub> | RMS Random Jitter                                                       | Overdrive = ±100 mV; C <sub>L</sub> = 2 pF<br>Center Frequency = 140 MHz<br>Bandwidth = 10 Hz–20 MHz |                   | 702            |            | fs    |

| t <sub>PDH</sub>        | Propagation Delay.                                                      | Overdrive 20 mV                                                                                      |                   | 818            |            |       |

|                         | (see Figure 19 application note)                                        | Overdrive 50 mV                                                                                      |                   | 723            |            | ps    |

|                         | Input SR = Constant                                                     | Overdrive 100 mV                                                                                     |                   | 708            |            |       |

|                         | V <sub>IN</sub> Startvalue = V <sub>REF</sub> −100 mV                   | Overdrive 1V                                                                                         |                   | 703            |            | ps    |

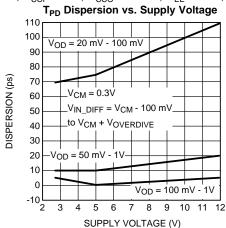

| t <sub>OD-disp</sub>    | Input Overdrive Dispersion                                              | t <sub>PDH</sub> @ Overdrive 20 mV ↔ 100 mV                                                          |                   | 110            |            |       |

|                         |                                                                         | t <sub>PDH</sub> @ Overdrive 100 mV ↔ 1V                                                             |                   | 5              |            | ps    |

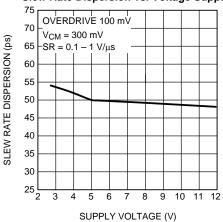

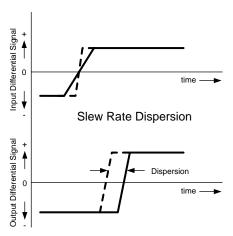

| t <sub>SR-disp</sub>    | Input Slew Rate Dispersion                                              | 0.1 V/ns to 1 V/ns; Overdrive = 100 mV                                                               |                   | 48             |            | ps    |

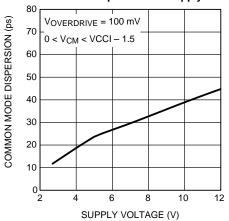

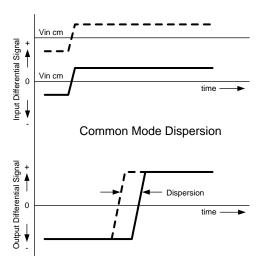

| t <sub>CM-disp</sub>    | Input Common Mode Dispersion                                            | SR = 1 V/ns; Overdrive = 100 mV;<br>$0V \le V_{CM} \le V_{CCI}$ - 1.5V                               |                   | 43             |            | ps    |

| $\Delta t_{PDLH}$       | Q to $\overline{\mathbb{Q}}$ Time Skew $ t_{PDH} - t_{PD\overline{L}} $ | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                            |                   | 24             |            | ps    |

| $\Delta t_{PDHL}$       | Q to $\overline{\mathbb{Q}}$ Time Skew $ t_{PDL} - t_{PD\overline{H}} $ | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                            |                   | 45             |            | ps    |

| t <sub>r</sub>          | Output Rise Time (20%–80%)                                              | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                            |                   | 155            |            | ps    |

| t <sub>f</sub>          | Output Fall Time (20%–80%)                                              | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                            |                   | 155            |            | ps    |

| t <sub>sLE</sub>        | Latch Setup Time                                                        |                                                                                                      |                   | 77             |            | ps    |

| t <sub>hLE</sub>        | Latch Hold Time                                                         |                                                                                                      |                   | 33             |            | ps    |

| t <sub>PD_LE</sub>      | Latch to Output Delay Time                                              |                                                                                                      |                   | 944            |            | ps    |

### **5V DC Electrical Characteristics**

Unless otherwise specified, all limits are specified for  $T_J = 25^{\circ}C$ ,  $V_{CCI} = V_{CCO} = 5V$ ,  $V_{EE} = 0V$ ,  $R_L = 50\Omega$  to  $V_{CCO}$ -2V,  $V_{CM} = 300$  mV,  $R_{HYS} = 1$  k $\Omega$ . **Boldface** limits apply at temperature extremes.

| Symbol             | Parameter                        | Conditions                                                              | <b>Min</b> (1)       | Typ<br>(2) | Max<br>(1)            | Units |

|--------------------|----------------------------------|-------------------------------------------------------------------------|----------------------|------------|-----------------------|-------|

| INPUT CHARAC       | CTERISTICS                       |                                                                         |                      |            | -                     |       |

| I <sub>B</sub>     | Input Bias Current               | $V_{IN}$ Differential = 0V; $R_{HYS}$ = 8 k $\Omega$ Biased at $V_{CM}$ | -5                   | -2.6       |                       | μA    |

| I <sub>OS</sub>    | Input Offset Current             | V <sub>IN</sub> Differential = 0V                                       | -250                 | 40         | +250                  | nA    |

| TC I <sub>OS</sub> | Input Offset Current TC          | V <sub>IN</sub> Differential = 0V                                       |                      | 0.3        |                       | nA/°C |

| V <sub>OS</sub>    | Input Offset Voltage             |                                                                         | -8                   | -2         | +8                    | mV    |

| TC V <sub>OS</sub> | Input Offset Voltage TC          |                                                                         |                      | 12         |                       | μV/°C |

| $V_{RI}$           | Input Voltage Range              | for CMRR ≥ 50 dB                                                        | V <sub>EE</sub> -0.2 |            | V <sub>CCI</sub> -1.5 | V     |

| $V_{RID}$          | Input Differential Voltage Range |                                                                         | -1                   |            | +1                    | V     |

| CMRR               | Common Mode Rejection Ratio      | $0V \le V_{CM} \le V_{CC1} - 0.2$                                       |                      | 80         |                       | dB    |

| PSRR               | Power Supply Rejection Ratio     |                                                                         |                      | 80         |                       | dB    |

| A <sub>V</sub>     | Active Gain                      |                                                                         |                      | 53         |                       | dB    |

| Hyst               | Hysteresis                       | $V_{HYS} = V_{(HYS^{+})} - V_{(HYS^{-})}$ , $R_{HYS} = 0\Omega$         | 25                   | 50         | 75                    | mV    |

| LATCH ENABL        | E CHARACTERISTICS                |                                                                         |                      |            |                       |       |

| I <sub>B-LE</sub>  | Latch Enable Bias Current        | Biased at RSPECL Level                                                  |                      | 3          | 10                    | μA    |

| V <sub>OS-LE</sub> | Latch Enable Offset Voltage      | Biased at RSPECL Level                                                  |                      | +5         |                       | mV    |

| V <sub>RI-LE</sub> | Latch Enable Voltage Range       | for CMRR ≥ 50 dB                                                        | V <sub>EE</sub> +1.4 |            | V <sub>CCO</sub> -0.8 | V     |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

### **5V DC Electrical Characteristics (continued)**

Unless otherwise specified, all limits are specified for  $T_J = 25$ °C,  $V_{CCI} = V_{CCO} = 5$ V,  $V_{EE} = 0$ V,  $R_L = 50\Omega$  to  $V_{CCO}$ -2V,  $V_{CM} = 300$  mV,  $R_{HYS} = 1$  k $\Omega$ .**Boldface** limits apply at temperature extremes.

| Symbol              | Parameter                                  | Conditions            | Min<br>(1) | <b>Typ</b> (2)        | Max<br>(1)      | Units |

|---------------------|--------------------------------------------|-----------------------|------------|-----------------------|-----------------|-------|

| V <sub>RID-LE</sub> | Latch Enable Differential Voltage<br>Range |                       |            | ±0.4                  |                 | V     |

| OUTPUT CHAR         | ACTERISTICS                                |                       | ·          |                       |                 |       |

| V <sub>OH</sub>     | Output Voltage High                        |                       |            | V <sub>CCO</sub> -1.1 |                 | mV    |

| V <sub>OL</sub>     | Output Voltage Low                         |                       |            | V <sub>CCO</sub> -1.5 |                 | mV    |

| V <sub>OD</sub>     | Output Voltage Differential                |                       |            | 355                   |                 | mV    |

| POWER SUPPL         | IES                                        |                       |            |                       |                 |       |

| I <sub>VCCI</sub>   | V <sub>CCI</sub> Supply Current/ Channel   |                       |            | 6.3                   | 10<br><b>12</b> | mA    |

| I <sub>VCCO</sub>   | V <sub>CCO</sub> Supply Current/ Channel   | Load Current Excluded |            | 15.8                  | 20<br><b>25</b> | mA    |

#### **5V AC Electrical Characteristics**

Unless otherwise specified, all limits are specified for  $T_J = 25^{\circ}C$ ,  $V_{CCI} = V_{CCO} = 5V$ ,  $V_{EE} = 0V$ ,  $R_L = 50\Omega$  to  $V_{CCO}$ -2V,  $V_{CM} = 300$  mV,  $R_{HYS} = none$ . **Boldface** limits apply at temperature extremes.

| Symbol                  | Parameter                                                               | Conditions                                                                                           | <b>Min</b> (1) | Typ | Max<br>(1) | Units |

|-------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------|-----|------------|-------|

| TR                      | Maximum Toggle Rate                                                     | Overdrive = ±50 mV; C <sub>L</sub> = 2 pF<br>@ 50% of Output Swing                                   |                | 3.9 |            | Gb/s  |

|                         | Minimum Pulse Width                                                     | Overdrive = ±50 mV; C <sub>L</sub> = 2 pF<br>@ 50% of Output Swing                                   |                | 260 |            | ps    |

| t <sub>jitter_RMS</sub> | RMS Random Jitter                                                       | Overdrive = ±100 mV; C <sub>L</sub> = 2 pF<br>Center Frequency = 140 MHz<br>Bandwidth = 10 Hz–20 MHz |                | 572 |            | fs    |

| t <sub>PDLH</sub>       | Propagation Delay.                                                      | Overdrive 20 mV                                                                                      |                | 783 |            |       |

|                         | (see Figure 19 application note)                                        | Overdrive 50 mV                                                                                      |                | 718 |            | ps    |

|                         | Input SR = Constant $V_{IN}$ startvalue = $V_{REF}$ - 100 mV            | Overdrive 100 mV                                                                                     |                | 708 |            |       |

|                         |                                                                         | Overdrive 1V                                                                                         |                | 708 |            | ps    |

| t <sub>OD-disp</sub>    | Input Overdrive Dispersion                                              | t <sub>PDH</sub> @ Overdrive 20 mV ↔ 100 mV                                                          |                | 75  |            |       |

| ·                       |                                                                         | t <sub>PDH</sub> @ Overdrive 100 mV ↔ 1V                                                             |                | 5   |            | ps    |

| t <sub>SR-disp</sub>    | Input Slew Rate Dispersion                                              | 0.1 V/ns to 1 V/ns; Overdrive = 100 mV                                                               |                | 50  |            | ps    |

| t <sub>CM-disp</sub>    | Input Common Mode Dispersion                                            | $SR = 1 \text{ V/ns}$ ; Overdrive = 100 mV; $0V \le V_{CM} \le V_{CCI}$ - 1.5V                       |                | 24  |            | ps    |

| $\Delta t_{PDLH}$       | Q to $\overline{\mathbb{Q}}$ Time Skew $ t_{PDH} - t_{PD\overline{L}} $ | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                            |                | 29  |            | ps    |

| $\Delta t_{PDHL}$       | Q to Q Time Skew  t <sub>PDL</sub> - t <sub>PDH</sub>                   | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                            |                | 47  |            | ps    |

| t <sub>r</sub>          | Output Rise Time (20%–80%)                                              | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                            |                | 160 |            | ps    |

| t <sub>f</sub>          | Output Fall Time (20%–80%)                                              | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                            |                | 160 |            | ps    |

| t <sub>sLE</sub>        | Latch Setup Time                                                        |                                                                                                      |                | 95  |            | ps    |

| t <sub>hLE</sub>        | Latch Hold Time                                                         |                                                                                                      |                | 29  |            | ps    |

| t <sub>PD_LE</sub>      | Latch to Output Delay Time                                              |                                                                                                      |                | 893 |            | ps    |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

## 2.7V DC Electrical Characteristics

Unless otherwise specified, all limits are specified for  $T_J = 25^{\circ}\text{C}$ ,  $V_{\text{CCI}} = V_{\text{CCO}} = 2.7\text{V}$ ,  $V_{\text{EE}} = 0\text{V}$ ,  $R_L = 50\Omega$  to  $V_{\text{CCO}}$ -2V,  $V_{\text{CM}} = 300 \text{ mV}$ ,  $R_{\text{HYS}} = 1 \text{ k}\Omega$ . **Boldface** limits apply at temperature extremes.

| Symbol              | Parameter                                | Conditions                                                              | Min<br>(1)               | Typ<br>(2)            | Max<br>(1)                | Units |

|---------------------|------------------------------------------|-------------------------------------------------------------------------|--------------------------|-----------------------|---------------------------|-------|

| INPUT CHAR          | ACTERISTICS                              |                                                                         |                          |                       |                           |       |

| I <sub>B</sub>      | Input Bias Current                       | $V_{IN}$ Differential = 0V; $R_{HYS}$ = 8 k $\Omega$ Biased at $V_{CM}$ | -5                       | -2.5                  |                           | μA    |

| Ios                 | Input Offset Current                     | V <sub>IN</sub> Differential = 0V                                       | -250                     | 40                    | +250                      | nA    |

| TC I <sub>OS</sub>  | Input Offset Current TC                  | V <sub>IN</sub> Differential = 0V                                       |                          | 0.2                   |                           | nA/°C |

| Vos                 | Input Offset Voltage                     |                                                                         | -8                       | -2                    | +8                        | mV    |

| TC V <sub>OS</sub>  | Input Offset Voltage TC                  |                                                                         |                          | 12                    |                           | μV/°C |

| $V_{RI}$            | Input Voltage Range                      | for CMRR ≥ 50 dB                                                        | V <sub>EE</sub> -0<br>.2 |                       | V <sub>CCI</sub> -<br>1.5 | V     |

| $V_{RID}$           | Input Differential Voltage Range         |                                                                         | -1                       |                       | +1                        | V     |

| CMRR                | Common Mode Rejection Ratio              | $0V \le V_{CM} \le V_{CC1}-2$                                           |                          | 80                    |                           | dB    |

| PSRR                | Power Supply Rejection Ratio             |                                                                         |                          | 80                    |                           | dB    |

| $A_V$               | Active Gain                              |                                                                         |                          | 53                    |                           | dB    |

| Hyst                | Hysteresis                               | $V_{HYS} = V_{(HYS^{+})} - V_{(HYS^{-})}$ , $R_{HYS} = 0\Omega$         | 25                       | 50                    | 75                        | mV    |

| LATCH ENAB          | BLE CHARACTERISTICS                      |                                                                         |                          |                       |                           |       |

| I <sub>B-LE</sub>   | Latch Enable Bias Current                | Biased at RSPECL Level                                                  |                          | 3                     | 10                        | μΑ    |

| V <sub>OS-LE</sub>  | Latch Enable Offset Voltage              | Biased at RSPECL Level                                                  |                          | -5                    |                           | mV    |

| $V_{\text{RI-LE}}$  | Latch Enable Voltage Range               | for CMRR ≥ 50 dB                                                        | V <sub>EE</sub> +1<br>.4 |                       | V <sub>CCO</sub> -<br>0.8 | V     |

| $V_{RID\text{-}LE}$ | Latch Enable Differential Voltage Range  |                                                                         |                          | ±0.4                  |                           | ٧     |

| OUTPUT CHA          | ARACTERISTICS                            |                                                                         |                          |                       |                           |       |

| V <sub>OH</sub>     | Output Voltage High                      |                                                                         |                          | V <sub>CCO</sub> -1.1 |                           | mV    |

| V <sub>OL</sub>     | Output Voltage Low                       |                                                                         |                          | V <sub>CCO</sub> -1.5 |                           | mV    |

| V <sub>OD</sub>     | Output Voltage Differential              |                                                                         |                          | 350                   |                           | mV    |

| POWER SUPI          | PLIES                                    |                                                                         |                          |                       |                           |       |

| I <sub>VCCI</sub>   | V <sub>CCI</sub> Supply Current/ Channel |                                                                         |                          | 6.2                   | 10<br><b>12</b>           | mA    |

| I <sub>VCCO</sub>   | V <sub>CCO</sub> Supply Current/ Channel | Load Current Excluded                                                   |                          | 15.5                  | 20<br><b>25</b>           | mA    |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

#### 2.7V AC Electrical Characteristics

Unless otherwise specified, all limits are specified for  $T_J = 25^{\circ}C$ ,  $V_{CCI} = V_{CCO} = 2.7V$ ,  $V_{EE} = 0V$ ,  $R_L = 50\Omega$  to  $V_{CCO}$ -2V,  $V_{CM} = 300$  mV,  $R_{HYS} = none$ . **Boldface** limits apply at temperature extremes.

| Symbol | Parameter           | Conditions                                                         | Min<br>(1) | <b>Typ</b> (2) | Max<br>(1) | Units |

|--------|---------------------|--------------------------------------------------------------------|------------|----------------|------------|-------|

| TR     | Maximum Toggle Rate | Overdrive = ±50 mV; C <sub>L</sub> = 2 pF<br>@ 50% of Output Swing |            | 3.8            |            | Gb/s  |

|        | Minimum Pulse Width | Overdrive = ±50 mV; C <sub>L</sub> = 2 pF<br>@ 50% of Output Swing |            | 265            |            | ps    |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

# 2.7V AC Electrical Characteristics (continued)

Unless otherwise specified, all limits are specified for  $T_J = 25^{\circ}C$ ,  $V_{CCI} = V_{CCO} = 2.7V$ ,  $V_{EE} = 0V$ ,  $R_L = 50\Omega$  to  $V_{CCO}$ -2V,  $V_{CM} = 300$  mV,  $R_{HYS} = none$ . **Boldface** limits apply at temperature extremes.

| Symbol                   | Parameter                                                               | Conditions                                                                                          | Min<br>(1) | <b>Typ</b> (2) | Max<br>(1) | Units |

|--------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------|----------------|------------|-------|

| t <sub>jitter_</sub> RMS | RMS Random Jitter                                                       | Overdrive = ±50 mV; C <sub>L</sub> = 2 pF<br>Center Frequency = 140 MHz<br>Bandwidth = 10 Hz–20 MHz |            | 551            |            | fs    |

| t <sub>PDH</sub>         | Propagation Delay.                                                      | Overdrive 20 mV                                                                                     |            | 783            |            |       |

|                          | (see Figure 19 application note)                                        | Overdrive 50 mV                                                                                     |            | 728            |            | ps    |

|                          | Input SR = Constant                                                     | Overdrive 100 mV                                                                                    |            | 713            |            |       |

|                          | V <sub>IN</sub> startvalue = V <sub>REF</sub> – 100 mV                  | Overdrive 1V                                                                                        |            | 718            |            | ps    |

| t <sub>OD-disp</sub>     | Input Overdrive Dispersion                                              | t <sub>PDH</sub> @ Overdrive 20 mV ↔ 100 mV                                                         |            | 70             |            |       |

| •                        |                                                                         | t <sub>PDH</sub> @ Overdrive 100 mV ↔ 1V                                                            |            | 5              |            | ps    |

| t <sub>SR-disp</sub>     | Input Slew Rate Dispersion                                              | 0.1 V/ns to 1 V/ns; Overdrive = 100 mV                                                              |            | 54             |            | ps    |

| t <sub>CM-disp</sub>     | Input Common Mode Dispersion                                            | $SR = 1 \text{ V/ns}$ ; Overdrive = 100 mV; $0V \le V_{CM} \le V_{CCI}$ - 1.5V                      |            | 12             |            | ps    |

| $\Delta t_{PDLH}$        | Q to $\overline{\mathbb{Q}}$ Time Skew $ t_{PDH} - t_{PD\overline{L}} $ | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                           |            | 35             |            | ps    |

| $\Delta t_{PDHL}$        | Q to $\overline{\mathbb{Q}}$ Time Skew $ t_{PDL} - t_{PD\overline{H}} $ | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                           |            | 53             |            | ps    |

| t <sub>r</sub>           | Output Rise Time (20%–80%)                                              | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                           |            | 165            |            | ps    |

| t <sub>f</sub>           | Output Fall Time (20%–80%)                                              | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                           |            | 165            |            | ps    |

| t <sub>sLE</sub>         | Latch Setup Time                                                        |                                                                                                     |            | 102            |            | ps    |

| t <sub>hLE</sub>         | Latch Hold Time                                                         |                                                                                                     |            | 37             |            | ps    |

| t <sub>PD LE</sub>       | Latch to Output Delay Time                                              |                                                                                                     |            | 906            |            | ps    |

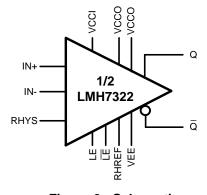

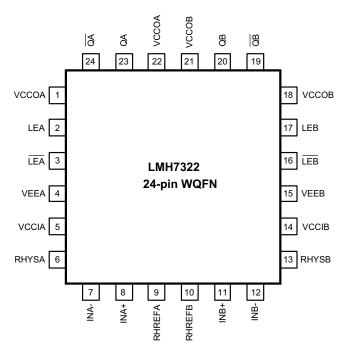

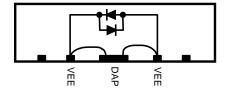

# **Connection Diagrams**

Figure 2. Schematic

Figure 3. Footprint

Copyright © 2007–2013, Texas Instruments Incorporated

Submit Documentation Feedback

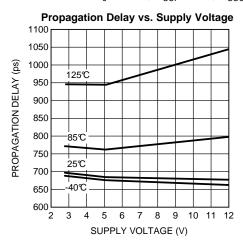

# **Typical Performance Characteristics**

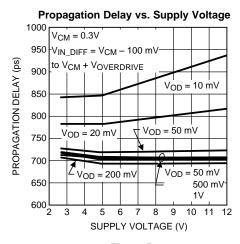

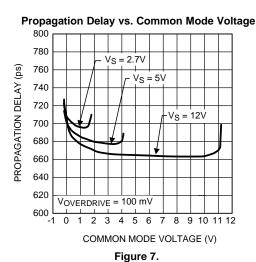

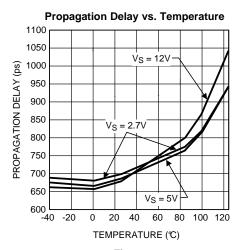

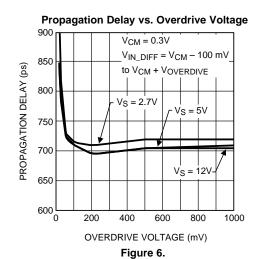

At  $T_J = 25$ °C;  $V_{CCI} = +5V$ ;  $V_{CCO} = +3.3V$ ;  $V_{EE} = -5V$ ; unless otherwise specified.

Figure 4.

Figure 5.

Figure .

Propagation Delay vs. Slew Rate

900

850

VS = 2.7V

800

750

VS = 12V

700

VS = 5V

OVERDRIVE 100 mV

VCM = 300 mV

100 200 300 400 500 600 700 800 900 1000

SLEW RATE (V/µs)

Figure 8.

Submit Documentation Feedback

# **Typical Performance Characteristics (continued)**

At  $T_J = 25$ °C;  $V_{CCI} = +5V$ ;  $V_{CCO} = +3.3V$ ;  $V_{EE} = -5V$ ; unless otherwise specified.

Figure 9.

### Common Mode Dispersion vs. Supply Voltage

Figure 11.

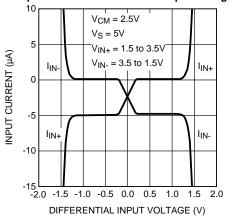

#### Input Current vs. Differential Input Voltage

Figure 13.

# Slew Rate Dispersion vs. Voltage Supply

Figure 10.

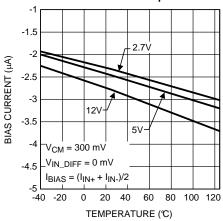

#### Bias Current vs. Temperature

Figure 12.

Figure 14.

# **Typical Performance Characteristics (continued)**

At  $T_J = 25^{\circ}C$ ;  $V_{CCI} = +5V$ ;  $V_{CCO} = +3.3V$ ;  $V_{EE} = -5V$ ; unless otherwise specified.

Figure 16.

Submit Documentation Feedback

#### APPLICATION INFORMATION

#### Introduction

The LMH7322 is a high speed comparator with RS(P)ECL (Reduced Swing Positive Emitter Coupled Logic) outputs, and is compatible with LVDS (Low Voltage Differential Signaling) if V<sub>CCO</sub> is set to 2.5V. The use of complementary outputs gives a high level of suppression for common mode noise. The very fast rise and fall times of the LMH7322 enable data transmission rates up to several Gigabits per second (Gbps). The LMH7322 inputs have a common mode voltage range that extends 200 mV below the negative supply voltage thus allowing ground sensing in case of single supply. The rise and fall times of the LMH7322 are about 160 ps, while the propagation delay time is about 700 ps. The LMH7322 can operate over the full supply voltage range of 2.7V to 12V, while using single or dual supply voltages. This is a very useful feature because it provides a flexible way to interface between several high speed logic families. Several setups are shown in the application information section "Interface Between Logic Families". The outputs are referenced to the positive V<sub>CCO</sub> supply rail. The supply current is 23 mA at 5V (per comparator, load current excluded.) The LMH7322 is available in a 24-Pin WQFN package.

The following topics will be discussed in this application section.

- Input and output topology

- Specification definitions

- Propagation delay and dispersion

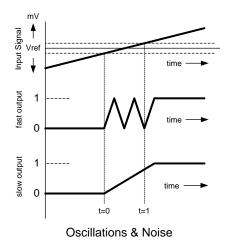

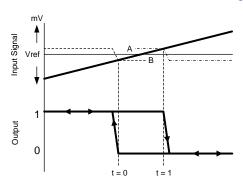

- Hysteresis and oscillations

- Output

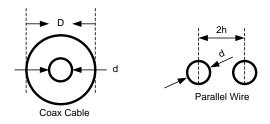

- Applying transmission lines

- **PCB** layout

# **Input & Output Topology**

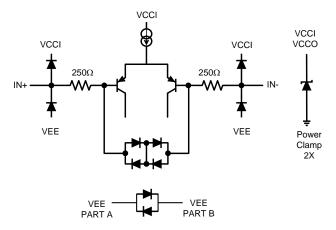

All input and output pins are protected against excessive voltages by ESD diodes. These diodes are conducting from the negative supply to the positive supply. As can be seen in Figure 17, both inputs are connected to these diodes. Further protection of the inputs is provided by the two resistors of  $250\Omega$ , in conjunction with the string of anti-parallel diodes connected between both bases of the input stage. This combination of resistors and diodes reduces excessive input voltages over the input stage, but is low enough to maintain switching speed to the output signal.

Protection against excessive supply voltages is provided by a power clamp between V<sub>CC</sub> and GND.

When using this part be aware of situations in which the differential input voltage level is such that these diodes are conducting. In this case the input current is raised far above the normal value stated in the datasheet tables because input current is flowing through the bypass diode string between both inputs.

Figure 17. Equivalent Input Circuitry

Product Folder Links: LMH7322

Copyright © 2007-2013, Texas Instruments Incorporated

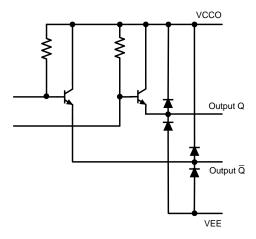

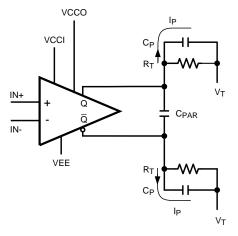

The output stage of the LMH7322 is built using two emitter followers, which are referenced to the  $V_{CCO}$  (see Figure 18.) Each of the output transistors is active when a current is flowing through any external output resistor connected to a lower supply rail. The output structure is actually the same as for all other ECL devices. Activating the outputs is done by connecting the emitters to a termination voltage which lies 2V below the V<sub>CCO</sub>. In this case a termination resistor of  $50\Omega$  can be used and a transmission line of  $50\Omega$  can be driven. Another method is to connect the emitters through a resistor to the most negative supply by calculating the right value for the emitter current in accordance with the datasheet tables. Both methods are useful, and it is up to the customer which method is used. Using  $50\Omega$  to the termination voltage means the introduction of an extra supply in the system, while using resistors to a negative supply means the use of resistors that are much larger than  $50\Omega$  and a more constant output current per stage. The following calculation will show the difference. In this example a V<sub>CCO</sub> of 2.5V is used and a  $V_T$  of  $V_{CCO}$ -2V and a negative supply of -5V. When connecting the outputs through a  $50\Omega$ resistor to the V<sub>T</sub>, the output currents for the high and the low state are respectively 18 mA and 10 mA. Connecting the outputs through a  $400\Omega$  resistor to the -5V supply the output currents for the high and the low state are respectively 16 mA and 15 mA. Higher resistor values to the V<sub>EE</sub> will further reduce power consumption but will cause a slower transition of the output stage. In the case that this will not harm your application it is a useful method to reduce power consumption.

Figure 18. Equivalent Output Circuitry

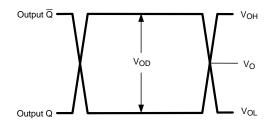

The output voltages for '1' and '0' have a difference of approximately 400 mV and are respectively 1.1V (for the '1') and 1.5V (for the '0') below the  $V_{CCO}$ . This swing of 400 mV is enough to drive any LVDS input but can also be used to drive any ECL or PECL input, when the right supply voltage is chosen, especially the right level for the  $V_{CCO}$ .

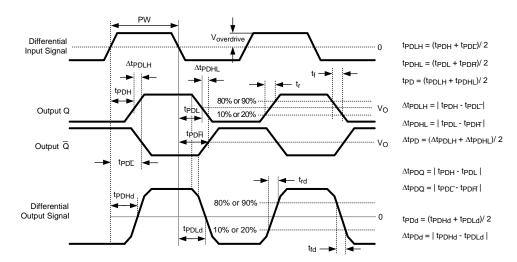

**Table 1. Definitions**

| Symbol             | Text                               | Description                                                                                                                                                                                                                                       |

|--------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>B</sub>     | Input Bias Current                 | Current flowing in or out of the input pins, when both are biased at the $V_{\text{CM}}$ voltage as specified in the tables.                                                                                                                      |

| I <sub>OS</sub>    | Input Offset Current               | Difference between the input bias current of the inverting and non-inverting inputs.                                                                                                                                                              |

| TC I <sub>OS</sub> | Average Input Offset Current Drift | Temperature coefficient of I <sub>OS</sub> .                                                                                                                                                                                                      |

| V <sub>OS</sub>    | Input Offset Voltage               | Voltage difference needed between IN+ and IN- to make the outputs change state, averaged for H to L and L to H transitions.                                                                                                                       |

| TC V <sub>OS</sub> | Average Input Offset Voltage Drift | Temperature coefficient of V <sub>OS</sub> .                                                                                                                                                                                                      |

| V <sub>RI</sub>    | Input Voltage Range                | Voltage which can be applied to the input pin maintaining normal operation.                                                                                                                                                                       |

| V <sub>RID</sub>   | Input Differential Voltage Range   | Differential voltage between positive and negative input at which the input clamp is not working. The difference can be as high as the supply voltage but excessive input currents are flowing through the clamp diodes and protection resistors. |

| CMRR               | Common Mode Rejection Ratio        | Ratio of input offset voltage change and input common mode voltage change.                                                                                                                                                                        |

| PSRR               | Power Supply Rejection Ratio       | Ratio of input offset voltage change and supply voltage change from $V_{S-MIN}$ to $V_{S-MAX}$ .                                                                                                                                                  |

| A <sub>V</sub>     | Active Gain                        | Overall gain of the circuit.                                                                                                                                                                                                                      |

# **Table 1. Definitions (continued)**

| Symbol                                        | Text                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hyst                                          | Hysteresis                                       | Difference between the switching point '0' to '1' and vice versa.                                                                                                                                                                                                                                                                                                                                                                               |

| I <sub>B-LE</sub>                             | Latch Enable Bias Current                        | Current flowing in or out of the input pins, when both are biased at normal PECL levels.                                                                                                                                                                                                                                                                                                                                                        |

| I <sub>OS-LE</sub>                            | Latch Enable Offset Current                      | Difference between the input bias current of the LE and $\overline{\text{LE}}$ pin.                                                                                                                                                                                                                                                                                                                                                             |

| TC I <sub>OS-LE</sub>                         | Temp Coefficient Latch Enable Offset Current     | Temperature coefficient of I <sub>OS-LE</sub> .                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>OS-LE</sub>                            | Latch Enable Offset Voltage                      | Voltage difference needed between LE and $\overline{\text{LE}}$ to place the part in the latched or the transparent state.                                                                                                                                                                                                                                                                                                                      |

| TC V <sub>OS-LE</sub>                         | Temp Coefficient Latch Enable Offset Voltage     | Temperature coefficient of V <sub>OS-LE</sub> .                                                                                                                                                                                                                                                                                                                                                                                                 |

| $V_{RI\text{-}LE}$                            | Latch Enable Voltage Range                       | Voltage which can be applied to the LE input pins without damaging the device.                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{RID\text{-}LE}$                           | Latch Enable Differential Voltage Range          | Differential Voltage between LE and $\overline{\text{LE}}$ at which the clamp isn't working. The difference can be as high as the supply voltage but excessive input currents are flowing through the clamp diodes and protection resistors.                                                                                                                                                                                                    |

| $V_{OH}$                                      | Output Voltage High                              | High state single ended output voltage ( $\overline{Q}$ or Q) (see Figure 34).                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{OL}$                                      | Output Voltage Low                               | Low state single ended output voltage ( $\overline{Q}$ or Q) (see Figure 34).                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{OD}$                                      | average of V <sub>ODH</sub> and V <sub>ODL</sub> | $(V_{ODH} + V_{ODL})/2$ .                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I <sub>VCCI</sub>                             | Supply Current Input Stage                       | Supply current into the input stage.                                                                                                                                                                                                                                                                                                                                                                                                            |

| I <sub>vcco</sub>                             | Supply Current Output Stage                      | Supply current into the output stage while current through the load resistors is excluded.                                                                                                                                                                                                                                                                                                                                                      |

| I <sub>VEE</sub>                              | Supply Current V <sub>EE</sub> pin               | Current flowing to the negative supply pin.                                                                                                                                                                                                                                                                                                                                                                                                     |

| TR                                            | Maximum Toggle Rate                              | Maximum frequency at which the outputs can toggle between the nominal $\rm V_{OH}$ and $\rm V_{OL}.$                                                                                                                                                                                                                                                                                                                                            |

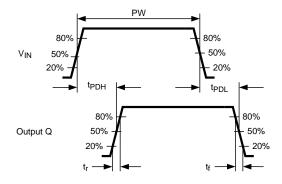

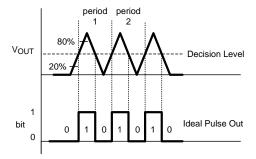

| PW                                            | Pulse Width                                      | Time from 50% of the rising edge of a signal to 50% of the falling edge.                                                                                                                                                                                                                                                                                                                                                                        |

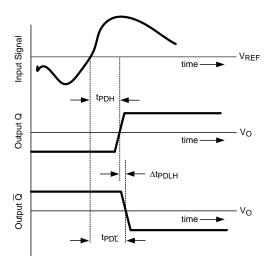

| t <sub>PDH</sub> resp t <sub>PDL</sub>        | Propagation Delay                                | Delay time between the moment the input signal crosses the switching level L to H and the moment the output signal crosses 50% of the rising edge of Q output $(t_{PDH})$ , or delay time between the moment the input signal crosses the switching level H to L and the moment the output signal crosses 50% of the falling edge of Q output $(t_{PDL})$ .                                                                                     |

| t <sub>PD</sub> resp t <sub>PD</sub>          |                                                  | Delay time between the moment the input signal crosses the switching level L to H and the moment the output signal crosses 50% of the falling edge of $\overline{\mathbb{Q}}$ output $(t_{PD\overline{\mathbb{L}}})$ , or delay time between the moment the input signal crosses the switching level H to L and the moment the output signal crosses 50% of the rising edge of $\overline{\mathbb{Q}}$ output $(t_{PD\overline{\mathbb{H}}})$ . |

| t <sub>PDLH</sub>                             |                                                  | Average of t <sub>PDH</sub> and t <sub>PDE</sub> .                                                                                                                                                                                                                                                                                                                                                                                              |

| t <sub>PDHL</sub>                             |                                                  | Average of t <sub>PDL</sub> and t <sub>PDH</sub> .                                                                                                                                                                                                                                                                                                                                                                                              |

| t <sub>PD</sub>                               |                                                  | Average of t <sub>PDLH</sub> and t <sub>PDHL</sub> .                                                                                                                                                                                                                                                                                                                                                                                            |

| t <sub>PDHd</sub> resp<br>t <sub>PDLd</sub>   |                                                  | Delay time between the moment the input signal crosses the switching level L to H and the zero crossing of the rising edge of the differential output signal $(t_{PDHd})$ , or delay time between the moment the input signal crosses the switching level H to L and the zero crossing of the falling edge of the differential output signal $(t_{PDLd})$ .                                                                                     |

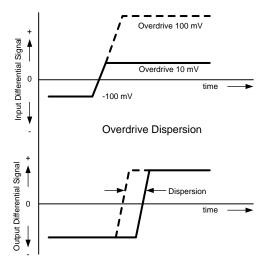

| t <sub>OD-disp</sub>                          | Input Overdrive Dispersion                       | Change in t <sub>PD</sub> for different overdrive voltages at the input pins.                                                                                                                                                                                                                                                                                                                                                                   |

| t <sub>SR-disp</sub>                          | Input Slew Rate Dispersion                       | Change in t <sub>PD</sub> for different slew rates at the input pins.                                                                                                                                                                                                                                                                                                                                                                           |

| t <sub>CM-disp</sub>                          | Input Common Mode Dispersion                     | Change in t <sub>PD</sub> for different common mode voltages at the input pins.                                                                                                                                                                                                                                                                                                                                                                 |

| Δt <sub>PDLH</sub> resp<br>Δt <sub>PDHL</sub> | Q to $\overline{\mathbb{Q}}$ Time Skew           | Time skew between 50% levels of the rising edge of $\overline{Q}$ output and the falling edge of output ( $\Delta t_{PDLH}$ ), or time skew between 50% levels of falling edge of Q output and rising edge of $\overline{Q}$ output ( $\Delta t_{PDHL}$ ).                                                                                                                                                                                      |

| $\Delta t_{PD}$                               | Average Q to Q Time Skew                         | Average of t <sub>PDLH</sub> and t <sub>PDHL</sub> for L to H and H to L transients.                                                                                                                                                                                                                                                                                                                                                            |

| $\Delta t P_{Dd}$                             | Average Diff. Time Skew                          | Average of t <sub>PDHd</sub> and t <sub>PDLd</sub> for L to H and H to L transients.                                                                                                                                                                                                                                                                                                                                                            |

| t <sub>r</sub> / t <sub>rd</sub>              | Output Rise Time (20% - 80%)                     | Time needed for the (single ended or differential) output voltage to change from 20% of its nominal value to 80%.                                                                                                                                                                                                                                                                                                                               |

| t <sub>f</sub> / t <sub>fd</sub>              | Output Fall Time (20% - 80%)                     | Time needed for the (single ended or differential) output voltage to change from 80% of its nominal value to 20%.                                                                                                                                                                                                                                                                                                                               |

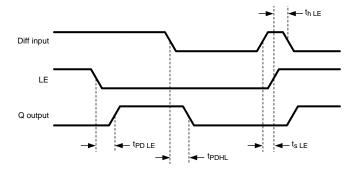

| t <sub>s</sub> LE                             | Latch Setup Time                                 | Time the input signal has to be stable before enabling the latch functionality.                                                                                                                                                                                                                                                                                                                                                                 |

Copyright © 2007–2013, Texas Instruments Incorporated

Submit Documentation Feedback

## **Table 1. Definitions (continued)**

| Symbol             | Text                       | Description                                                                                                                                                                                                                        |

|--------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>h</sub> LE  | Latch Hold Time            | Time the input signal has to remain stable after enabling the latch functionality.                                                                                                                                                 |

| t <sub>PD-LE</sub> | Latch to Output Delay Time | Delay time between the moment the latch input crosses the switching level H to L and the moment the differential output signal crosses the 50% level.  Note: input signal is opposite to output signal when latch becomes enabled. |

Figure 19. Timing Definitions

Figure 20. LE Timing

### **Table 2. PIN DESCRIPTIONS**

| Pin | Name  | Description                     |        | Comment                                                                                                                                        |

|-----|-------|---------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | VCCOA | Positive Supply Output Stage    | part A | The supply pin for the output stage is independent of the supply pin for the input pin. This allows output levels of different logic families. |

| 2.  | LEA   | Latch Enable Input              | part A | Logic '1' sets the part on hold. Logic levels are RSPECL (Reduced Swing PECL) compatible.                                                      |

| 3.  | LEA   | Latch Enable Input Not          | part A | Logic '0' sets the part on hold. Logic levels are RSPECL compatible.                                                                           |

| 4.  | VEEA  | Negative Supply                 | part A | The supply pin for the negative supply is connected to the VEEB via a string of two anti-parallel diodes (see Figure 17)                       |

| 5.  | VCCIA | Positive Supply for Input Stage | part A | The supply pin for the input stage is independent of the supply for the output stage.                                                          |

| 6.  | RHYSA | Hysteresis Resistor             | part A | The hysteresis voltage is determined by connecting a resistor from this pin to RHREFA.                                                         |

| 7.  | INA-  | Negative Input                  | part A | Input for analog voltages between 200 mV below VEEA and 2V below VCCIA.                                                                        |

#### Table 2. PIN DESCRIPTIONS (continued)

| Pin | Name   | Description                              |        | Comment                                                                                                                                        |

|-----|--------|------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.  | INA+   | Positive Input                           | part A | Input for analog voltages between 200 mV below VEEA and 2V below VCCIA.                                                                        |

| 9.  | RHREFA | Reference Voltage Hysteresis<br>Resistor | part A | The hysteresis voltage is determined by connecting a resistor from this pin to RHYSA.                                                          |

| 10. | RHREFB | Reference Voltage Hysteresis<br>Resistor | part B | The hysteresis voltage is determined by connecting a resistor from this pin to RHYSB.                                                          |

| 11. | INB+   | Positive Input                           | part B | Input for analog voltages between 200 mV below VEEB and 2V below VCCIB.                                                                        |

| 12. | INB-   | Negative Input                           | part B | Input for analog voltages between 200 mV below VEEB and 2V below VCCIB.                                                                        |

| 13. | RHYSB  | Hysteresis Resistor                      | part B | The hysteresis voltage is determined by connecting a resistor from this pin to RHREFB.                                                         |

| 14. | VCCIB  | Positive Supply for Input Stage          | part B | The supply pin for the input stage is independent of the supply for the output stage.                                                          |

| 15. | VEEB   | Negative Supply                          | part B | The supply pin for the negative supply is connected to the VEEA via a string of two anti-parallel diodes (see Figure 17).                      |

| 16. | LEB    | Latch Enable Input Not                   | part B | Logic '0' sets the part on hold. Logic levels are RSPECL compatible.                                                                           |

| 17. | LEB    | Latch Enable Input Logic                 | part B | '1' sets the part on hold. Logic levels are RSPECL compatible.                                                                                 |

| 18. | VCCOB  | Positive Supply for Output<br>Stage      | part B | The supply pin for the output stage is independent of the supply pin for the input pin. This allows output levels of different logic families. |

| 19. | QB     | Inverted Output                          | part B | Output levels are determined by the choice of VCCOB.                                                                                           |