### **QUASI-RESONANT PWM SWITCHER**

## Description

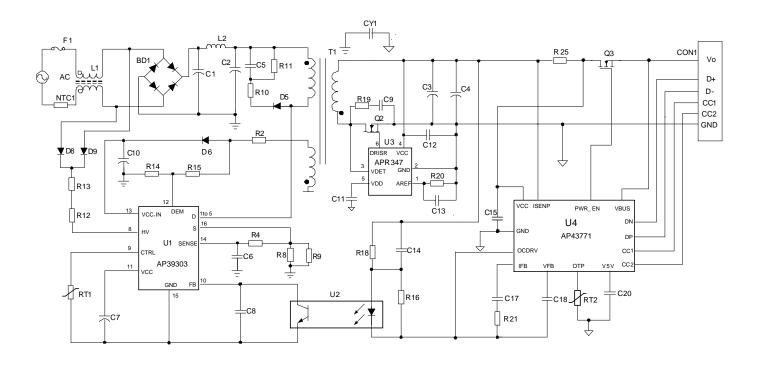

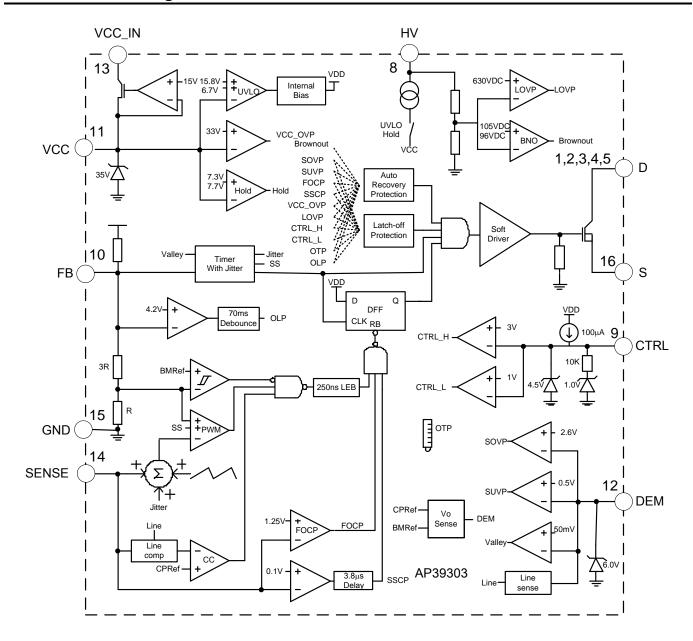

The AP39303 is a highly integrated power switcher with a built-in Quasi-Resonant (QR) PWM controller and a 700V high performance power MOSFET. AP39303 is specially designed for offline power supply that requires ultra-low standby power, high-power density and comprehensive protection. Coordinating with secondary side USBPD or quick charger controller to provide a Flyback charger solution.

At no load or light load, the IC will enter the burst mode to minimize standby power consumption. The minimum switching frequency (typical: 24kHz) is set to avoid the audible noise. When the load increases, the IC will enter QR mode with frequency foldback to improve system efficiency and EMI performance. The maximum switching frequency (typical: 120kHz) is set to clamp the QR frequency to reduce switching power loss. Furthermore, the frequency dithering function is built in to reduce EMI emission.

The AP39303 provides an inner high-voltage start-up function through HV pin which can reduce the standby loss. Moreover, The AP39303 integrates a VCC LDO circuitry, allowing the LDO to regulate the wide range  $V_{\text{CC\_IN}}$  to an acceptable value. This makes the AP39303 to be a good choice in wide range output voltage application.

Internal piecewise linear line compensation ensures constant output power limit over entire universal line voltage range.

Comprehensive protection features are included, such as brown out protection, cycle-by-cycle current limit, VCC Over Voltage Protection (VOVP), Secondary-side Output OVP (SOVP) and UVP (SUVP), internal OTP, Over Load Protection (OLP) and pins' fault protection.

Combined with Diodes Incorporated's synchronous controller APR347, AP39303 system can achieve the higher power conversion efficiency and the better thermal performance.

#### **Features**

- Quasi-Resonant Operation under all Line and Load Condition

- Peak Current Mode Control @ DCM

- High-Voltage Startup

- Built-In 700V High Performance Power MOSFET

- Embedded VCC LDO to Guarantee Wide Range V<sub>CC\_IN</sub> Voltage

- Low VCC Charge Current Reduces Standby Power in Output Short Situation

- Adaptive Burst Mode Operation with Output Voltage

- Adaptive Output Power Limit with Output Voltage

- Non-Audible-Noise Quasi-Resonant Control

- Soft Start during Startup Process

- Frequency Fold Back for High Average Efficiency

- Secondary Winding Short Protection with FOCP

- Frequency Dithering for Reducing EMI

- Vcc Maintain Mode

- Useful Pin Fault Protection:

SENSE Pin Floating

FB/Opto-Coupler Open/Short

Comprehensive System Protection Feature:

Programmable External OTP

Over Load Protection (OLP)

Brown In/Out Protection

Secondary Side OVP (SOVP) and UVP (SUVP)

- HSOP-16 (Type SM) Package

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

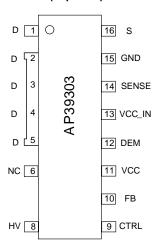

## **Pin Assignments**

### (Top View)

**HSOP-16 (Type SM)**

## **Applications**

- Switching AC-DC Adapter/Charger

- ATX/BTX Auxiliary Power

- Set-Top Box (STB) Power Supply

- Open Frame Switching Power Supply

Notes:

- $1.\ No\ purposely\ added\ lead.\ Fully\ EU\ Directive\ 2002/95/EC\ (RoHS),\ 2011/65/EU\ (RoHS\ 2)\ \&\ 2015/863/EU\ (RoHS\ 3)\ compliant.$

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

# **Typical Applications Circuit**

# **Pin Descriptions**

| Pin Number | Pin Name | Function                                                                         |

|------------|----------|----------------------------------------------------------------------------------|

| 1 to 5     | D        | The Drain of Internal Power MOSFET                                               |

| 6          | NC       | Suspended                                                                        |

| 8          | HV       | High Voltage Input. Sense Line Voltage and Provide Startup Current to Vcc        |

| 9          | CTRL     | Programmable External Protection                                                 |

| 10         | FB       | Feedback. Directly Connected to the Opto-Coupler                                 |

| 11         | VCC      | Supply Voltage of Driver and Control Circuits                                    |

| 12         | DEM      | Valley Detection for QR Control. Sample Vout to Realize SOVP and SUVP Protection |

| 13         | VCC_IN   | Wide Range Input Supply Voltage to Produce Vcc                                   |

| 14         | SENSE    | Sense the Primary Current                                                        |

| 15         | GND      | Signal Ground                                                                    |

| 16         | S        | The Source of Internal Power MOSFET                                              |

# **Functional Block Diagram**

# **Absolute Maximum Ratings** (Note 4)

| Symbol                   | Parameter                                                | Rating    | Unit |

|--------------------------|----------------------------------------------------------|-----------|------|

| VHV                      | HV Pin Input Voltage                                     | 700       | V    |

| V <sub>D</sub>           | Drain Pin Input Voltage                                  | 700       | V    |

| Vcc_in                   | LDO Supply Voltage                                       | 120       | V    |

| Vcc                      | Power Supply Voltage                                     | 34        | V    |

| lo                       | Gate Output Current                                      | 350       | mA   |

| Vfb, Vsense, Vctrl, Vdem | Input Voltage to FB, SENSE, CTRL, DEM                    | -0.3 to 7 | V    |

| θја                      | Thermal Resistance (Junction to Ambient) (Note 5)        | 77        | °C/W |

| P <sub>D</sub>           | Power Dissipation at T <sub>A</sub> < +25°C              | 500       | mW   |

| TJ                       | T <sub>J</sub> Operating Junction Temperature            |           | °C   |

| Tstg                     | T <sub>STG</sub> Storage Temperature Range               |           | °C   |

| ECD                      | Human Body Model (Except HV Pin and VCC_IN Pin) (Note 6) | 3,000     | V    |

| ESD                      | Charged Device Model                                     | 600       | V    |

Notes: 4. Stresses greater than those listed under *Absolute Maximum Ratings* can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to *Absolute Maximum Ratings* for extended periods can affect device reliability.

- 5. Test condition: Device mounted on FR-4 substrate PC board, 2oz copper, with 1inch<sup>2</sup> cooling area.

- 6. HV devices are ESD sensitive (HBM:  $V_{HV}$  = 500V,  $V_{CC\_IN}$  = 450V).

# **Recommended Operating Conditions**

| Symbol         | Parameter           | Min | Max | Unit |

|----------------|---------------------|-----|-----|------|

| Vcc            | Supply Voltage      | 10  | 28  | V    |

| T <sub>A</sub> | Ambient Temperature | -40 | +85 | °C   |

## **Electrical Characteristics** (@T<sub>A</sub> = -40°C to +85°C, V<sub>CC</sub> = 18V, unless otherwise specified.)

| Symbol                            | Parameter                                                             | Condition                                              | Min  | Тур   | Max  | Unit   |  |

|-----------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|------|-------|------|--------|--|

| Supply Voltage (VCC Pin)          |                                                                       |                                                        |      |       |      |        |  |

| Ist                               | Startup Current                                                       | _                                                      | _    | 1     | 15   | μΑ     |  |

| Icc                               | Operating Supply Current                                              | V <sub>FB</sub> = 4V, C <sub>L</sub> = 0nF (Note 8)    | 1.2  | 1.6   | 2.2  | 4      |  |

| ICC-FAULT                         | Operating Current If Fault Occurs                                     | V <sub>FB</sub> = 4V, V <sub>SENSE</sub> = 0V (Note 8) | 0.25 | 0.4   | 0.55 | mA     |  |

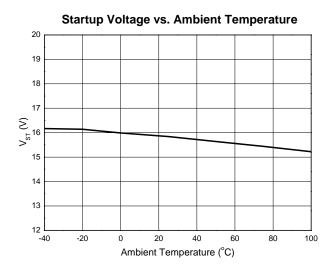

| Vst                               | Startup Voltage                                                       | _                                                      | 14.3 | 15.8  | 16.3 | V      |  |

| VM                                | Vcc Maintain                                                          | _                                                      | _    | 7.3   | _    | V      |  |

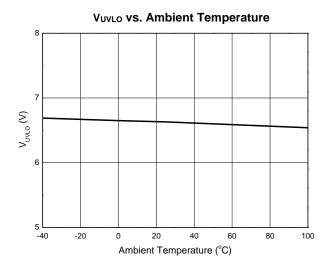

| V <sub>UVLO</sub>                 | Shutdown Voltage                                                      | _                                                      | 6.1  | 6.7   | 7.1  | V      |  |

| Vcc-ovp                           | Vcc OVP                                                               | _                                                      | 32   | 33    | 34   | V      |  |

| PWM Section/C                     | Dscillator Section                                                    |                                                        |      |       |      |        |  |

| fosc-max                          | Maximum Clamp Frequency                                               | (Note 8)                                               | _    | 120   | _    | kHz    |  |

| fosc-min                          | Minimum Clamp Frequency                                               | (Note 8)                                               | 20   | 24    | 28   | kHz    |  |

| fosc-JITTER                       | Valley Blanking Time Dithering                                        | (Note 8)                                               | _    | ±12   | _    | %      |  |

| tDITHER                           | Frequency Dithering Period                                            | _                                                      | _    | 4     | _    | ms     |  |

| Current Sense                     | Section (SENSE Pin)                                                   |                                                        |      |       |      |        |  |

| VSENSE-MAX                        | Current Limit Threshold Voltage                                       | IDEM_SOURCE = 200µA                                    | 0.89 | 0.96  | 1.04 | V      |  |

| V <sub>TH-FOCP</sub>              | FOCP Voltage                                                          | _                                                      | _    | 1.25  | _    | V      |  |

| tdelay-focp                       | FOCP Debounce Time (Note 9)                                           | _                                                      | _    | 7     | _    | Cycles |  |

| tLEB                              | Leading Edge Blanking Time                                            | _                                                      | 150  | 250   | 350  | ns     |  |

| VTH-SSCP                          | SSCP Voltage                                                          | _                                                      | _    | 100   | _    | mV     |  |

| tsoft-st                          | Soft-Start Time                                                       | _                                                      | 3    | 4     | 8    | ms     |  |

| t <sub>DELAY</sub> -SENSE         | Sense Propagation Delay (Note 7)                                      | _                                                      | _    | 100   | _    | ns     |  |

| Feedback Inpu                     | t Section (FB Pin)                                                    |                                                        |      |       | •    | •      |  |

| KFB-SENSE                         | The Ratio of Input Voltage to Current<br>Sense Voltage (Note 7)       | _                                                      | _    | 4     | _    | V/V    |  |

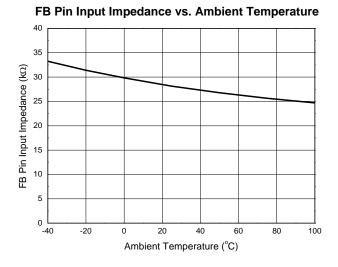

| R <sub>FB</sub>                   | Input Impedance                                                       | _                                                      | 20   | 30    | 40   | kΩ     |  |

| IFB-SOURCE                        | Source Current                                                        | V <sub>FB</sub> = 0V                                   | 0.1  | 0.2   | 0.3  | mA     |  |

| GQR                               | QR Mode Frequency Modulation<br>Slope Versus V <sub>FB</sub> (Note 7) | _                                                      | _    | 94    | _    | kHz/V  |  |

|                                   |                                                                       | V <sub>DEM</sub> <0.75V                                | _    | 0.66  | _    | V      |  |

| $V_{BURST}$                       | Threshold for Entering Burst Mode                                     | 0.75V <v<sub>DEM&lt;1.45V</v<sub>                      | _    | 0.8   | _    | V      |  |

|                                   |                                                                       | V <sub>DEM</sub> >1.45V                                | _    | 0.933 | _    | V      |  |

| ton-max                           | Maximum on Time                                                       | (Note 8)                                               | 16   | 18.5  | 21   | μs     |  |

| tDELAY-OLP                        | Delay of Over Load Protection (Note 7)                                | _                                                      | _    | 70    | _    | ms     |  |

| Vfb-olp                           | Over Load Protection (Note 7)                                         | _                                                      | _    | 4.2   | _    | V      |  |

| Demagnetization Section (DEM Pin) |                                                                       |                                                        |      |       |      |        |  |

| V <sub>TH-DEM</sub>               | De-Magnetization Voltage (Note 7)                                     | _                                                      | _    | 50    | _    | mV     |  |

| V <sub>CLP-L</sub>                | Low Level for Clamping Voltage                                        | IDEM = 200µA (Source Current)                          | -50  | -5    | _    | mV     |  |

| V <sub>CLP-H</sub>                | High Level for Clamping Voltage                                       | IDEM = -1mA (Sink Current)                             | _    | 6     | _    | V      |  |

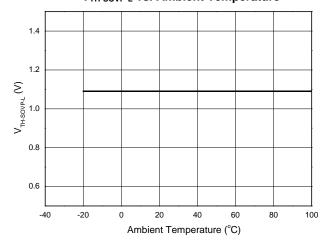

| VTH-SOVP-L                        | SOVP Threshold Voltage for Startup                                    | _                                                      | 1.0  | 1.1   | 1.2  | V      |  |

| V <sub>TH-SOVP-H</sub>            | SOVP Threshold Voltage for Steady<br>State                            | _                                                      | 2.5  | 2.6   | 2.7  | V      |  |

|                                   |                                                                       | +                                                      |      |       | 1    |        |  |

Notes: 7. Guaranteed by design.

S. Data measured in IC test mode.

Cycle-by-Cycle limit delay time contains OCP comparator delay time and driver delay time, Guaranteed by design.

## Electrical Characteristics (continued) (@TA = -40°C to +85°C, Vcc = 18V, unless otherwise specified.)

| Symbol                  | Parameter                               | Condition                                                            | Min      | Тур  | Max  | Unit   |

|-------------------------|-----------------------------------------|----------------------------------------------------------------------|----------|------|------|--------|

| Demagnetization Se      | ection (DEM Pin)                        |                                                                      |          |      |      |        |

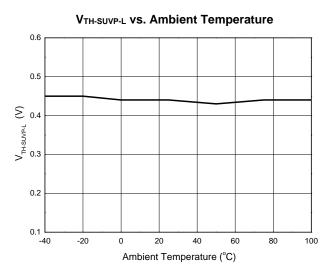

| V <sub>TH-SUVP-L</sub>  | SUVP Threshold Voltage for Hiccup       | _                                                                    | _        | 0.5  | _    | V      |

| tdeb-suvp               | SUVP Debounce Time                      | _                                                                    | _        | 7    | _    | Cycle  |

| tBLANK-SUVP             | SUVP Blank Time after Startup           | _                                                                    | 15       | 20   | 25   | ms     |

| tsample                 | Sample Delay Time (Note 7)              | _                                                                    | _        | 2    | _    | μs     |

| LDO Section ( VCC       | _IN Pin/VCC Pin )                       |                                                                      |          |      | T    |        |

| Vcc                     | LDO Regulated Voltage                   | Vcc Open, Vcc_in = 10V                                               | 9.0      | 9.8  | 10   | V      |

|                         | (Power Supply Voltage)                  | Vcc Open, Vcc_in = 40V                                               | 14       | 15   | 16   | V      |

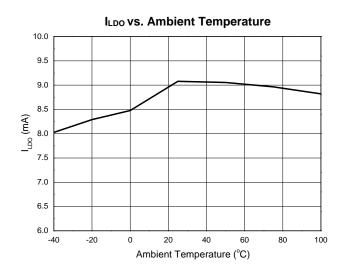

| ILDO                    | Operating Current                       | Vcc=12V, Vcc_in = 40V                                                | 6        | 8    | 11   | mA     |

| Protection Section      | ,                                       | T                                                                    |          |      |      |        |

| ICTRL-SOURCE            | Source Current                          | <u> </u>                                                             | -110     | -100 | -90  | μA     |

| V <sub>TH-CTRL-L</sub>  | Low Threshold                           | _                                                                    | 0.97     | 1    | 1.03 | V      |

| tctrl-blank             | Blank Time when VCTRL is Low            | _                                                                    | _        | 20   | _    | ms     |

| V <sub>TH-CTRL-H</sub>  | High Threshold Voltage                  | _                                                                    | 2.9      | 3    | 3.1  | V      |

| VCTRL-CLP               | Clamp Voltage (Note 11)                 | I <sub>CTRL</sub> = -2mA                                             |          | 4.5  | _    | V      |

| t <sub>DELAY-HICC</sub> | Delay of Hiccup Protection (Note 7)     | SUVP, SOVP, Line OVP,<br>VCC OVP, FOCP, SSCP,<br>CTRL Pin Protection | _        | 7    | _    | Cycles |

| HV Section (HV Pin      | )                                       |                                                                      |          |      |      |        |

| ICHARGE-L               |                                         | Vcc = 0V, V <sub>HV</sub> = 100V                                     | _        | 0.23 | _    | mA     |

| ICHARGE-H               | Charge Current                          | Vcc = 6V, V <sub>HV</sub> = 100V                                     | _        | 2    | _    | mA     |

| ICHARGE-FAULT           | Charge Current if Fault Occurs          | Vcc = 6V, V <sub>HV</sub> = 100V                                     | _        | 65   | _    | μΑ     |

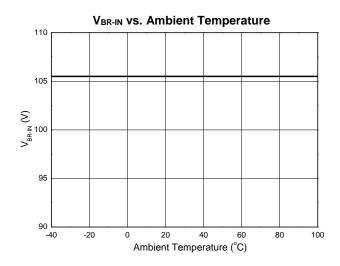

| V <sub>BR</sub> -IN     | Brown In Voltage                        | _                                                                    | 100      | 105  | 110  | V      |

| V <sub>BR</sub> -OUT    | Brown Out Voltage                       | _                                                                    | 92       | 97   | 102  | V      |

| t <sub>BR-IN</sub>      | Delay of Brown In (Note 7)              | _                                                                    | _        | 100  | _    | μs     |

| t <sub>BR-OUT</sub>     | Delay of Brown Out (Note 7)             | _                                                                    | _        | 50   | _    | ms     |

| $V_{LOVP}$              | Line OVP (Note 7)                       | _                                                                    | _        | 630  | _    | V      |

| V <sub>H</sub> V        | HV Pin Input Voltage (Note 10)          | _                                                                    | _        | _    | 700  | V      |

| Internal OTP Sectio     | • • • • • • • • • • • • • • • • • • • • |                                                                      |          |      |      |        |

| OTP                     | OTP Threshold (Note 7)                  | _                                                                    | _        | +150 | _    | °C     |

| Thys                    | OTP Recovery Hysteresis (Note 7)        | _                                                                    | <u> </u> | +125 | _    | °C     |

| tDEB-OTP                | OTP Debounce Time                       | _                                                                    | _        | 7    | _    | Cycle  |

| Power MOSFET Sec        |                                         | •                                                                    | •        |      | •    |        |

| V <sub>(BR)DSS</sub>    | Drain-Source Breakdown Voltage          | _                                                                    | 700      | _    | _    | V      |

| R <sub>DS(ON)</sub>     | Drain-Source On State Resistance        | <u> </u>                                                             | _        | 1.26 | 2    | Ω      |

Notes:

<sup>7.</sup> Guaranteed by design.

8. Data measured in IC test mode.

9. Cycle-by-Cycle limit delay time contains OCP comparator delay time and driver delay time, Guaranteed by design.

<sup>10.</sup> The drain-source voltage is 80% of VDS in the aging condition.

<sup>11.</sup> The sourcing current of CTRL pin must be limited below 5mA. Otherwise it may cause permanent damage to the device.

# **Performance Characteristics**

# **Performance Characteristics** (continued)

### V<sub>TH-SOVP-L</sub> vs. Ambient Temperature

## **Operation Description**

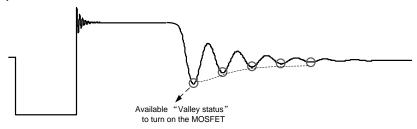

## Quasi-Resonant (QR) Mode

Quasi-Resonant operation is regarded as a soft switching technology which always turns on the primary MOSFET at the valley status of Drain-to-Source voltage (V<sub>DS</sub>). Compared to traditional hard switching, QR switching-on can reduce the switching power loss of MOSFET and achieve good EMI behavior without any additional BOM cost.

Figure 1

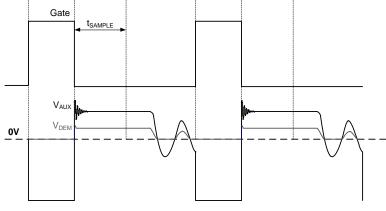

Figure 1 shows the primary MOSFET  $V_{DS}$  waveform. When the secondary-side current flows to zero, the primary inductance  $L_{M}$  and the effective MOSFET output capacitor  $C_{OSS}$  would be resonant. The valley is detected by DEM pin through a pair of voltage divider. At primary MOSFET turning off time, once the voltage on DEM pin is detected below 50mV, one "valley status" is counted. To prevent the false trigger of the  $V_{DS}$  ring caused by leakage inductance, the valley detection function is blanked within the  $t_{SAMPLE}$  ( $2\mu s$ , refer to Figure 6) when primary MOSFET turns off.

Each "valley status" of MOSFET V<sub>DS</sub> will be detected and counted by DEM pin. According to the frequency control strategy of AP39303, one proper "valley status" will be selected to turn on the MOSFET.

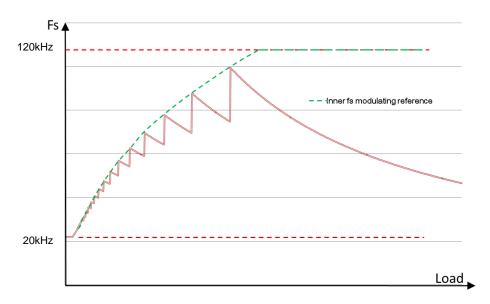

### **Frequency Modulation Strategy**

The AP39303 operates with QR mode, green mode and burst mode to achieve the high efficiency performance.

In general, the AP39303 power system operates with first "valley status" under low line and full load condition, in which the maximum primary peak current and transformer flux density occur. The power system designer is required to choose transformer size and switching frequency according to this worst case condition.

With output load decreasing from full load in the first "valley status", the switching frequency of AP39303 increases correspondingly. In order to avoid performance degrading at very high switching frequency operation, there is a fixed 120kHz maximum frequency limitation in AP39303. Since too high switching frequency will lead to the worse performance, the 120kHz frequency limitation is not preferred to reach in system design. Actually AP39303 has built-in reference in FB pin voltage to adjust "valley status" for green mode operation, as shown in Figure 2. When FB pin voltage decreases to a modulating reference, the first "valley status" is forced to shift to other available "valley status".

The AP39303 has the minimum switching frequency limit of 24kHz to avoid audible noise issue. When the switching frequency decrease to 24kHz with output load decreasing, the switching frequency will keep at 24kHz. When FB pin voltage is lower than VBURST, the power system enters burst mode to reduce the power dissipation under very light load condition.

Figure 2

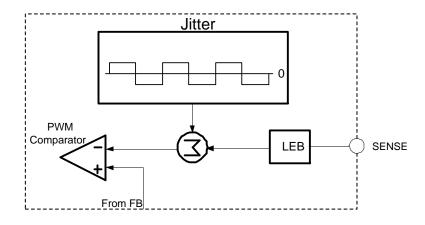

### **Active Frequency Dithering**

To improve the EMI performance, the AP39303 integrates an active frequency dithering function. A consecutive frequency-dithering signal is injected to the SENSE pin after Leading-Edge Blanking (LEB) time. As shown in Figure 3, the frequency-dithering signal is repeating over and over again with a period of 4ms and amplitude of +/-Vs\_JITTER. With the injection of frequency-dithering signal on SENSE pin, the switching frequency will have a periodical excursion to improve the EMI performance.

Figure 3

#### **Current Mode PWM Control**

The AP39303 operates as a current mode controller; the output switch is turned on by every oscillator cycle and turned off when the primary peak current reaches the threshold level established by the FB pin. The primary current signal is converted to a voltage signal on current sense resistor Rs. The relation between primary peak current (IPK) and VFB is:

$$I_{PK} = V_{FB} / 4R_S$$

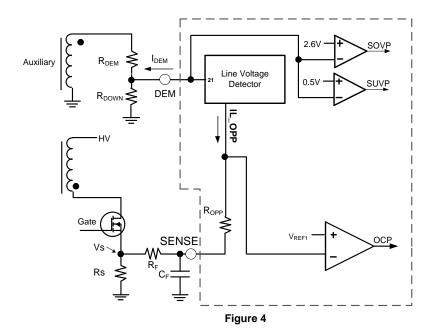

#### **Constant Over Current Protection**

Cycle-by-cycle current limit is a popular method to achieve output over current protection. Actually, the turn-off delay of the MOSFET and the higher switching frequency always result in the higher OCP current at high line voltage. To obtain a constant OCP current value with universal input voltage, AP39303 adopts an effective line compensation circuitry. The function block is illustrated in Figure 4. The current IDEM which reflects line voltage is scaled down and inversed to IL\_OPP within AP39303, this IL\_OPP flows through the inner compensation resistor ROPP and an external filtering resistor RF, and then the final line compensation voltage is formed as:

$$V_S + \frac{Vindc * Naux}{Np * Rdem * 21} * (R_{OPP} + R_F) = V_{REF1}$$

Where  $V_S$  is the sense voltage of  $R_S$

As above formula indicates, changing the compensation voltage at different line voltage is a good way to balance the OCP current. In a real system, usually keep the  $R_{DEM}$  value fixed (220k $\Omega$  is recommended). To change the line compensation voltage, a good solution is to change  $R_F$ . Whenever the  $R_F$  is changed, adjust the  $C_F$  at the same time to offer an enough RC time to filter the spike on SENSE pin.

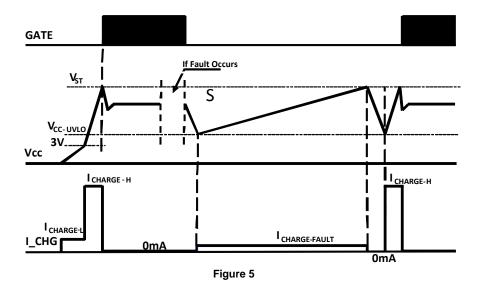

### **HV Start-Up Circuit**

A built-in HV startup circuit in AP39303 can help to simplify the power system design for ultra-low standby application. For AP39303, there are two HV Start-Up charging current: the  $I_{CHARGE-L}$  when  $V_{CC}$  is lower than 3V and the  $I_{CHARGE-H}$  when the  $V_{CC}$  voltage rises above 3V, which can prevent the IC from overheat when  $V_{CC}$  short-to-GND fault happens. The HV startup circuit will stop working and have no additional power dissipation when  $V_{CC}$  voltage reaches the  $V_{ST}$ , then the AP39303 starts working and will supply energy to  $V_{CC}$  from auxiliary winding.

However, the charging process described above is only for the normal system startup condition. Once some system faults occur and the protection process is triggered, AP39303 will shut down and Vcc voltage will begin to decrease. The HV startup circuit starts working again when Vcc voltage decreases below Vcc-uvLo, and charges the Vcc capacitor with current of Icharge-Fault. This special design can reduce the input power dissipation when system fault happens, especially for output short condition. The HV Start-Up circuit working process is illustrated in Figure 5.

#### **Built-In Vcc LDO**

The AP39303 integrates a V<sub>CC</sub> LDO circuitry, the LDO regulates the wide range V<sub>CC\_IN</sub> which is rectified from auxiliary winding to an acceptable value. It makes the AP39303 a good choice in wide range output voltage application.

#### **Brown In/Out Protection**

To avoid potential high-current stress at low line voltage, the AP39303 introduces a reliable brownout protection. The AC line voltage is detected through HV pin, a pair of high-voltage diodes are connected to the AC line which will rectify the AC input voltage to a double-frequency positive voltage referring to GND, a  $20k\Omega$  resistor is recommended to be added to improve the surge immunity. When the voltage across HV pin is higher than  $V_{BR-IN}$  for about  $100\mu$ s of  $t_{BR-IN}$  and  $V_{CC}$  reaches  $V_{ST}$ , the system starts to work. If the HV pin voltage falls below  $V_{BR-OUT}$  and lasts for 50ms of  $t_{BR-OUT}$ , the system will shut down until the line voltage rises over its brown-in voltage again.

#### SOVP/SUVP Protection

The AP39303 provides output OVP and UVP protection function. The auxiliary winding voltage during secondary rectifier conducting period reflects the output voltage. A voltage divide network is connected to the auxiliary winding and DEM pin, the DEM pin will detect the equivalent output voltage with a delay of tsample from the falling edge of GATE driver signal, as shown in Figure 6. The detected voltage will be compared to the SOVP and SUVP threshold voltage Vth-sovP and Vth-suvP. If the SOVP or SUVP threshold is reached continuously by 7 switching cycles, the SOVP or SUVP protection will be triggered, the AP39303 will shut down and the system will restart when the Vcc voltage falls below the UVLO voltage.

To prevent from false-trigger of SUVP during start up process, a blank time of tBLANK-SUVP is set during which the SUVP protection function is ignored.

Figure 6

#### **Externally Triggered Protection**

The AP39303 reserves flexible protection mode for power design. The CTRL pin can achieve external programmable protection. A high threshold of  $V_{TH-CTRL-H}$  is set for any over voltage protection, if the CTRL pin voltage is higher than the threshold for 7 switching cycles, the CTRL-High protection will be triggered. A low threshold of  $V_{TH-CTRL-L}$  is usually used for external over temperature protection. To realize the external OTP, a proper NTC should be connected from the CTRL pin to the ground. An inner current of 100 $\mu$ A flows through the NTC from the CTRL pin. If the CTRL pin voltage is lower than the  $V_{TH-CTRL-L}$  for 32ms duration at least, the CTRL-Low protection will be triggered. Whenever the protection is triggered, the system will stop the output drive signal and will restart after the  $V_{CC}$  voltage falling below the UVLO voltage.

#### **System Protection**

#### LOVP, FOCP, SSCP, VCC OVP, OTP

The AP39303 provides versatile protection to ensure the reliability of the power system. LOVP achieves line voltage overvoltage protection, if the detected AC line voltage is higher than VLOVP for 7 switching cycles, the LOVP protection will be triggered. FOCP protection is an ultra-fast short-current protection which is helpful to avoid catastrophic damage of the system when the secondary rectifier is short. The primary peak current will be monitored by SENSE pin through a primary sense resistor, whenever the sampled voltage reaches the threshold of VTH-FOCP for 7 switching cycles continuously, the FOCP protection will be activated to shut down the switching pulse. SSCP might be triggered at ultra-low DC bus voltage condition or other failure condition that short the SENSE pin to ground. The SSCP module senses the voltage across the primary sense resistor with a delay of 3µs after the rising edge of primary GATE signal, this sensed signal is compared with VTH-SSCP. If it is lower than VTH-SSCP for 7 switching cycles, the SSCP protection will be triggered and the drive signal will be disabled. All these protections described above will restart the system when the Vcc voltage falls below UVLO. Although the external OTP can be easily implemented through CTRL pin, the AP39303 still reserves the inner OTP with a hysteresis for any necessary use.

#### **Vcc Maintain Mode**

During light-load or transient-load condition, VFB will drop and be lower than VBURST, thus the PWM drive signal will be stopped, and there is no energy for transferring to the output. Therefore, the IC VCc supply voltage may decrease to the UVLO threshold voltage and system may enter the unexpected restart mode. To avoid this, the AP39303 holds a so-called Vcc maintain mode which can supply energy to Vcc.

When  $V_{CC}$  decreases to a setting threshold as  $V_{M}$ , the  $V_{CC}$  maintain mode will be awaked and a charging current of  $I_{CHARGE-H}$  will flow to the  $V_{CC}$  pin. With  $V_{CC}$  maintain mode, the  $V_{CC}$  is not easy to touch the shutdown threshold during the startup process and transient load condition. This will also simplify the system design. The minimum  $V_{CC}$  voltage is suggested to be designed a little higher than  $V_{CC}$  maintain threshold thus can achieve the best balance between the power loss and step load performance.

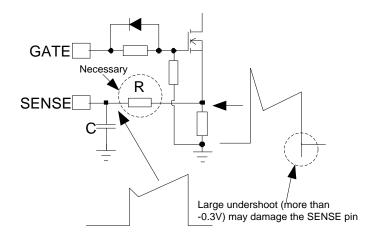

### Leading-Edge Blanking Time

A narrow spike on the leading edge of the current waveform can usually be observed when the power MOSFET is turned on. A 250ns leading-edge blank is built-in to prevent the false-trigger caused by the turn-on spike. During this period, the current limit comparator and the PWM comparator are disabled and the gate driver cannot be switched off.

At the time of turning-off the MOSFET, a negative undershoot (maybe larger than -0.3V) can occur on the SENSE pin. So it is strongly recommended to add a small RC filter or at least connect a resistor "R" on this pin to protect the IC (Shown as Figure 7).

Figure 7

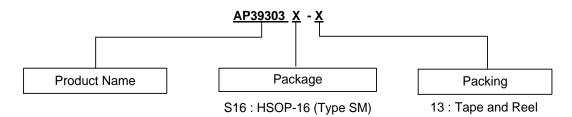

## **Ordering Information**

| 5 (1)         | <b>.</b> .        |            | 13"Tape and Reel   |                    |  |

|---------------|-------------------|------------|--------------------|--------------------|--|

| Part Number   | Package           | Marking ID | Quantity           | Part Number Suffix |  |

| AP39303S16-13 | HSOP-16 (Type SM) | AP39303    | 4000/Tape and Reel | -13                |  |

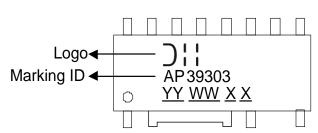

# **Marking Information**

## ( Top View )

YY: Year: 18,19, 20~ <u>WW</u>: Week: 01~52; 52 represents 52 and 53 week

XX: Internal Code

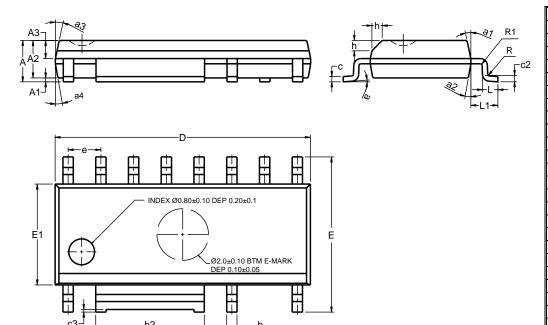

## Package Outline Dimensions (All dimensions in mm)

Please see http://www.diodes.com/package-outlines.html for the latest version.

(1) Package Type: HSOP-16 (Type SM)

| HSOP-16 (Type SM)    |      |         |      |  |  |

|----------------------|------|---------|------|--|--|

| Dim                  | Min  | Max     | Тур  |  |  |

| Α                    | 1.35 | 1.75    | 1.60 |  |  |

| A1                   | 0.10 | 0.25    | 0.15 |  |  |

| A2                   | 1.25 | 1.65    | 1.45 |  |  |

| A3                   | 0.55 | 0.75    | 0.65 |  |  |

| b                    | 0.36 | 0.51    |      |  |  |

| b2                   | 4.17 | 4.32    |      |  |  |

| С                    | 0.17 | 0.25    |      |  |  |

| c2                   |      | 0.25BS0 | 2    |  |  |

| с3                   | 0.00 | 0.15    |      |  |  |

| D                    | 9.80 | 10.00   | 9.90 |  |  |

| Е                    | 5.80 | 6.20    | 6.00 |  |  |

| E1                   | 3.80 | 4.00    | 3.90 |  |  |

| е                    |      | 1.27BS0 | 3    |  |  |

| h                    | 0.30 | 0.50    | 0.40 |  |  |

| L                    | 0.45 | 0.80    | 0.60 |  |  |

| L1                   |      | 1.04REI | F    |  |  |

| R                    | 0.07 |         |      |  |  |

| R1                   | 0.07 |         |      |  |  |

| а                    | 0°   | 8°      |      |  |  |

| a1                   | 10°  | 14°     | 12°  |  |  |

| a2                   | 8°   | 12°     | 10°  |  |  |

| a3                   | 10°  | 14°     | 12°  |  |  |

| a4                   | 8°   | 12°     | 10°  |  |  |

| All Dimensions in mm |      |         |      |  |  |

# **Mechanical Data**

- Moisture Sensitivity: MSL Level 3 per JESD22-A113

- Terminals: Finish Matte Tin Plated Leads, Solderable per JESD22-B102 (3)

- Weight: 0.168 grams (Approximate)

#### **IMPORTANT NOTICE**

- 1. DIODES INCORPORATED AND ITS SUBSIDIARIES ("DIODES") MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes products. Diodes products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of the Diodes products for their intended applications, (c) ensuring their applications, which incorporate Diodes products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- 5. Diodes products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

Copyright © 2020 Diodes Incorporated

www.diodes.com