# LP8725 Power Management Unit for Application or Multimedia Processors and Subsystems

Check for Samples: LP8725

### **FEATURES**

- Two High-Efficiency Step-Down DC-DC Converters, I<sub>OUT</sub> = 600 mA, With a 4-MHz Switching Frequency Using Small 1-µH Inductors, With Options up to 800 mA

- Three Digital LDOs for up to 300-mA Load Current Each

- Two Low-Noise Analog 300-mA LDOs

- Two Low-Input Low-Output Regulators,  $I_{OUT} = 300 \text{ mA}$

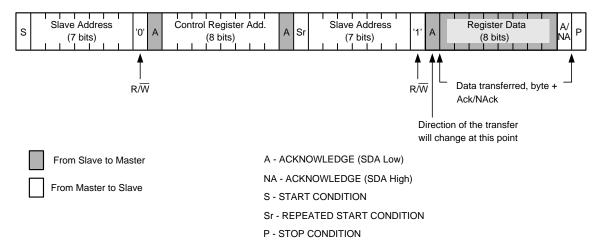

- I<sup>2</sup>C-Compatible Interface for Control of Internal Registers

- Adjustable Startup Sequence Through Serial Interface or Configuration

- **Thermal Shutdown Protection**

### APPLICATIONS

- **Multimedia Processors**

- **Portable Handheld Products**

### **KEY SPECIFICATIONS**

- 190 mV typ. Dropout Voltage on digital LDOs @ 300 mA

- 2% typ. Output Voltage Accuracy on digital and analog LDOs

- 10 µVrms Output Noise on analog LDOs

- ±2% typ. Output Voltage Bucks up to 93% efficiency

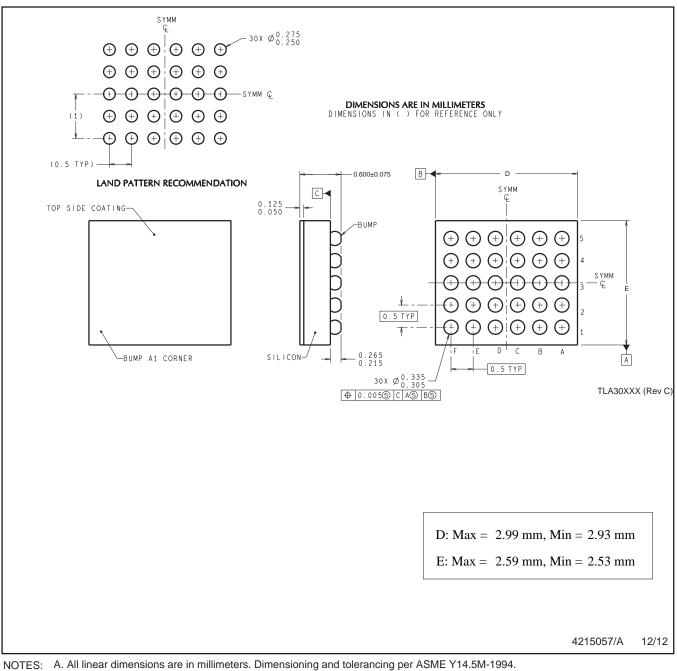

- 30-bump DSBGA package (0.5 mm pitch)

### DESCRIPTION

This device is a multi-function programmable Power Management Unit (PMU), optimized for sub block power solutions. This device integrates two highly efficient 600-mA step-down DC-DC converters configurable up to 800-mA load with Dynamic Voltage Scaling (DVS) via the serial interface, two low-noise analog LDOs, three digital LDOs for up to 300 mA load current each, two Low-Input Low-Output (LILO) regulators, and an I<sup>2</sup>C-compatible serial interface to allow a host controller access to the internal control registers. The device also features programmable power-on sequencing. LDO regulators provide high PSRR and low noise ideally suited for supplying power to both analog and digital loads.

The device can be configured either as a Sub PMU for modules (for example, camera or multimedia modules) or as a stand-alone PMU that powers the processor itself.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

SNVS618G-DECEMBER 2009-REVISED MAY 2013

www.ti.com

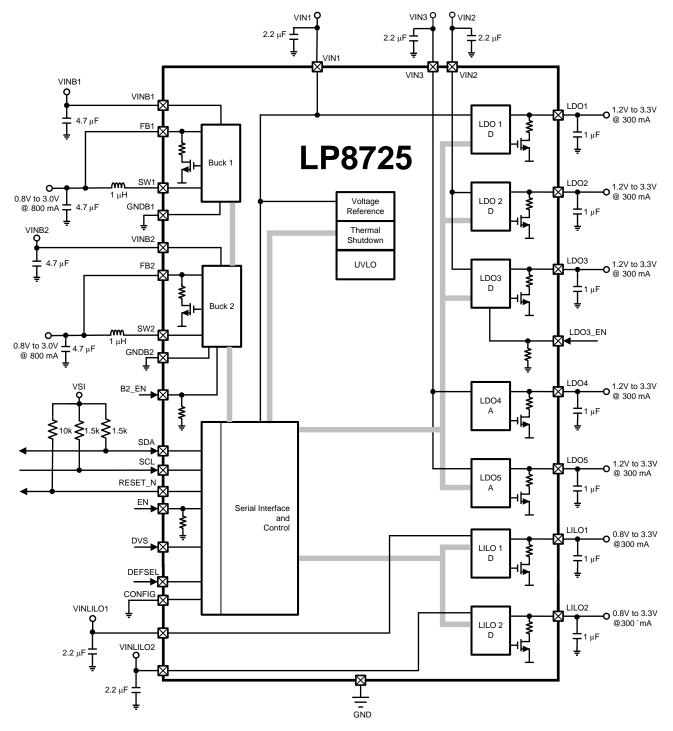

### **TYPICAL APPLICATION (SUB-PMU)**

SNVS618G - DECEMBER 2009 - REVISED MAY 2013

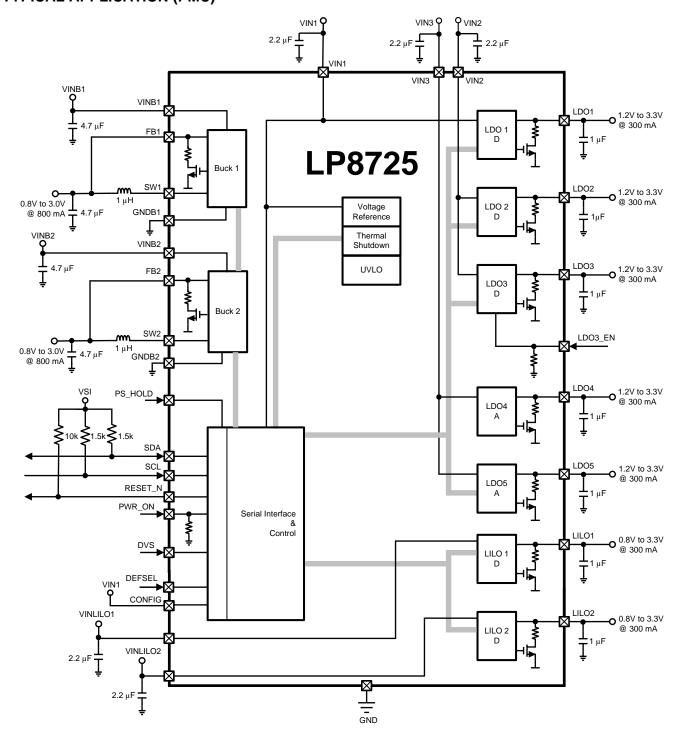

# **TYPICAL APPLICATION (PMU)**

SNVS618G-DECEMBER 2009-REVISED MAY 2013

Texas Instruments

www.ti.com

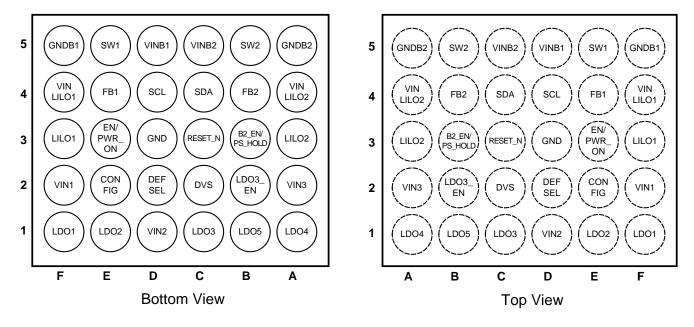

### **CONNECTION DIAGRAMS**

#### Texas Instruments

www.ti.com

#### SNVS618G - DECEMBER 2009 - REVISED MAY 2013

| Name          | Pin No. | Description                                                                                                                                                                                                                                                                                                 |  |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B2_EN/PS_HOLD | B3      | CONFIG=0: B2_EN is the enable for BUCK2 output if this pin is high and if BUCK2_EN register bit is set to 0. (B2_EN and the register bit are logical OR.) Internal 500 K $\Omega$ pull-down resistor in this configuration only. CONFIG=1: PS_HOLD is a power supply hold input from an external processor. |  |

| CONFIG        | E2      | Connect to GND for SUB_PMU or connect to VIN1 for PMU.                                                                                                                                                                                                                                                      |  |

| DEFSEL        | D2      | Control input that sets default voltages and start-up sequence. Must be hard wired to VIN1 or GND for specific application.<br>When DEFSEL=VIN1 then setup 1 is used for default voltages and startup sequences.<br>When DEFSEL=GND then setup 2 is used for default voltages and startup sequences.        |  |

| DVS           | C2      | Dynamic Voltage Scaling (operational when REG 0x00<2> is '0').<br>DVS=1 then BUCK voltage set BUCK1_V1 is in use.<br>DVS=0 then BUCK voltage set BUCK1_V2 is in use.<br>This pin must be driven to its logic high or low whenever the BUCK1 or BUCK2 outputs are enabled.                                   |  |

| EN/PWR_ON     | E3      | CONFIG=0: EN=1 turns on outputs or standby mode if EN=0.<br>CONFIG=1: PWR_ON=1 starts power up sequence after 30 ms of de-bounce time. Internal 500K pull-<br>down resistor.                                                                                                                                |  |

| FB1           | E4      | BUCK1 Feedback. Active pull-down when BUCK1 turns off.                                                                                                                                                                                                                                                      |  |

| FB2           | B4      | BUCK2 Feedback. Active pull-down when BUCK2 turns off.                                                                                                                                                                                                                                                      |  |

| GND           | D3      | IC Ground                                                                                                                                                                                                                                                                                                   |  |

| GNDB1         | F5      | BUCK1 Ground.                                                                                                                                                                                                                                                                                               |  |

| GNDB2         | A5      | BUCK2 Ground.                                                                                                                                                                                                                                                                                               |  |

| LDO1          | F1      | LDO1 output.                                                                                                                                                                                                                                                                                                |  |

| LDO2          | E1      | LDO2 output.                                                                                                                                                                                                                                                                                                |  |

| LDO3          | C1      | LDO3 output.                                                                                                                                                                                                                                                                                                |  |

| LDO3_EN       | B2      | Enable for LDO3 output if this pin is high and if LDO3_EN register bit is set to 0. (LDO3_EN and the register bit are logical OR.) Internal 500 K $\Omega$ pull-down resistor.                                                                                                                              |  |

| LDO4          | A1      | LDO4 output.                                                                                                                                                                                                                                                                                                |  |

| LDO5          | B1      | 05 output                                                                                                                                                                                                                                                                                                   |  |

| LILO1         | F3      | O1 output.                                                                                                                                                                                                                                                                                                  |  |

| LILO2         | A3      | LILO2 output.                                                                                                                                                                                                                                                                                               |  |

| RESET_N       | C3      | CONFIG=0: Goes high typ. 30 ms after EN=1 and goes low when EN=0.<br>CONFIG=1: Goes high typ. 60 ms after PWR_ON=1 and goes low 30 ms after PS_HOLD=0.<br>External pull-up resistor is needed, typical 10 k $\Omega$ .                                                                                      |  |

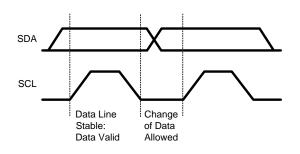

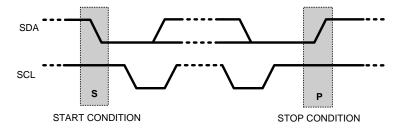

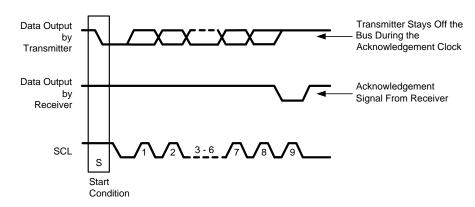

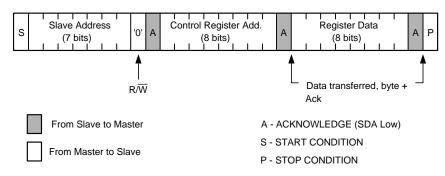

| SCL           | D4      | Serial Interface Clock Input. External pull-up resistor is needed, typical 1.5 k $\Omega$ .                                                                                                                                                                                                                 |  |

| SDA           | C4      | Serial Interface Data Input/Output. Open Drain output, external pull-up resistor is needed, typical 1.5 kΩ.                                                                                                                                                                                                 |  |

| SW1           | E5      | BUCK1 Switch node of DC-DC converter BUCK1.                                                                                                                                                                                                                                                                 |  |

| SW2           | B5      | BUCK2 Switch node of DC-DC converter BUCK2.                                                                                                                                                                                                                                                                 |  |

| VIN1          | F2      | Input for LDO1.                                                                                                                                                                                                                                                                                             |  |

| VINB1         | D5      | Input for BUCK1.                                                                                                                                                                                                                                                                                            |  |

| VIN2          | D1      | Input for LDO2 and LDO3.                                                                                                                                                                                                                                                                                    |  |

| VINB2         | C5      | Input for BUCK2.                                                                                                                                                                                                                                                                                            |  |

| VIN3          | A2      | Input for LDO4 and LDO5.                                                                                                                                                                                                                                                                                    |  |

| VINLILO1      | F4      | Input for LILO1.                                                                                                                                                                                                                                                                                            |  |

| VINLILO2      | A4      | Input for LILO2.                                                                                                                                                                                                                                                                                            |  |

**PIN DESCRIPTIONS**

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **DEVICE DESCRIPTION**

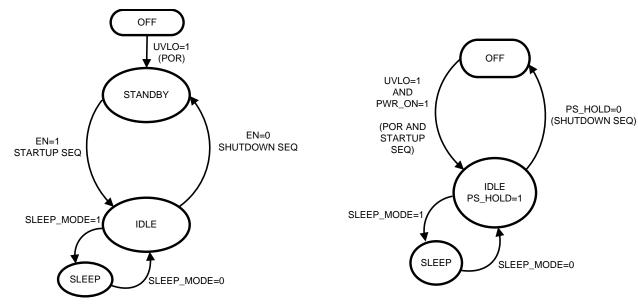

### **Operation Modes**

- **POWER-ON-RESET:** In SUB\_PMU configuration After VIN1 goes above UVLO high threshold, then all internal registers of LP8725 are reset to the default values from the DEFSEL setting, after which LP8725 goes to STANDBY mode. In PMU configuration When PWR\_ON goes high while VIN1 is above the UVLO high threshold, all internal registers of LP8725 are reset to the default values from the DEFSEL setting. This process duration max is typically 500 μs.

- **STANDBY:** In STANDBY mode only serial interface is working and all other PMU functions are disabled PMU is in low-power condition. In STANDBY mode LP8725 can be (re)configured via Serial Interface. The LP8725 only enters STANDBY mode automatically in SUB\_PMU configuration.

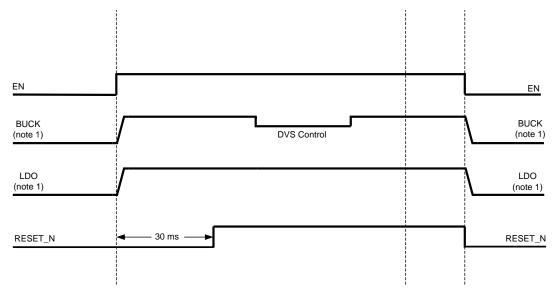

- STARTUP: STARTUP sequence is defined by registers contents. STARTUP sequence starts:

- 1) If rising edge on EN-pin in SUB\_PMU configuration.

2) After cooling down from thermal shutdown event if EN=1 in SUB\_PMU configuration.

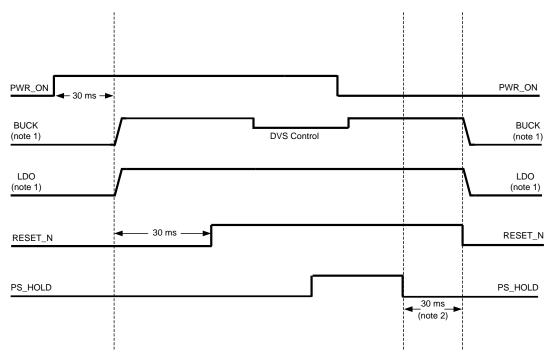

3) If PWR\_ON is still high after 30 ms (typical de-bounce time) in PMU configuration. It is not recommended to write to LP8725 registers during STARTUP. If doing so then current STARTUP sequence may become undefined.

In SUB\_PMU configuration RESET\_N is de-asserted 30 ms (typical) after EN=1. In PMU configuration RESET\_N is de-asserted a further 30 ms (typical) after PWR\_ON de-bounce time has ended. It is not recommended to write to LP8725 registers during startup. If doing so then current STARTUP sequence may become undefined.

- **IDLE:** The LP8725 will enter into IDLE mode (normal operating mode) after end of startup sequence. In IDLE mode all LDOs and BUCK can be enabled/disabled via Serial Interface. Also in IDLE mode the LP8725 can be (re)configured via Serial Interface.

- **SHUTDOWN:** SHUTDOWN sequence follows the reverse order of the startup sequence defined by registers contents:

1) If falling edge on EN-pin in SUB\_PMU configuration.

2) If PS\_HOLD and PWR\_ON both go low for typically 30 ms in PMU configuration. Device immediately shuts down if the temperature exceeds thermal shutdown threshold TSD +160°C.

RESET\_N is asserted when the device starts to shut down.

It is not recommended to write to LP8725 registers during SHUT DOWN. If doing so then current SHUTDOWN sequence may become undefined.

- In SUB\_PMU configuration the device shuts down to STANDBY mode.

- In PMU configuration the device shuts down completely (so registers will be reset on next PWR\_ON high).

- SLEEP: The load current for each of the LDO outputs should be no greater than 5mA when the device is put into SLEEP mode. In Sleep mode Ground current is minimized. SLEEP mode is controlled by the serial interface, Register 0x00 bit 1.

SLEEP Mode is controlled by the Serial Interface.

| CONFIG | Application | Pin B3 Function | Pin E3 Function | Slave Address,<br>DEFSEL = 1 | Slave Address,<br>DEFSEL = 0 |

|--------|-------------|-----------------|-----------------|------------------------------|------------------------------|

| GND    | SUB_PMU     | B2_EN           | EN              | 7h'78                        | 7h'7A                        |

| VIN1   | PMU         | PS_HOLD         | PWR_ON          | 7h'79                        | 7h'7B                        |

#### Table 1. Application Configuration<sup>(1)(2)</sup>

(1) The LP8725 and LP8725-A are both configured as either SUB\_PMU or PMU by the wiring of the CONFIG pin on the application of power to the device.

(2) These are dependent on whether DEFSEL is connected to VIN1 or GND when PWR\_ON/EN=1.

SNVS618G - DECEMBER 2009-REVISED MAY 2013

Figure 2. PMU Mode, CONFIG = 1

### **Additional Functions**

- **DVS:** Dynamic Voltage Scaling allows using 2 set voltages for BUCKs. This is controlled via Serial Interface. BUCK1 can also be controlled by the external DVS pin.

- **FAULT DETECTION** If BUCK1/BUCK2 and LDO1 are not masked then if one of the outputs is pulled down e.g., short circuit, then RESET\_N is asserted (low)..

| Part No. | DEFSEL         | Start-Up Sequence                                                                     | Shut Down Sequence                     |

|----------|----------------|---------------------------------------------------------------------------------------|----------------------------------------|

| LP8725   | VIN1 (setup 1) | BUCK1 then BUCK2 and LILO2 then LDO1, LDO2, LDO4 and LDO5 then LDO3 and LILO1         | In reverse order of start-up sequence. |

| LP8725   | GND (setup 2)  | BUCK1 and LILO2 then BUCK2, LDO1, LDO2, LDO5 and LILO1 then LDO3 and LDO4.            | In reverse order of start-up sequence. |

| LP8725-A | VIN1 (setup 1) | LDO1, LDO2, LDO5 and LILO1 then LDO4 and LILO2                                        | In reverse order of start-up sequence. |

| LP8725-A | GND (setup 2)  | BUCK1 and BUCK2 then LDO2 and LDO3 then LDO1, LDO4 and LDO5 then LILO1 and LILO2      | In reverse order of start-up sequence. |

| LP8725-B | VIN1 or GND    | BUCK1 then BUCK2 then LDO1 then LILO2                                                 | In reverse order of start-up sequence. |

| LP8725-C | VIN1 or GND    | BUCK1 then BUCK2 and LDO5 then LDO1 and LDO2 and LILO 1 and LILO 2 then LDO3 and LDO4 | In reverse order of start-up sequence. |

| LP8725-D | VIN1 or GND    | BUCK1 then BUCK2, LDO3, LILO1 and LILO2                                               | In reverse order of start-up sequence. |

(1) These are dependent on whether DEFSEL is connected to VIN1 or GND when PWR\_ON/EN=1.

TEXAS INSTRUMENTS

SNVS618G-DECEMBER 2009-REVISED MAY 2013

www.ti.com

Figure 3. Simplified startup Sequence if CONFIG=GND (SUB\_PMU)

All timing is typical.

Note 1 See detailed on/off sequence diagrams for the different DEFSEL options.

**Note 2** PS\_HOLD needs to be held low for >30 ms before RESET\_N is asserted low. PMU should then start shutdown sequence opposite of startup sequence.

### Figure 4. Simplified Startup Sequence if CONFIG=VIN1 (PMU)

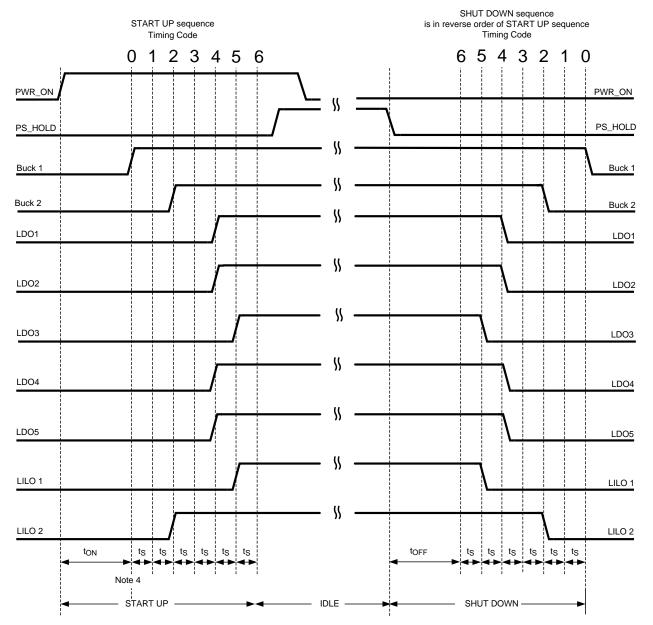

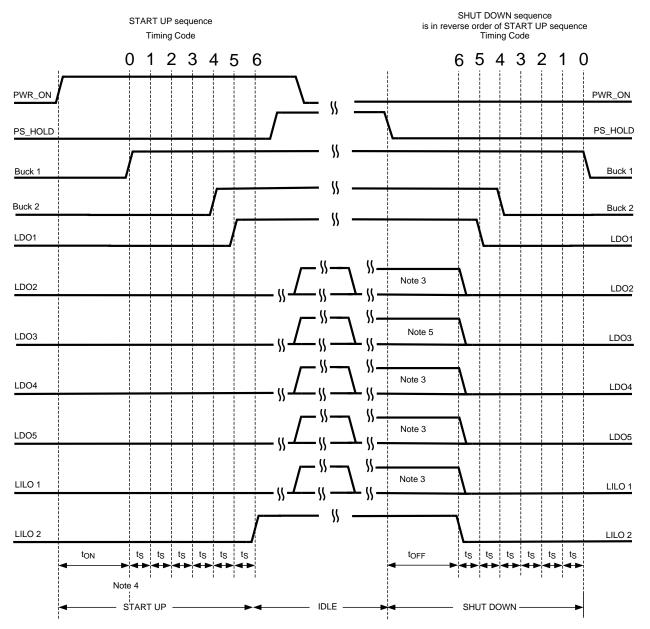

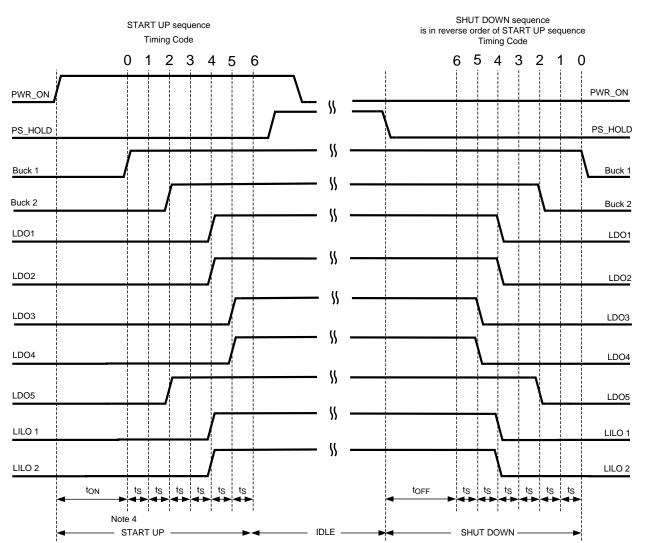

# Figure 5. LP8725 Startup and Shutdown Sequence if CONFIG=VIN1 Note 1, Note 2

All timing is typical.

ton/OFF 30 ms typ. de-bounce times

t<sub>S</sub> Programmable time steps. (**Typically 64 μs/step.**) Time step accuracy is defined by OSC frequency accuracy. **Note 1** STARTUP and SHUTDOWN sequences are defined by registers. Sequences given here are valid if there the registers are not rewritten via Serial Interface.

**Note 2** The timing showed here define time points when LDOs and BUCK are enabled/disabled. Enabling /disabling process duration depends on voltages and loading conditions. Buck startup duration is typically 170 µs. LDO startup duration is typically 35 µs. For details please see LDOs and BUCK Electrical Specifications. **Note 4** At this time point registers are reset to POR default values.

SNVS618G-DECEMBER 2009-REVISED MAY 2013

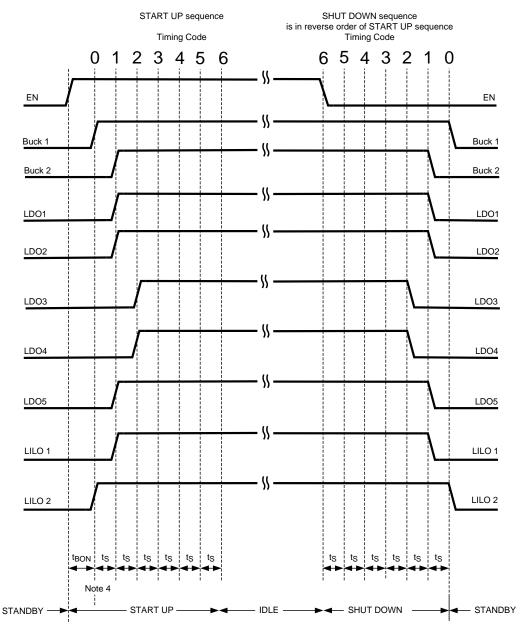

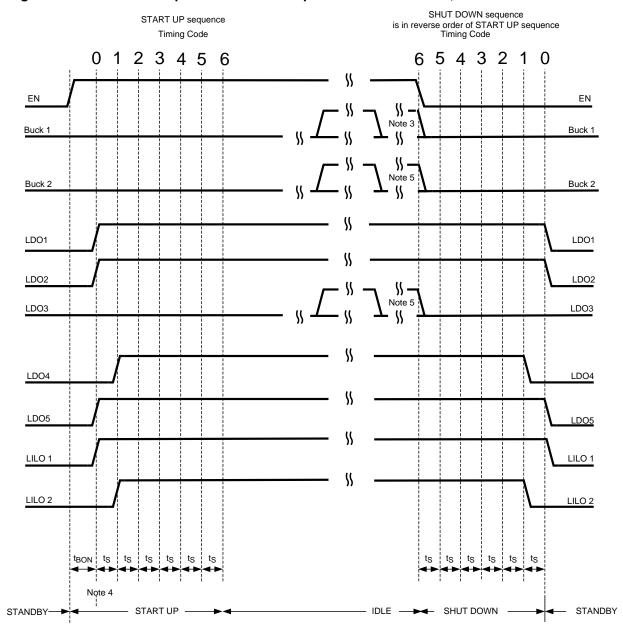

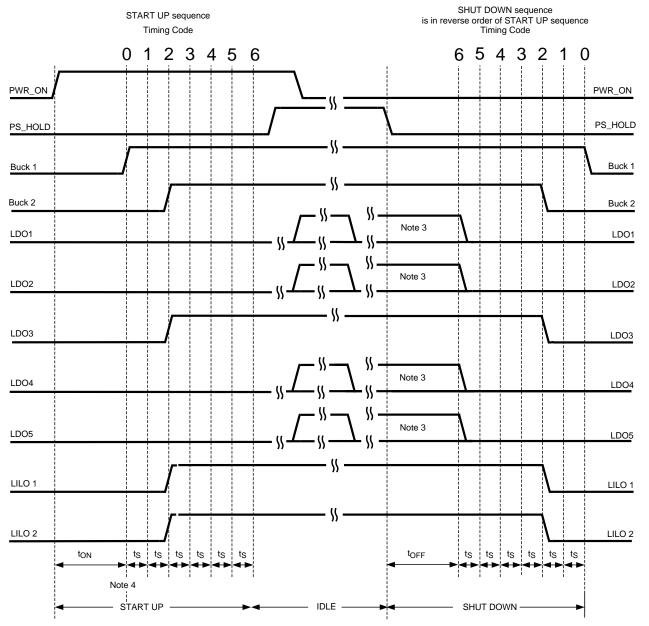

# Figure 6. LP8725 Startup and Shutdown Sequence if CONFIG=GND, DEFSEL=GND Note 1, Note 2

All timing is typical.

$t_{\text{BON}}$  75  $\mu \text{s}$  - Reference and bias turn ON.

t<sub>s</sub> Programmable time steps. **(Typically 64 μs/step.)** Time step accuracy is defined by OSC frequency accuracy. **Note 1** STARTUP and SHUTDOWN sequences are defined by registers. Sequences given here are valid if there the registers are not rewritten via Serial Interface.

**Note 2** The timing showed here define time points when LDOs and BUCK are enabled/disabled. Enabling /disabling process duration depends on voltages and loading conditions. Buck startup duration is typically 170 µs. LDO startup duration is typically 35 µs. For details please see LDOs and BUCK Electrical Specifications. **Note 4** At this time point registers are reset to POR default values.

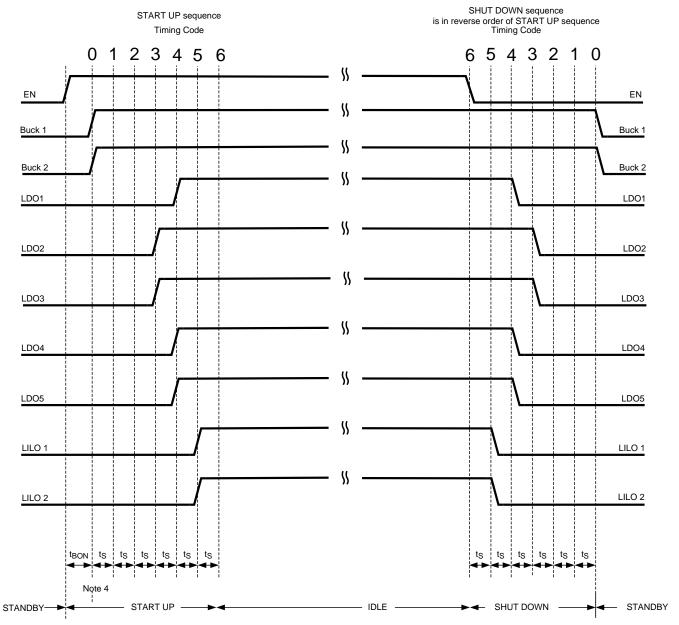

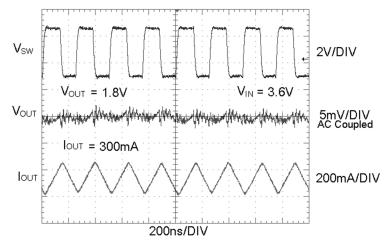

### Figure 7. LP8725-A Startup and Shutdown Sequence if CONFIG=GND, DEFSEL=VIN1 Note 1, Note 2

All timing is typical.

$t_{BON}$  75  $\mu s$  - Reference and bias turn ON.

t<sub>S</sub> Programmable time steps. **(Typically 64 μs/step.)** Time step accuracy is defined by OSC frequency accuracy. **Note 1** STARTUP and SHUTDOWN sequences are defined by registers. Sequences given here are valid if there the registers are not rewritten via Serial Interface.

**Note 2** The timing showed here define time points when LDOs and BUCK are enabled/disabled. Enabling /disabling process duration depends on voltages and loading conditions. Buck startup duration is typically 170 µs. LDO startup duration is typically 35 µs. For details please see LDOs and BUCK Electrical Specifications.

**Note 3** BUCK1 is disabled. If it is enabled via Serial Interface and the startup sequence is not changed, then it will be disabled, with no delay, from falling edge of EN-pin.

**Note 4** At this time point registers are reset to POR default values.

**Note 5** BUCK2 and LDO3 are enabled by B2\_EN and LDO3\_EN respectively (or via serial interface). If these inputs are high when EN goes high then these outputs turn on after  $t_s$ = 6.

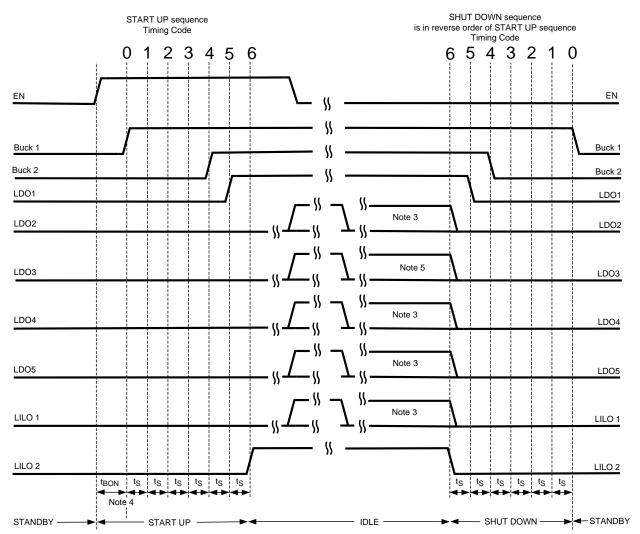

# Figure 8. LP8725-A Startup and Shutdown Sequence if CONFIG=GND, DEFSEL=GND Note 1, Note 2

All timing is typical.

$t_{\text{BON}}$  75  $\mu s$  - Reference and bias turn ON.

t<sub>S</sub> Programmable time steps. **(Typically 64 μs/step.)** Time step accuracy is defined by OSC frequency accuracy. **Note 1** STARTUP and SHUTDOWN sequences are defined by registers. Sequences given here are valid if there the registers are not rewritten via Serial Interface.

**Note 2** The timing showed here define time points when LDOs and BUCK are enabled/disabled. Enabling /disabling process duration depends on voltages and loading conditions. Buck startup duration is typically 170 µs. LDO startup duration is typically 35 µs. For details please see LDOs and BUCK Electrical Specifications. **Note 4** At this time point registers are reset to POR default values.

#### Figure 9. LP8725-B Startup and Shutdown Sequence if CONFIG=VIN1, DEFSEL=VIN1 or DEFSEL=GND Note 1, Note 2

All timing is typical.

ton/off 30 ms typ. de-bounce times.

t<sub>S</sub> Programmable time steps. **(Typically 64 μs/step.)** Time step accuracy is defined by OSC frequency accuracy. **Note 1** STARTUP and SHUTDOWN sequences are defined by registers. Sequences given here are valid if there the registers are not rewritten via Serial Interface.

**Note 2** The timing showed here define time points when LDOs and BUCK are enabled/disabled. Enabling /disabling process duration depends on voltages and loading conditions. Buck startup duration is typically 170 µs. LDO startup duration is typically 35 µs. For details please see LDOs and BUCK Electrical Specifications.

**Note 3** LDO2, 4, 5 and LILO1 are disabled. If they are enabled via Serial Interface and the startup sequence is not changed, then they will be disabled, with no delay, from falling edge of EN-pin.

Note 4 At this time point registers are reset to POR default values.

Note 5 LDO3 is enabled by LDO3\_EN (or via serial interface). If this input is high when PWR\_ON goes high then this output turns on after  $t_s$ = 6.

SNVS618G-DECEMBER 2009-REVISED MAY 2013

All timing is typical.

tBON 75 µs - Reference and bias turn ON.

t<sub>S</sub> Programmable time steps. (Typically 64 μs/step.) Time step accuracy is defined by OSC frequency accuracy. Note 1 STARTUP and SHUT DOWN sequences are defined by registers. Sequences given here are valid if there the registers are not rewritten via Serial Interface.

**Note 2** The timing showed here define time points when LDOs and BUCK are enabled/disabled. Enabling /disabling process duration depends on voltages and loading conditions. Buck startup duration is typically 170 µs. LDO startup duration is typically 35 µs. For details please see LDOs and BUCK Electrical Specifications.

**Note 3** LDO2, 4, 5 and LILO1 are disabled. If they are enabled via Serial Interface and the startup sequence is not changed, then they will be disabled, with no delay, from falling edge of EN-pin.

Note 4 At this time point registers are reset to POR default values.

Note 5 LDO3 is enabled by LDO3\_EN (or via serial interface). If this input is high when PWR\_ON goes high then this output turns on after  $t_s$ = 6.

SNVS618G - DECEMBER 2009 - REVISED MAY 2013

#### Figure 11. LP8725-C Startup and Shutdown Sequence if CONFIG=VIN1, DEFSEL=VIN1 or DEFSEL=GND Note 1, Note 2

All timing is typical.

ton/off 30 ms typ. de-bounce times.

t<sub>S</sub> Programmable time steps. (**Typically 64 μs/step.)** Time step accuracy is defined by OSC frequency accuracy. **Note 1** STARTUP and SHUTDOWN sequences are defined by registers. Sequences given here are valid if there the registers are not rewritten via Serial Interface.

**Note 2** The timing showed here define time points when LDOs and BUCK are enabled/disabled. Enabling /disabling process duration depends on voltages and loading conditions. Buck startup duration is typically 170 µs. LDO startup duration is typically 35 µs. For details please see LDOs and BUCK Electrical Specifications.

Note 4 At this time point registers are reset to POR default values.

SNVS618G - DECEMBER 2009 - REVISED MAY 2013

All timing is typical.

ton/OFF 30 ms typ. de-bounce times.

t<sub>S</sub> Programmable time steps. (**Typically 64 μs/step.**) Time step accuracy is defined by OSC frequency accuracy. **Note 1** STARTUP and SHUTDOWN sequences are defined by registers. Sequences given here are valid if there the registers are not rewritten via Serial Interface.

**Note 2** The timing showed here define time points when LDOs and BUCK are enabled/disabled. Enabling /disabling process duration depends on voltages and loading conditions. Buck startup duration is typically 170 µs. LDO startup duration is typically 35 µs. For details please see LDOs and BUCK Electrical Specifications.

**Note 3** LDO1, 2, 4, 5 are disabled. If they are enabled via Serial Interface and the startup sequence is not changed, then they will be disabled, with no delay, from falling edge of EN-pin.

**Note 4** At this time point registers are reset to POR default values.

**Note 5** LDO3 is enabled by LDO3\_EN (or via serial interface). If this input is high when PWR\_ON goes high then this output turns on after  $t_s$ = 6.

#### SNVS618G - DECEMBER 2009-REVISED MAY 2013

www.ti.com

|        | Table 3. Default Output Voltages <sup>(1)(2)</sup> |                   |                                                                |               |  |

|--------|----------------------------------------------------|-------------------|----------------------------------------------------------------|---------------|--|

| Output | Max Current (mA)                                   | Voltage Range (V) | Default output Voltage [V] and default ON/OFF<br>(PWR_ON/EN=1) |               |  |

|        |                                                    |                   | DEFSEL = VIN1                                                  | DEFSEL = GND  |  |

| BUCK1  | 800                                                | 0.8 to 3.0        | 1.0*/1.2** ON                                                  | 1.2*/1.0** ON |  |

| BUCK2  | 600                                                | 0.8 to 3.0        | 1.8*/1.8** ON                                                  | 1.8*/1.8** ON |  |

| LDO1   | 300                                                | 1.2 to 3.3        | 2.8 ON                                                         | 2.6 ON        |  |

| LDO2   | 300                                                | 1.2 to 3.3        | 1.8 ON                                                         | 2.8 ON        |  |

| LDO3   | 300                                                | 1.2 to 3.3        | 3.3 ON                                                         | 2.8 ON        |  |

| LDO4   | 300                                                | 1.2 to 3.3        | 3.3 ON                                                         | 2.8 ON        |  |

| LDO5   | 300                                                | 1.2 to 3.3        | 2.8 ON                                                         | 2.8 ON        |  |

| LILO1  | 300                                                | 0.8 to 3.3        | 1.2 ON                                                         | 3.3 ON        |  |

| LILO2  | 300                                                | 0.8 to 3.3        | 1.2 ON                                                         | 1.2 ON        |  |

These are dependent on whether DEFSEL is connected to VIN1 or GND when PWR\_ON/EN=1. (1)

(2) BUCK1 voltages are set to \*BUCK1\_V1 and \*\*BUCK1\_V2 as selected by DVS1\_V and the DVS pin.

BUCK2 voltages are set to \*BUCK2\_V1 and \*\*BUCK2\_V2 as selected by DVS2\_V.

### Table 4. LP8725-A Alternative Part's Default Output Voltages<sup>(1)(2)</sup>

| Output | Max Current (mA) | Voltage Range (V) | Default output Voltage [V] and default ON/OFF<br>(PWR_ON/EN=1) |               |

|--------|------------------|-------------------|----------------------------------------------------------------|---------------|

|        |                  |                   | DEFSEL = VIN1                                                  | DEFSEL = GND  |

| BUCK1  | 800              | 0.8 to 3.0        | 1.1*/1.0** OFF                                                 | 1.3*/1.2** ON |

| BUCK2  | 600              | 0.8 to 3.0        | 1.1*/1.0** OFF***                                              | 1.3*/1.2** ON |

| LDO1   | 300              | 1.2 to 3.3        | 2.6 ON                                                         | 2.8 ON        |

| LDO2   | 300              | 1.2 to 3.3        | 3.0 ON                                                         | 2.8 ON        |

| LDO3   | 300              | 1.2 to 3.3        | 3.3 OFF****                                                    | 2.8 ON        |

| LDO4   | 300              | 1.2 to 3.3        | 3.0 ON                                                         | 2.8 ON        |

| LDO5   | 300              | 1.2 to 3.3        | 2.8 ON                                                         | 2.8 ON        |

| LILO1  | 300              | 0.8 to 3.3        | 1.8 ON                                                         | 1.8 ON        |

| LILO2  | 300              | 0.8 to 3.3        | 1.0 ON                                                         | 1.8 ON        |

These are dependent on whether DEFSEL is connected to VIN1 or GND when PWR\_ON/EN=1.

BUCK1 voltages are set to \*BUCK1\_V1 and \*\*BUCK1\_V2 as selected by DVS1\_V and the DVS pin. BUCK2 voltages are set to \*BUCK2\_V1 and \*\*BUCK2\_V2 as selected by DVS2\_V.

\*\*\* Only if pin B2\_EN=0 if in SUB\_PMU configuration

\*\*\*\* Only if pin LDO3\_EN=0

#### SNVS618G - DECEMBER 2009 - REVISED MAY 2013

www.ti.com

## Table 5. LP8725-B Alternative Part's Default Output Voltages<sup>(1)(2)</sup>

| Output | Max Current (mA) | Voltage Range (V) | Default output Voltage [V] and default ON/OFF<br>(PWR_ON/EN=1) |               |

|--------|------------------|-------------------|----------------------------------------------------------------|---------------|

|        |                  |                   | DEFSEL = VIN1                                                  | DEFSEL = GND  |

| BUCK1  | 800              | 0.8 to 3.0        | 1.2*/1.2** ON                                                  | 1.2*/1.2** ON |

| BUCK2  | 600              | 0.8 to 3.0        | 1.8*/1.8** ON                                                  | 1.8*/1.8** ON |

| LDO1   | 300              | 1.2 to 3.3        | 2.6 ON                                                         | 1.8 ON        |

| LDO2   | 300              | 1.2 to 3.3        | 2.8 OFF                                                        | 2.8 OFF       |

| LDO3   | 300              | 1.2 to 3.3        | 2.8 OFF***                                                     | 2.8 OFF***    |

| LDO4   | 300              | 1.2 to 3.3        | 1.2 OFF                                                        | 1.2 OFF       |

| LDO5   | 300              | 1.2 to 3.3        | 1.2 OFF                                                        | 1.2 OFF       |

| LILO1  | 300              | 0.8 to 3.3        | 2.5 OFF                                                        | 2.5 OFF       |

| LILO2  | 300              | 0.8 to 3.3        | 3.3 ON                                                         | 3.3 ON        |

(1) These are dependent on whether DEFSEL is connected to VIN1 or GND when PWR\_ON/EN=1.

(2) BUCK1 voltages are set to \*BUCK1\_V1 and \*\*BUCK1\_V2 as selected by DVS1\_V and the DVS pin.

BUCK2 voltages are set to \*BUCK2\_V1 and \*\*BUCK2\_V2 as selected by DVS2\_V.

\*\*\* Only if pin LDO3\_EN=0

| Table 6. LP8725-C Alternative Part's Default Output Voltages <sup>(1)</sup> |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

| Output | Max Current (mA) | Voltage Range (V) | Default output Voltage [V] and default ON/OFF<br>(PWR_ON/EN=1) |              |

|--------|------------------|-------------------|----------------------------------------------------------------|--------------|

|        |                  |                   | DEFSEL = VIN1                                                  | DEFSEL = GND |

| BUCK1  | 800              | 0.8 to 3.0        | 1.2 ON                                                         | 1.2 ON       |

| BUCK2  | 600              | 0.8 to 3.0        | 1.8 ON                                                         | 1.8 ON       |

| LDO1   | 300              | 1.2 to 3.3        | 2.6 ON                                                         | 2.6 ON       |

| LDO2   | 300              | 1.2 to 3.3        | 2.8 ON                                                         | 2.8 ON       |

| LDO3   | 300              | 1.2 to 3.3        | 2.8 ON                                                         | 2.8 ON       |

| LDO4   | 300              | 1.2 to 3.3        | 2.5 ON                                                         | 2.5 ON       |

| LDO5   | 300              | 1.2 to 3.3        | 3.3 ON                                                         | 3.3 ON       |

| LILO1  | 300              | 0.8 to 3.3        | 1.2 ON                                                         | 1.2 ON       |

| LILO2  | 300              | 0.8 to 3.3        | 1.2 ON                                                         | 1.2 ON       |

(1) These are dependent on whether DEFSEL is connected to VIN1 or GND when PWR\_ON/EN=1.

SNVS618G - DECEMBER 2009 - REVISED MAY 2013

www.ti.com

### Table 7. LP8725-D Alternative Part's Default Output Voltages<sup>(1)(2)</sup>

| Output | Max Current (mA) | Voltage Range (V) | Default output Voltage [V] and default ON/OFF<br>(PWR_ON/EN=1) |               |

|--------|------------------|-------------------|----------------------------------------------------------------|---------------|

|        |                  |                   | DEFSEL = VIN1                                                  | DEFSEL = GND  |

| BUCK1  | 800              | 0.8 to 3.0        | 1.3*/1.3** ON                                                  | 1.3*/1.3** ON |

| BUCK2  | 800              | 0.8 to 3.0        | 1.8*/1.8** ON                                                  | 1.8*/1.8** ON |

| LDO1   | 300              | 1.2 to 3.3        | 2.8 OFF                                                        | 2.8 OFF       |

| LDO2   | 300              | 1.2 to 3.3        | 1.8 OFF                                                        | 1.8 OFF       |

| LDO3   | 300              | 1.2 to 3.3        | 1.8 ON                                                         | 1.8 ON        |

| LDO4   | 300              | 1.2 to 3.3        | 3.0 OFF                                                        | 3.0 OFF       |

| LDO5   | 300              | 1.2 to 3.3        | 1.8 OFF                                                        | 1.2 OFF       |

| LILO1  | 300              | 0.8 to 3.3        | 3.0 ON                                                         | 3.0 ON        |

| LILO2  | 300              | 0.8 to 3.3        | 3.0 ON                                                         | 3.0 ON        |

These are dependent on whether DEFSEL is connected to VIN1 or GND when PWR\_ON/EN=1. (1)

BUCK1 voltages are set to \*BUCK1\_V1 and \*\*BUCK1\_V2 as selected by DVS1\_V and the DVS pin. BUCK2 voltages are set to \*BUCK2\_V1 and \*\*BUCK2\_V2 as selected by DVS2\_V. (2)

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup> <sup>(2)</sup>

| V <sub>IN1</sub>                             |                              | -0.3V to +6V                 |

|----------------------------------------------|------------------------------|------------------------------|

| VIN2, VIN3, VINLILO1, VINLILO2, VINB1, VINB2 | -0.3V to VIN1+0.3V and <6.0V |                              |

| Logic and control pins: Voltage to GND       |                              | -0.3V to VIN1+0.3V and <6.0V |

| Continuous Power Dissipation <sup>(3)</sup>  | Internally Limited           |                              |

| Junction Temperature (T <sub>J-MAX</sub> )   | 150°C                        |                              |

| Storage Temperature Range                    |                              | -65 to 150°C                 |

| ESD Rating <sup>(4)</sup>                    | Human Body Model             | 2kV                          |

|                                              | Machine Model                | 200V                         |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND pin.

(3) Internal thermal shutdown circuitry protects the device fro permanent damage. Thermal shutdown engages at  $T_J = 150^{\circ}C$  (typ.) and disengages at  $T_J = 130^{\circ}C$ .

(4) The human-body model is 100 pF discharged through 1.5 kΩ. The machine model is a 200 pF capacitor discharged directly into each pin, MIL-STD-883 3015.7.

### OPERATING RATINGS (1) (2)

| V <sub>IN1</sub>                                                            | 2.6 to 4.5V  |

|-----------------------------------------------------------------------------|--------------|

| V <sub>IN2</sub> , V <sub>IN3</sub> , V <sub>INB1</sub> , V <sub>INB2</sub> | 2.6V to VIN1 |

| V <sub>INLILO1</sub> , V <sub>INLILO2</sub>                                 | 1.8V to VIN1 |

| All input-only pins                                                         | 0V to VIN1   |

| Junction Temperature (T <sub>J</sub> )                                      | -40 to 125°C |

| Ambient Temperature (T <sub>A</sub> ) <sup>(3)</sup>                        | -40 to 85°C  |

| Maximum Power Dissipation ( $T_A = 70^{\circ}C$ )                           | 1.3 W        |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND pin.

(3) In applications where high power dissipation and/or poor package resistance is present, the maximum ambient temperature may have to be de-rated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX</sub>), The maximum power dissipation of the device in the application (P<sub>D-MAX</sub>) and the junction to ambient thermal resistance of the package (θ<sub>JA</sub>) in the application, as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX</sub> (θ<sub>JA</sub> x P<sub>D-MAX</sub>). Due to the pulsed nature of testing the part, the temp in the Electrical Characteristic table is specified as T<sub>A</sub> = T<sub>J</sub>.

### **THERMAL PROPERTIES**

| Junction-to-Ambient Thermal Resistance $(\theta_{JA})^{(1)}$ , $\theta_{JA}$ 4–Layer JEDEC Board <sup>(2)</sup> | 41°C/W |

|-----------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                                 |        |

(1) In applications where high power dissipation and/or poor package resistance is present, the maximum ambient temperature may have to be de-rated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX</sub>). The maximum power dissipation of the device in the application (P<sub>D-MAX</sub>) and the junction to ambient thermal resistance of the package (θ<sub>JA</sub>) in the application, as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX</sub> (θ<sub>JA</sub> x P<sub>D-MAX</sub>). Due to the pulsed nature of testing the part, the temp in the Electrical Characteristic table is specified as T<sub>A</sub> = T<sub>J</sub>.

(2) Junction-to-ambient thermal resistance is highly application and board layout dependent. In applications where high power dissipation exists, special care must be given to thermal dissipation issues in board design.

### **CURRENT CONSUMPTION**

Unless otherwise noted,  $V_{IN1}=V_{IN2}=V_{IN3}=V_{INB1}=V_{INB2}=V_{INLILO1}=V_{INLILO2}=3.6V$ ;  $C_{LDOX}=1\mu$ F;  $C_{BUCKOUT}=C_{BUCKIN}=4.7 \mu$ F;  $C_{VIN1-3}=C_{VINLILO1}=C_{VINLILO2}=2.2 \mu$ F. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J=-40$  to  $+125^{\circ}$ C. <sup>(1)</sup>

| Symbol     | Parameter                        | Conditions                             | Min | Тур | Max | Unit |

|------------|----------------------------------|----------------------------------------|-----|-----|-----|------|

| Q(STANDBY) | Standby Current                  | All outputs disabled EN = 0            |     | 3.3 | 8   |      |

| Q(SLEEP)   | Current in SLEEP Mode at no load | Outputs disabled via control registers |     | 50  | 80  |      |

|            |                                  | Only Buck1 and LDO1 enabled            |     | 95  |     |      |

|            |                                  | All outputs enabled                    |     | 205 | 280 | μA   |

| Q(IDLE)    | Current at no load               | Outputs disabled via control registers |     | 145 | 210 |      |

|            |                                  | Only Buck1 and LDO1 enabled            |     | 205 |     |      |

|            |                                  | All outputs enabled                    |     | 420 | 600 |      |

(1) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not verified, but do represent the most likely norm.

### THERMAL SHUTDOWN

The Thermal Shutdown (TSD) function monitors the chip temperature  $(T_J)$  to protect the chip from temperature damage caused, e.g., by excessive power dissipation. <sup>(1)</sup>

| Symbol | Parameter      | Conditions | Min | Тур | Max | Unit |

|--------|----------------|------------|-----|-----|-----|------|

|        | TSD            |            |     | 160 |     | °C   |

|        | TSD Hysteresis |            |     | 20  |     | °C   |

(1) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not verified, but do represent the most likely norm.

### UNDER-VOLTAGE LOCK OUT

This device has Under-Voltage Lock Out (UVLO) that checks VIN1-pin voltage before starting Power On sequence. UVLO is also checked during Power On sequence. If the VDD voltage is less than UVLO threshold the PMU will not Power On. After the PMU successfully passed Power On sequence UVLO is not monitored. <sup>(1)</sup>

| Symbol            | Parameter                                 | Conditions | Min   | Тур | Мах   | Unit |

|-------------------|-------------------------------------------|------------|-------|-----|-------|------|

|                   | UVLO Threshold<br>V <sub>IN1</sub> rising | CONFIG = 0 |       | 2.3 |       | V    |

| N                 |                                           | CONFIG = 1 | 2.825 | 3.0 | 3.185 | v    |

| V <sub>UVLO</sub> | Hysteresis                                | CONFIG = 0 |       | 400 |       |      |

|                   |                                           | CONFIG = 1 |       | 800 |       | mV   |

(1) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not verified, but do represent the most likely norm.

### LOGIC AND CONTROL

Unless otherwise noted,  $V_{IN1}=V_{IN2}=V_{IN3}=V_{INB1} = V_{INB2}=V_{INLILO1}=V_{INLILO2}=3.6V$ ;  $C_{LODX}=1\mu$ F;  $C_{BUCKOUT}=C_{BUCKIN}=4.7 \mu$ F,  $C_{VIN1-3}=C_{VINLILO1}C_{VINLILO2}=2.2 \mu$ F. Typical values and limits appearing in normal type apply for  $T_{J}=25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_{J}=-40$  to  $+125^{\circ}$ C. <sup>(1)</sup>

| Symbol           | Parameter                | Conditions                                                                                       | Min | Тур | Max | Unit |  |  |  |  |  |

|------------------|--------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|--|--|

| Logic and Contro | Logic and Control Inputs |                                                                                                  |     |     |     |      |  |  |  |  |  |

| V <sub>IL</sub>  | Input Low Level          | EN, SCL, SDA, DVS, PS_HOLD,<br>PWR_ON BUCK2_EN, LDO3_EN                                          |     |     | 0.4 | V    |  |  |  |  |  |

| V <sub>IH</sub>  | Input High Level         | EN, SCL, SDA, DVS, PS_HOLD<br>PWR_ON, BUCK2_EN, LDO3_EN                                          | 1.2 |     |     | V    |  |  |  |  |  |

| I <sub>IL</sub>  | Input Low Level Current  | EN, SCL, SDA, DVS, PS_HOLD<br>PWR_ON, DVS, DEFSEL, CONFIG,<br>BUCK2_EN, LDO3_EN<br>$V_{IL} = 0V$ |     | 0   | 2   | μA   |  |  |  |  |  |

(1) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not verified, but do represent the most likely norm.

# LOGIC AND CONTROL (continued)

Unless otherwise noted,  $V_{IN1}=V_{IN2}=V_{IN3}=V_{INB1}=V_{INB2}=V_{INLILO1}=V_{INLILO2}=3.6V$ ;  $C_{LODX}=1\mu$ F;  $C_{BUCKOUT}=C_{BUCKIN}=4.7 \mu$ F,  $C_{VIN1-3}=C_{VINLILO1}C_{VINLILO2}=2.2 \mu$ F. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J=-40$  to  $+125^{\circ}$ C. <sup>(1)</sup>

| Symbol          | Parameter                | Conditions                                              | Min                    | Тур                           | Max | Unit |

|-----------------|--------------------------|---------------------------------------------------------|------------------------|-------------------------------|-----|------|

| I <sub>IH</sub> | Input High Level Current | PS_HOLD, DEFSEL, CONFIG, DVS $V_{IH} = V_{IN1}$         |                        | 0                             | 2   |      |

| R <sub>PD</sub> | Pull Down Resistance     | From EN, PWR_ON, B2_EN, and LDO3_EN                     | PWR_ON, B2_EN, and 500 |                               | kΩ  |      |

| Logic and Cont  | rol Outputs              |                                                         |                        |                               |     |      |

| V <sub>OL</sub> | Output Low Level         | SDA, RESET_N<br>I <sub>OUT</sub> = 2mA                  |                        | 0.14                          | 0.3 | V    |

| I <sub>OH</sub> | Output High Level        | SDA, RESET_N have Open drain outputs $V_{OH} = V_{IN1}$ |                        | 0.14 <b>0.3</b><br>0 <b>2</b> |     | μΑ   |

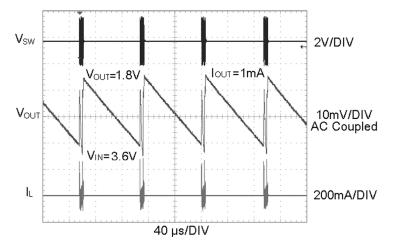

### **BUCK CONVERTERS**

Unless otherwise noted,  $V_{IN1}=V_{IN2}=V_{IN3}=V_{INB1} = V_{INB2}=V_{INLILO1}=V_{INLILO2}=3.6V$ ;  $C_{LODX}=1\mu$ F;  $C_{BUCKOUT}=C_{BUCKIN}=4.7 \mu$ F,  $C_{VIN1-3}=C_{VINLILO1}C_{VINLILO2}=2.2 \mu$ F. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J=-40$  to  $+125^{\circ}$ C. <sup>(1)</sup> <sup>(2)</sup>

| Symbol               | Parameter                   | Conditions                                                         | Min | Тур  | Max  | Unit |

|----------------------|-----------------------------|--------------------------------------------------------------------|-----|------|------|------|

|                      | BUCK1 Feedback Voltage      | N/ 4 0V/                                                           | -2  |      | +2   | 0/   |

| V <sub>FB</sub>      | BUCK2 Feedback Voltage      | V <sub>OUT</sub> = 1.8V                                            | -3  |      | +3   | %    |

| R <sub>DSON(P)</sub> | Pin-Pin resistance for PFET | I <sub>OUT</sub> = 200 mA                                          |     | 265  |      | mΩ   |

| R <sub>DSON(N)</sub> | Pin-Pin resistance for NFET | I <sub>OUT</sub> = −200 mA                                         |     | 150  |      | mΩ   |

|                      | Switch Peak Current Limit   | Open-loop, programmable:                                           |     | 460  |      |      |

| 1                    |                             | 250 mA max I <sub>OUT</sub> typ<br>450 mA max I <sub>OUT</sub> typ |     | 780  | 780  | 1.   |

| LIM                  | Switch Feak Current Linit   | 600 mA max l <sub>OUT</sub> typ                                    | 750 | 1050 | 1500 | mA   |

|                      |                             | 800 mA max I <sub>OUT</sub> typ                                    |     | 1370 |      | -    |

| t <sub>STUP</sub>    | Startup Time                | $I_{OUT} = 0$ mA to 100 mA                                         |     | 170  |      | μs   |

| f <sub>SW</sub>      | Switching Frequency         |                                                                    | 3.6 | 4.1  | 4.4  | MHz  |

(1) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not verified, but do represent the most likely norm.

(2) The parameters in the electrical characteristic table are tested under open loop conditions at  $V_{IN} = 3.6V$  unless otherwise specified. For performance over the input voltage range and closed loop condition, refer to the datasheet curves.

# DIGITAL LDOs (1, 2, 3)

Unless otherwise noted,  $V_{IN1}=V_{IN2}=V_{IN3}=V_{INB1}=V_{INB2}=V_{INLILO1}=V_{INLILO2}=3.6V$ ;  $C_{LODX}=1\mu$ F;  $C_{BUCKOUT}=C_{BUCKIN}=4.7 \mu$ F,  $C_{VIN1-3}=C_{VINLILO1}C_{VINLILO2}=2.2 \mu$ F. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J=-40$  to  $+125^{\circ}$ C. <sup>(1)</sup>

| Symbol                                             | Parameter                             | Conditions                                                                  | Min  | Тур | Max  | Unit |

|----------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------|------|-----|------|------|

|                                                    | LDO1 Output Voltage                   |                                                                             | -1.5 |     | +1.5 |      |

| $V_{OUT}$ Accuracy $I_{OUT} = 1mA, V_{OUT} = 2.8V$ | -2                                    |                                                                             | +2   | %   |      |      |

| VOUT                                               | LDOs 2 & 3 Output Voltage<br>Accuracy | $I_{OUT} = 1 \text{ImA}, V_{OUT} = 2.8 \text{V}$                            | -2   |     | +2   | 70   |

|                                                    |                                       |                                                                             | -2.5 |     | +2.5 |      |

| ΔV <sub>OUT</sub>                                  | Line Regulation                       | $V_{OUT}$ + 0.5V $\leq V_{IN2} \leq 4.5V$<br>$I_{OUT}$ = 1mA <sup>(2)</sup> |      | 2   |      | mV   |

|                                                    | Load Regulation                       | 1 < I <sub>OUT</sub> < 300 mA                                               |      | 2   |      |      |

(2) The minimum input voltage equals  $V_{OUT}$  (nom) + 0.5V or 2.5V, which ever is greater.

<sup>(1)</sup> Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not verified, but do represent the most likely norm.

### DIGITAL LDOs (1, 2, 3) (continued)

Unless otherwise noted,  $V_{IN1}=V_{IN2}=V_{IN3}=V_{INB1}=V_{INB2}=V_{INLILO1}=V_{INLILO2}=3.6V$ ;  $C_{LODX}=1\mu$ F;  $C_{BUCKOUT}=C_{BUCKIN}=4.7 \mu$ F,  $C_{VIN1-3}=C_{VINLILO1}C_{VINLILO2}=2.2 \mu$ F. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J=-40$  to  $+125^{\circ}$ C. <sup>(1)</sup>

| Symbol             | Parameter                                    | Conditions                                                           | Min | Тур | Max | Unit              |

|--------------------|----------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|-------------------|

| V <sub>DO</sub>    | Dropout Voltage                              | $I_{OUT}$ = 300 mA<br>Nominal V <sub>OUT</sub> = 2.8V <sup>(3)</sup> |     | 190 | 270 | mV                |

| I <sub>OUT</sub>   | Output Current                               |                                                                      | 0   |     | 300 | mA                |

| I <sub>SLEEP</sub> | Max Output Current in<br>Sleep Mode          |                                                                      |     |     | 1   | mA                |

| I <sub>SC</sub>    | Output Current Limit                         | $V_{OUT} = 0V$                                                       |     | 650 |     | mA                |

| e <sub>N</sub>     | Output Voltage Noise                         | 10 Hz ≤ f ≤ 100 KHz<br>I <sub>OUT</sub> = 300 mA                     |     | 35  |     | μV <sub>RMS</sub> |

| PSRR               | Power Supply Rejection<br>Ratio              | f ≤ 10 KHz, I <sub>OUT</sub> = 20 mA                                 |     | 65  |     | dB                |

| t <sub>STUP</sub>  | Startup Time                                 | I <sub>OUT</sub> = 0 mA to 300 mA in Idle mode.                      |     | 20  |     | μs                |

| V <sub>OS</sub>    | Start-up Overshoot                           | $I_{OUT} = 300 \text{ mA}^{(4)}$                                     |     |     | 30  | mV                |

| C <sub>OUT</sub>   | External Output<br>Capacitance for Stability | (4)                                                                  | 0.5 | 1   | 20  | μF                |

(3) Dropout voltage is the voltage difference between the input and the output at which the output voltage drops to 100 mV below its nominal value.

(4) This specification is guaranteed by design.

### LOW-NOISE ANALOG LDOs (4, 5)

Unless otherwise noted,  $V_{IN1}=V_{IN2}=V_{IN3}=V_{INB1}=V_{INB2}=V_{INLILO1}=V_{INLILO2}=3.6V$ ;  $C_{LODX}=1\mu$ F;  $C_{BUCKOUT}=C_{BUCKIN}=4.7 \mu$ F,  $C_{VIN1-3}=C_{VINLILO2}=2.2 \mu$ F. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J=-40$  to  $+125^{\circ}$ C. <sup>(1)</sup>

| Symbol             | Parameter                                    | Conditions                                                              | Min  | Тур | Max  | Unit              |

|--------------------|----------------------------------------------|-------------------------------------------------------------------------|------|-----|------|-------------------|

|                    |                                              |                                                                         | -2   |     | +2   |                   |

| V <sub>OUT</sub>   | Output Voltage Accuracy                      | I <sub>OUT</sub> = 1mA, V <sub>OUT</sub> = 2.8V                         | -2.5 |     | +2.5 | - %               |

| ΔV <sub>OUT</sub>  | Line Regulation                              | $V_{OUT} + 0.5V \le V_{IN3} \le 4.5V$<br>$I_{OUT} = 1mA$ <sup>(2)</sup> |      | 1   |      | mV                |

|                    | Load Regulation                              | 1 < I <sub>OUT</sub> < 300 mA                                           |      | 1   |      |                   |

| V <sub>DO</sub>    | Dropout Voltage                              | $I_{OUT} = 300 \text{ mA}$<br>Nominal V <sub>OUT</sub> = 2.8V<br>(3)    |      | 220 | 310  | mV                |

| I <sub>OUT</sub>   | Output Current                               |                                                                         | 0    |     | 300  | mA                |

| I <sub>SLEEP</sub> | Max Output Current in Sleep Mode             |                                                                         |      |     | 1    | mA                |

| I <sub>SC</sub>    | Output Current Limit                         | V <sub>OUT</sub> = 0V                                                   |      | 625 |      | mA                |

| e <sub>N</sub>     | Output Voltage Noise                         | 10 Hz $\leq$ f $\leq$ 100 KHz<br>I <sub>OUT</sub> = 300 mA              | 10   | 10  |      | μV <sub>RMS</sub> |

| PSRR               | Power Supply Rejection<br>Ratio              | $f \le 10 \text{ KHz}, I_{OUT} = 20 \text{ mA}$                         |      | 75  |      | dB                |

| t <sub>STUP</sub>  | Startup Time                                 | $I_{OUT} = 0$ mA to 300 mA in Idle mode.                                |      | 35  |      | μs                |

| V <sub>OS</sub>    | Start-up Overshoot                           | I <sub>OUT</sub> = 300 mA <sup>(4)</sup>                                |      |     | 30   | mV                |

| C <sub>OUT</sub>   | External Output<br>Capacitance for Stability | (4)                                                                     | 0.5  | 1   | 20   | μF                |

(1) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not verified, but do represent the most likely norm.

(2) The minimum input voltage equals  $V_{OUT}$  (nom) + 0.5V or 2.5V, which ever is greater.

(3) Dropout voltage is the voltage difference between the input and the output at which the output voltage drops to 100 mV below its nominal value.

(4) This specification is guaranteed by design.

# LOW-INPUT LOW-OUTPUT LDO (LILO1, LILO2)

Unless otherwise noted,  $V_{IN1}=V_{IN2}=V_{IN3}=V_{INB1}=V_{INB2}=V_{INLILO1}=V_{INLILO2}=3.6V$ ;  $C_{LODX}=1\mu$ F;  $C_{BUCKOUT}=C_{BUCKIN}=4.7 \mu$ F,  $C_{VIN1-3}=C_{VINLILO1}C_{VINLILO2}=2.2 \mu$ F. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J=-40$  to  $+125^{\circ}$ C. <sup>(1)</sup>

| Symbol             | Parameter                                    | Conditions                                                                   | Min | Тур | Max | Unit          |

|--------------------|----------------------------------------------|------------------------------------------------------------------------------|-----|-----|-----|---------------|

|                    | LILO1 Output Voltage                         |                                                                              | -2  |     | +2  |               |

| N/                 | Accuracy                                     |                                                                              | -3  |     | +3  | 0/            |

| V <sub>OUT</sub>   | LILO2 Output Voltage                         | $-I_{OUT} = 1mA, V_{OUT} = 1.8V$                                             | -3  |     | +3  | %             |

|                    | Accuracy                                     |                                                                              | -4  |     | +4  |               |

| ΔV <sub>OUT</sub>  | Line Regulation                              | $V_{OUT}$ + 0.5V $\leq V_{LILO} \leq 4.5V$<br>$I_{OUT}$ = 1mA                |     | 1   |     | mV            |

|                    | Load Regulation                              | 1 < I <sub>OUT</sub> < 300 mA                                                |     | 5   |     |               |

| V <sub>DO</sub>    | Dropout Voltage                              | $I_{OUT} = 300 \text{ mA}$<br>Nominal V <sub>OUT</sub> = 1.8V <sup>(2)</sup> |     | 230 | 310 | mV            |

| I <sub>OUT</sub>   | Output Current                               |                                                                              | 0   |     | 300 | mA            |

| I <sub>SLEEP</sub> | Max Output Current in<br>Sleep Mode          |                                                                              |     |     | 1   | mA            |

| I <sub>SC</sub>    | Output Current Limit                         | $V_{OUT} = 0V$                                                               |     | 670 |     | mA            |

| e <sub>N</sub>     | Output Voltage Noise                         | 10 Hz ≤ f ≤ 100 KHz<br>I <sub>OUT</sub> = 300 mA                             |     | 80  |     | $\mu V_{RMS}$ |

| PSRR               | Power Supply Rejection<br>Ratio              | f ≤ 10 KHz, I <sub>OUT</sub> = 20 mA                                         |     | 60  |     | dB            |

| t <sub>STUP</sub>  | Startup Time                                 | $I_{OUT} = 0$ mA to 300 mA in Idle mode.                                     |     | 65  |     | μs            |

| V <sub>OS</sub>    | Start-up Overshoot                           | (3)                                                                          |     |     | 30  | mV            |

| C <sub>OUT</sub>   | External Output<br>Capacitance for Stability | (3)                                                                          | 0.5 | 1   | 20  | μF            |

(1) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not verified, but do represent the most likely norm.

(2) Dropout voltage is the voltage difference between the input and the output at which the output voltage drops to 100 mV below its nominal value.

(2) The set of a s

(3) This specification is guaranteed by design.

### LP8725 CONTROL REGISTERS

### **Table 8. Control Registers**

| ADDR | Register<br>Name     | Bit 7              | Bit 6              | Bit 5          | Bit 4           | Bit 3           | Bit 2           | Bit 1           | Bit 0           |

|------|----------------------|--------------------|--------------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 0x00 | GENERAL              | TIMESTEP           | SHORT_<br>TIMESTEP | 0              | BUCK2_<br>EN    | DVS2_V          | DVS1_V          | SLEEP_<br>MODE  | BUCK1_<br>EN    |

| 0x01 | LDO1                 | LDO1<br>T[2]       | LDO1<br>T[1]       | LDO1<br>T[0]   | LDO1<br>V[4]    | LDO1<br>V[3]    | LDO1<br>V[2]    | LDO1<br>V[1]    | LDO1<br>V[0]    |

| 0x02 | LDO2                 | LDO2<br>T[2]       | LDO2<br>T[1]       | LDO2<br>T[0]   | LDO2<br>V[4]    | LDO2<br>V[3]    | LDO2<br>V[2]    | LDO2<br>V[1]    | LDO2<br>V[0]    |

| 0x03 | LDO3                 | LDO3<br>T[2]       | LDO3<br>T[1]       | LDO3<br>T[0]   | LDO3<br>V[4]    | LDO3<br>V[3]    | LDO3<br>V[2]    | LDO3<br>V[1]    | LDO3<br>V[0]    |

| 0x04 | LDO4                 | LDO4<br>T[2]       | LDO4<br>T[1]       | LDO4<br>T[0]   | LDO4<br>V[4]    | LDO4<br>V[3]    | LDO4<br>V[2]    | LDO4<br>V[1]    | LDO4<br>V[0]    |

| 0x05 | LDO5                 | LDO5<br>T[2]       | LDO5<br>T[1]       | LDO5<br>T[0]   | LDO5<br>V[4]    | LDO5<br>V[3]    | LDO5<br>V[2]    | LDO5<br>V[1]    | LDO5<br>V[0]    |

| 0x06 | LILO1                | LILO1_<br>T[2]     | LILO1_<br>T[1]     | LILO1_<br>T[0] | LILO1_<br>V[4]  | LILO1<br>V[3]   | LILO1_<br>V[2]  | LILO1_<br>V[1]  | LILO1_<br>V[0]  |

| 0x07 | LILO2                | LILO2_<br>T[2]     | LILO2_<br>T[1]     | LILO2_<br>T[0] | LILO2_<br>V[4]  | LILO2_<br>V[3]  | LILO2_<br>V[2]  | LILO2_<br>V[1]  | LILO2_<br>V[0]  |

| 0x08 | BUCK1 V1             | BUCK1_<br>T[2]     | BUCK1_<br>T[1]     | BUCK1_<br>T[0] | BUCK1_<br>V1[4] | BUCK1_<br>V1[3] | BUCK1_<br>V1[2] | BUCK1_<br>V1[1] | BUCK1_<br>V1[0] |

| 0x09 | BUCK1 V2             | BUCK1_<br>CL[1]    | BUCK1_<br>CL[0]    | 0              | BUCK1_<br>V2[4] | BUCK1_<br>V2[3] | BUCK1_<br>V2[2] | BUCK1_<br>V2[1] | BUCK1_<br>V2[0] |

| 0x0A | BUCK2 V1             | BUCK2_<br>T[2]     | BUCK2_<br>T[1]     | BUCK2_<br>T[0] | BUCK2_<br>V1[4] | BUCK2_<br>V1[3] | BUCK2_<br>V1[2] | BUCK2_<br>V1[1] | BUCK2_<br>V1[0] |

| 0x0B | BUCK2 V2             | BUCK2_<br>CL[1]    | BUCK2_<br>CL[0]    | 0              | BUCK2_<br>V2[4] | BUCK2_<br>V2[3] | BUCK2_<br>V2[2] | BUCK2_<br>V2[1] | BUCK2_<br>V2[0] |

| 0x0C | BUCK<br>CONTROL      | BK2_<br>FLAG MASK  | BK1_<br>FLAG MASK  | PWM_<br>BUCK2  | PDN_<br>BUCK2   | 0               | 0               | PWM_<br>BUCK1   | PDN_<br>BUCK1   |

| 0x0D | LDO<br>CONTROL       | LDO1_<br>FLAG MASK | LILO2_<br>EN       | LILO1_<br>EN   | LDO5_<br>EN     | LDO4_<br>EN     | LDO3_<br>EN     | LDO2_<br>EN     | LDO1_<br>EN     |

| 0x0E | PULL<br>DOWN<br>BITS | APU_<br>TSD        | PDN<br>LILO2       | PDN<br>LILO1   | PDN<br>LDO5     | PDN<br>LDO4     | PDN<br>LDO3     | PDN<br>LDO2     | PDN<br>LDO1     |

| 0x0F | STATUS<br>BITS       | REVISION[3]        | REVISION[2]        | REVISION[1]    | REVISION[0]     | LDO1_<br>OKN    | B2_<br>OKN      | B1_<br>OKN      | TSD             |

### Table 9. Control Register Defaults

|      |                |                  | -               |                  |                 |                  |

|------|----------------|------------------|-----------------|------------------|-----------------|------------------|

|      | LP8725 Default | ts: DEFSEL state | LP8725-A Defaul | ts: DEFSEL state | LP8725-B Defaul | ts: DEFSEL state |

| ADDR | VIN1           | GND              | VIN1            | GND              | VIN1            | GND              |

| 0x00 | 0101 1001      | 0101 1001        | 0000 0000       | 0101 0001        | 1101 1101       | 1101 1101        |

| 0x01 | 1001 1001      | 0011 0101        | 0001 0101       | 1001 1001        | 1011 0101       | 1010 1100        |

| 0x02 | 1000 1100      | 0011 1001        | 0001 1101       | 0111 1001        | 1111 1001       | 1111 1001        |

| 0x03 | 1011 1111      | 0101 1001        | 1111 1111       | 0111 1001        | 1111 1001       | 1111 1001        |

| 0x04 | 1001 1111      | 0101 1001        | 0011 1101       | 1001 1001        | 1110 0000       | 1110 0000        |

| 0x05 | 1001 1001      | 0011 1001        | 0001 1001       | 1001 1001        | 1110 0000       | 1110 0000        |

| 0x06 | 1010 1000      | 0011 1111        | 0001 0000       | 1011 0000        | 1111 0111       | 1111 0111        |

| 0x07 | 0100 1000      | 0000 1000        | 0010 0100       | 1011 0000        | 1101 1111       | 1101 1111        |

| 0x08 | 0000 0100      | 0000 1000        | 1110 0110       | 0000 1010        | 0000 1000       | 0000 1000        |

| 0x09 | 1100 1000      | 1100 0100        | 1100 0100       | 1100 1000        | 1100 1000       | 1100 1000        |

| 0x0A | 0101 0001      | 0011 0001        | 1110 0110       | 0000 1010        | 1001 0001       | 1001 0001        |

| 0x0B | 1001 0001      | 1001 0001        | 1000 0100       | 1000 1000        | 1001 0001       | 1001 0001        |

| 0x0C | 0111 1111      | 0001 0001        | 1101 0001       | 1101 0001        | 0001 0001       | 0001 0001        |

Copyright © 2009–2013, Texas Instruments Incorporated

#### SNVS618G - DECEMBER 2009 - REVISED MAY 2013

www.ti.com

|      | ······································ |                  |                  |                 |                                 |           |  |  |  |

|------|----------------------------------------|------------------|------------------|-----------------|---------------------------------|-----------|--|--|--|

|      | LP8725 Default                         | ts: DEFSEL state | LP8725-A Default | s: DEFSEL state | LP8725-B Defaults: DEFSEL state |           |  |  |  |

| ADDR | VIN1                                   | GND              | VIN1             | GND             | VIN1                            | GND       |  |  |  |

| 0x0D | 0111 1111                              | 0111 1111        | 1111 1011        | 1111 1111       | 0100 0001                       | 0100 0001 |  |  |  |

| 0x0E | 0111 1111                              | 0111 1111        | 0111 1111        | 0111 1111       | 0111 1111                       | 0111 1111 |  |  |  |

| 0x0F | 0000 0000                              | 0000 0000        | 0000 0000        | 0000 0000       | 0000 0000                       | 0000 0000 |  |  |  |

### Table 9. Control Register Defaults (continued)

| 4000 | LP8725-C Default | s: DEFSEL state | LP8725-D Defaults: | DEFSEL state |

|------|------------------|-----------------|--------------------|--------------|

| ADDR | VIN1             | GND             | VIN1               | GND          |

| 0x00 | 1101 1101        | 1101 1101       | 1001 1101          | 1001 1101    |

| 0x01 | 1001 0101        | 1001 0101       | 1111 1001          | 1111 1001    |

| 0x02 | 1001 1001        | 1001 1001       | 1110 1100          | 1110 1100    |

| 0x03 | 1011 1001        | 1011 1001       | 0100 1100          | 0100 1100    |

| 0x04 | 1011 0100        | 1011 0100       | 1111 1101          | 1111 1101    |

| 0x05 | 0101 1111        | 0101 1111       | 1110 0000          | 1110 1100    |

| 0x06 | 1000 1000        | 1000 1000       | 0101 1101          | 0101 1101    |

| 0x07 | 1000 1000        | 1000 1000       | 0101 1101          | 0101 1101    |

| 0x08 | 0000 1000        | 0000 1000       | 0000 1010          | 0000 1010    |

| 0x09 | 1100 1000        | 1100 1000       | 1100 1010          | 1100 1010    |

| 0x0A | 0101 0001        | 0101 0001       | 0101 0001          | 0101 0001    |

| 0x0B | 1001 0001        | 1001 0001       | 1101 0001          | 1101 0001    |

| 0x0C | 0001 0001        | 0001 0001       | 0001 0001          | 0001 0001    |

| 0x0D | 0111 1111        | 0111 1111       | 0110 0100          | 0110 0100    |

| 0x0E | 0111 1111        | 0111 1111       | 0111 1111          | 0111 1111    |

| 0x0F | 0000 0000        | 0000 0000       | 0000 0000          | 0000 0000    |

### Table 10. Register 0X00

| Addr | Register | Bit 7    | Bit 6              | Bit 5 | Bit 4        | Bit 3  | Bit2   | Bit 1          | Bit 0    |

|------|----------|----------|--------------------|-------|--------------|--------|--------|----------------|----------|

| 0x00 | GENERAL  | TIMESTEP | SHORT_<br>TIMESTEP |       | BUCK2_E<br>N | DVS2_V | DVS1_V | SLEEP_MO<br>DE | BUCK1_EN |

| BUCK1_EN       | BUCK1, BUCK2 enable control                                                                                                                                                                                                                          |                                                                                               |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| BUCK2_EN       | In STANDBY mode<br>1: During next STARTUP sequence will be enabled.<br>0: During next STARTUP sequence will be NOT<br>enabled<br>For proper operation output timing having "111 - NO<br>startup" should have corresponding enable bit 0<br>(disable) | In IDLE mode the bit has immediate effect.<br>1: Enable<br>0: Disable                         |  |  |  |

| SLEEP_MODE     | LDO Sleep Control<br>1: SLEEP mode<br>0: normal                                                                                                                                                                                                      |                                                                                               |  |  |  |

| DVS1_V         | 1: drive buck voltage to value stored in BUCK1_V1[4:0]<br>0: Buck output voltage controlled by external DVS pin.                                                                                                                                     |                                                                                               |  |  |  |

| DVS2_V         | 1: drive buck voltage to value stored in BUCK2_V1[4:0]<br>0: Buck output voltage to value stored in BUCK2_V2[4:0]                                                                                                                                    |                                                                                               |  |  |  |

| SHORT_TIMESTEP | TIMESTEP = 0                                                                                                                                                                                                                                         | TIMESTEP = 1                                                                                  |  |  |  |