SN65LBC173A-EP

ZHCSFQ1-NOVEMBER 2016

## SN65LBC173A-EP 四路 RS-485 差分线路接收器

#### 1 特性

- 专为 TIA/EIA-485、TIA/EIA-422 和 ISO 8482 应用 设计

- 信号传输速率 (1)高达 50Mbps

- 在总线短路、开路和空闲总线条件下提供故障保护

- 为总线输入提供的静电放电 (ESD) 保护电压超过 6kV

- 共模总线电压输入范围: -7V 至 12V

- 传播延迟时间 < 18ns</li>

- 低待机功耗: < 32µA</li>

- 针对 AM26LS32、DS96F173、LTC488 和 SN75173 进行引脚兼容升级

#### 2 应用

- 支持国防、航天和医疗 应用

- 受控基线

- 同一组装和测试场所

- 同一制造场所

- 延长的产品生命周期

- 延长产品的变更通知周期

- 产品可追溯性

- (1) 线路的信号传输速率是指每秒钟的电压转换次数,单位为 bps (每秒比特数)。

#### 3 说明

SN65LBC173A 是一款具有三态输出的四路差分接收器, 专为 TIA/EIA-485 (RS-485)、TIA/EIA-422 (RS-422) 和 ISO 8482 (欧盟的 RS-485) 应用 而设计。

当数据速率高达甚至超过 5000bps 时,该器件针对均 衡后的多点总线通信进行了优化。传输介质可采用双绞 线电缆、印刷电路板走线或背板。最终数据传输速率和 距离取决于介质衰减特性和环境噪声耦合。

接收器的正负共模输入电压范围较大, 其 ESD 保护电压高达 6kV,适用于严苛环境中的 高速多点数据传输 应用。这些器件通过 LinBiCMOS<sup>®</sup>进行设计,兼具低功耗特性和极强稳定性。

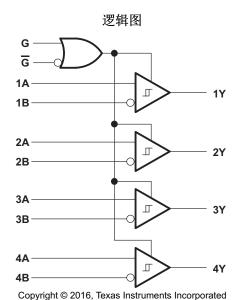

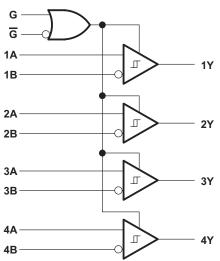

G 和 〒 输入为正/负逻辑提供使能控制逻辑,从而使能全部四个驱动器。禁用或关闭器件后,接收器输入针对总线呈现高阻抗状态,从而降低系统负载。

#### 器件信息(1)

| 器件型号           | 封装        | 封装尺寸(标称值)       |  |  |  |

|----------------|-----------|-----------------|--|--|--|

| SN65LBC173A-EP | SOIC (16) | 9.90mm x 3.90mm |  |  |  |

(1) 要了解所有可用封装,请参见数据表末尾的可订购产品附录。

M

# 目录

| 1 | 特性                                   |    | 8.3 Feature Description        | 10 |

|---|--------------------------------------|----|--------------------------------|----|

| 2 | 应用 1                                 |    | 8.4 Device Functional Modes    | 11 |

| 3 | 说明 1                                 | 9  | Application and Implementation | 12 |

| 4 | 修订历史记录 2                             |    | 9.1 Application Information    | 12 |

| 5 | Pin Configuration and Functions      |    | 9.2 Typical Application        | 12 |

| 6 | Specifications4                      | 10 | Power Supply Recommendations   | 14 |

| • | 6.1 Absolute Maximum Ratings 4       | 11 | Layout                         | 14 |

|   | 6.2 ESD Ratings                      |    | 11.1 Layout Guidelines         | 14 |

|   | 6.3 Recommended Operating Conditions |    | 11.2 Layout Example            | 14 |

|   | 6.4 Thermal Information              | 12 | 器件和文档支持                        | 15 |

|   | 6.5 Electrical Characteristics       |    | 12.1 接收文档更新通知                  | 15 |

|   | 6.6 Switching Characteristics        |    | 12.2 社区资源                      | 15 |

|   | 6.7 Typical Characteristics          |    | 12.3 商标                        | 15 |

| 7 | Parameter Measurement Information 8  |    | 12.4 静电放电警告                    | 15 |

| 8 | Detailed Description                 |    | 12.5 Glossary                  | 15 |

| • | 8.1 Overview                         | 13 | 机械、封装和可订购信息                    | 16 |

|   | 8.2 Functional Block Diagram         |    |                                |    |

# 4 修订历史记录

| 日期          | 修订版本 | 注释      |

|-------------|------|---------|

| 2016 年 11 月 | *    | 最初发布版本。 |

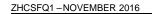

# 5 Pin Configuration and Functions

#### **Pin Functions**

|                 | PIN |     |                                           |  |  |  |  |

|-----------------|-----|-----|-------------------------------------------|--|--|--|--|

| NAME            | NO. | I/O | DESCRIPTION                               |  |  |  |  |

| 1A              | 2   | I   | RS-485 differential input (noninverting). |  |  |  |  |

| 1B              | 1   | I   | RS-485 differential input (inverting).    |  |  |  |  |

| 1Y              | 3   | 0   | Logic level output.                       |  |  |  |  |

| 2A              | 6   | I   | RS-485 differential input (noninverting). |  |  |  |  |

| 2B              | 7   | I   | RS-485 differential input (inverting).    |  |  |  |  |

| 2Y              | 5   | 0   | Logic level output.                       |  |  |  |  |

| ЗА              | 10  | I   | RS-485 differential input (noninverting). |  |  |  |  |

| 3B              | 9   | I   | RS-485 differential input (inverting).    |  |  |  |  |

| 3Y              | 11  | 0   | Logic level output.                       |  |  |  |  |

| 4A              | 14  | I   | RS-485 differential input (noninverting). |  |  |  |  |

| 4B              | 15  | I   | RS-485 differential input (inverting).    |  |  |  |  |

| 4Y              | 13  | 0   | Logic level output.                       |  |  |  |  |

| G               | 12  | I   | Active-low select.                        |  |  |  |  |

| G               | 4   | ı   | Active-high select.                       |  |  |  |  |

| GND             | 8   |     | Ground.                                   |  |  |  |  |

| V <sub>CC</sub> | 16  | _   | Power supply.                             |  |  |  |  |

#### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                                             | MIN  | MAX                   | UNIT |

|-------------------------------------------------------------------------------------------------------------|------|-----------------------|------|

| Supply voltage, V <sub>CC</sub> <sup>(2)</sup>                                                              | -0.3 | 6                     | V    |

| Voltage at any bus input (DC)                                                                               | -10  | 15                    | V    |

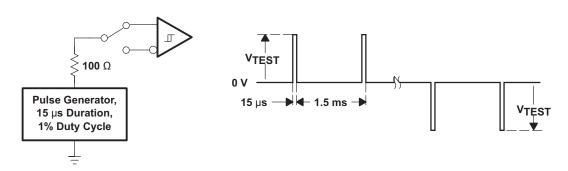

| Voltage at any bus input (transient pulse through 100 $\Omega$ , see $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $ | -30  | 30                    | V    |

| Input voltage at G and $\overline{G}$ , $V_I$                                                               | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Receiver output current, I <sub>O</sub>                                                                     | -10  | 10                    | mA   |

| Storage temperature, T <sub>stg</sub>                                                                       | -65  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                     |                | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|----------------|-------|------|

| V <sub>(ESD)</sub> |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | A and B to GND | ±6000 |      |

|                    | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC 35-001                  | All pins       | ±5000 | V    |

|                    |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | All pins       | ±2000 |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

|          |                             |      |  | MIN | NOM | MAX      | UNIT |

|----------|-----------------------------|------|--|-----|-----|----------|------|

| $V_{CC}$ | Supply voltage              |      |  |     | 5   | 5.25     | V    |

|          | Voltage at any bus terminal | A, B |  | -7  |     | 12       | V    |

| $V_{IH}$ | High-level input voltage    | G, G |  | 2   |     | $V_{CC}$ | V    |

| $V_{IL}$ | Low-level input voltage     | G, G |  | 0   |     | 0.8      | V    |

|          | Output current              | Υ    |  | -8  |     | 8        | mA   |

| TJ       | Junction temperature        | ,    |  |     |     | 125      | °C   |

#### 6.4 Thermal Information

|                  |                                              | SN65LBC173A-EP |       |

|------------------|----------------------------------------------|----------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                | D (SOIC)       | UNITS |

|                  |                                              | 16 PINS        |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 78             | °C/W  |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 39.5           | °C/W  |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 35.4           | °C/W  |

| ΨЈТ              | Junction-to-top characterization parameter   | 8.5            | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter | 35.1           | °C/W  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>2)</sup> All voltage values, except differential I/O bus voltages, are with respect to GND.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

ZHCSFQ1 -NOVEMBER 2016 www.ti.com.cn

#### 6.5 Electrical Characteristics

over recommended operating conditions

|                  | PARAMETER                                               |                      | TEST CO                                                                        | NDITIONS                                    | MIN  | TYP <sup>(1)</sup> | MAX | UNIT |

|------------------|---------------------------------------------------------|----------------------|--------------------------------------------------------------------------------|---------------------------------------------|------|--------------------|-----|------|

| V <sub>IT+</sub> | Positive-going differential inpu                        | t voltage threshold  | 71/41/ 4401/0/                                                                 |                                             |      |                    | -10 | mV   |

| V <sub>IT-</sub> | Negative-going differential input                       | ut voltage threshold | $-7 \text{ V} \le \text{V}_{\text{CM}} \le 12 \text{ V} (\text{V}_{\text{C}})$ | $_{CM} = (V_A + V_B) / 2)$                  | -200 | -120               |     | mV   |

| $V_{HYS}$        | Hysteresis voltage (V <sub>IT+</sub> – V <sub>IT-</sub> | .)                   |                                                                                |                                             |      | 40                 |     | mV   |

| VIK              | Input clamp voltage                                     |                      | $I_1 = -18 \text{ mA}$                                                         |                                             | -1.5 | -0.8               |     | V    |

| V <sub>OH</sub>  | High-level output voltage                               |                      | $V_{ID} = 200 \text{ mV},$<br>$I_{OH} = -8 \text{ mA}$                         | Coo III C                                   | 2.7  | 4.8                |     | V    |

| V <sub>OL</sub>  | Low-level output voltage                                |                      | $V_{ID} = -200 \text{ mV},$<br>$I_{OL} = 8 \text{ mA}$                         | See 图 6                                     |      | 0.2                | 0.4 | V    |

| $I_{OZ}$         | High-impedance-state output of                          | current              | $V_O = 0 V \text{ to } V_{CC}$                                                 | -1                                          |      | 1                  | μΑ  |      |

|                  | Line input number                                       |                      | Other input at 0 V,                                                            | V <sub>I</sub> = 12 V                       |      |                    | 0.9 |      |

| II               | Line input current                                      |                      | $V_{CC} = 0 V \text{ or } 5 V$                                                 | V <sub>I</sub> = -7 V                       | -0.7 |                    |     | mA   |

| I <sub>IH</sub>  | High-level input current                                | Facility involve O O |                                                                                |                                             |      |                    | 110 | μΑ   |

| I <sub>IL</sub>  | Low-level input current                                 | Enable inputs G, G   |                                                                                |                                             | -100 |                    |     | μΑ   |

| R <sub>I</sub>   | Input resistance                                        | A, B inputs          |                                                                                |                                             | 12   |                    |     | kΩ   |

|                  | Supply current                                          |                      | V <sub>ID</sub> = 5 V                                                          | G at 0 V, $\overline{G}$ at V <sub>CC</sub> |      |                    | 32  | μA   |

| I <sub>CC</sub>  |                                                         |                      | No load                                                                        | G at $V_{CC}$ , $\overline{G}$ at 0 $V$     |      | 11                 | 16  | mA   |

<sup>(1)</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  and  $25^{\circ}\text{C}$ .

### 6.6 Switching Characteristics

over recommended operating conditions

| PARAI               | METER                                                       | TEST CONDITIONS                 | MIN | TYP | MAX | UNIT |

|---------------------|-------------------------------------------------------------|---------------------------------|-----|-----|-----|------|

| t <sub>r</sub>      | Differential output voltage rise time                       |                                 |     | 2   | 7   | ns   |

| t <sub>f</sub>      | Differential output voltage fall time                       | $V_{ID} = -3 \text{ V to 3 V},$ |     | 2   | 7   | ns   |

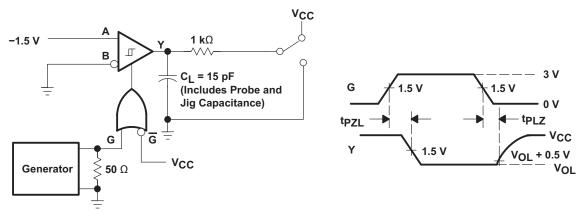

| t <sub>PLH</sub>    | Propagation delay time, low-to-high level output            | See 图 7                         | 8   | 12  | 18  | ns   |

| t <sub>PHL</sub>    | Propagation delay time, high-to-low level output            |                                 | 8   | 12  | 18  | ns   |

| t <sub>PZH</sub>    | Propagation delay time, high-impedance-to-high-level output | See 图 8                         |     | 27  | 39  | ns   |

| $t_{PHZ}$           | Propagation delay time, high-level-output-to-high impedance | See 🕅 8                         |     | 7   | 24  | ns   |

| t <sub>PZL</sub>    | Propagation delay time, high-impedance-to-low-level output  | See 图 9                         |     | 29  | 39  | ns   |

| t <sub>PLZ</sub>    | Propagation delay time, low-level-output-to-high impedance  |                                 |     | 12  | 18  | ns   |

| t <sub>sk(p)</sub>  | Pulse skew ( t <sub>PLH</sub> - t <sub>PHL</sub>  )         |                                 |     | 0.2 | 2   | ns   |

| t <sub>sk(o)</sub>  | Output skew <sup>(1)</sup>                                  |                                 |     |     | 3   | ns   |

| t <sub>sk(pp)</sub> | Part-to-part skew <sup>(2)</sup>                            |                                 |     |     | 3   | ns   |

Output skew (t<sub>sk(o)</sub>) is the magnitude of the time delay difference between the outputs of a single device with all of the inputs connected

Part-to-part skew  $(t_{sk(pp)})$  is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same input signals, the same supply voltages, at the same temperature, and have identical packages and test circuits.

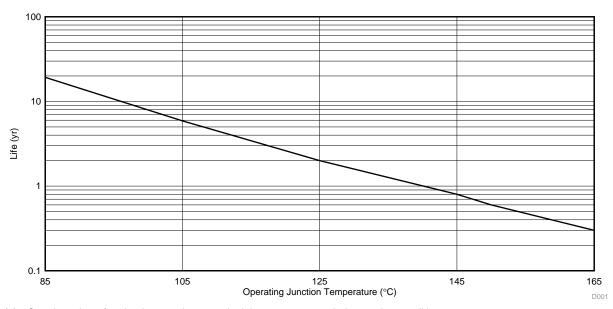

- (1) See data sheet for absolute maximum and minimum recommended operating conditions.

- (2) Silicon operating life design goal is 10 years at 105°C junction temperature (does not include package interconnect life).

- (3) Enhanced plastic product disclaimer applies.

图 1. SN65LBC173A-EP Wirebond Life Derating Chart

www.ti.com.cn

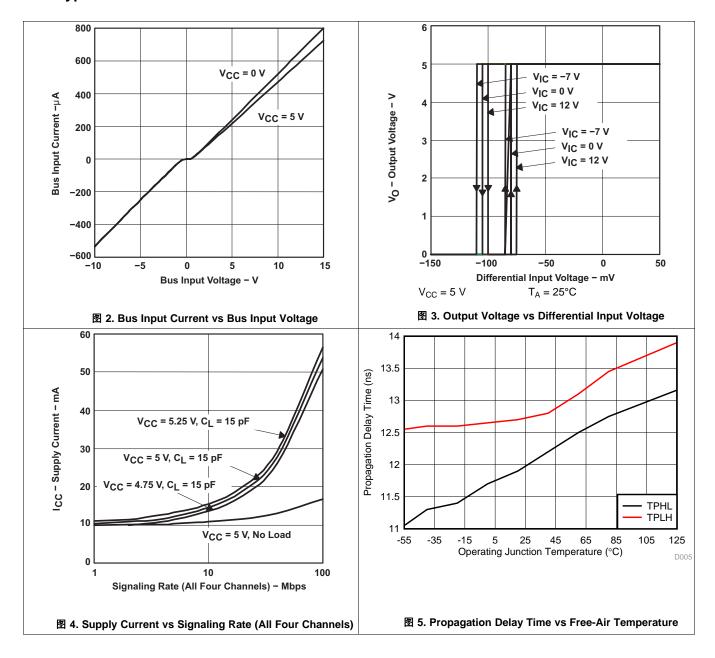

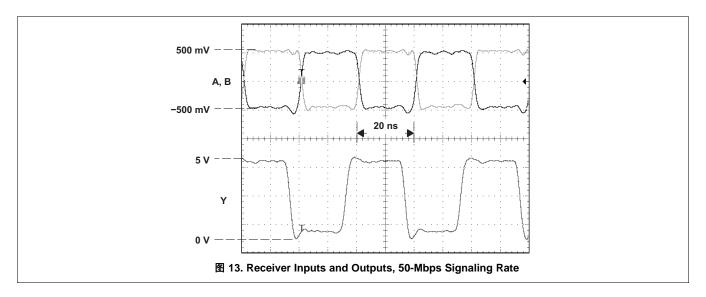

#### 6.7 Typical Characteristics

#### 7 Parameter Measurement Information

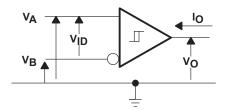

图 6. Voltage and Current Definitions

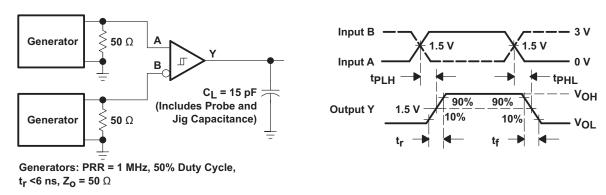

图 7. Switching Test Circuit and Waveforms

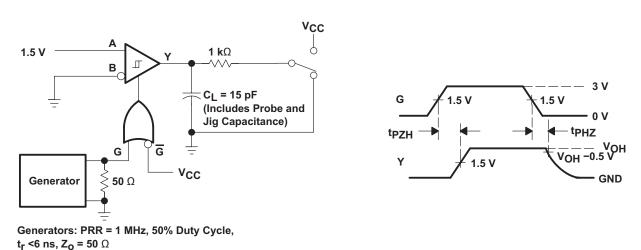

图 8. Test Circuit Waveforms,  $t_{PZH}$  and  $t_{PHZ}$

### Parameter Measurement Information (接下页)

Generators: PRR = 1 MHz, 50% Duty Cycle,  $t_{\rm r}$  <6 ns,  $\rm Z_{\rm O}$  = 50  $\rm \Omega$

### 图 9. Test Circuit Waveforms, $t_{PZL}$ and $t_{PLZ}$

图 10. Test Circuit and Waveform, Transient Over-Voltage Test

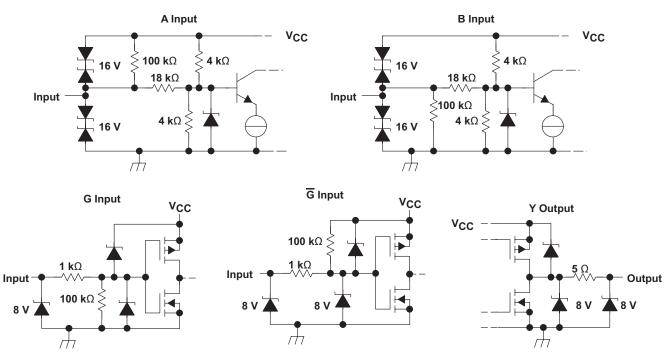

图 11. Equivalent Input and Output Schematic Diagrams

#### 8 Detailed Description

#### 8.1 Overview

The SN65LBC173A is a quadruple differential line receiver with tri-state outputs, designed for TIA/EIA-485 (RS-485), TIA/EIA-422 (RS-422), and ISO 8482 (Euro RS-485) applications. This device is optimized for balanced multipoint bus communication at data rates up to and exceeding 50 million bits per second. The transmission media may be twisted-pair cables, printed-circuit board traces, or backplanes. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

The receiver operates over a wide range of positive and negative common-mode input voltages, and features ESD protection to 6 kV, making it suitable for high-speed multipoint data transmission applications in harsh environments. These devices are designed using LinBiCMOS®, facilitating low-power consumption and robustness.

The G and  $\overline{G}$  inputs provide enable control logic for either positive- or negative-logic enabling all four drivers. When disabled or powered off, the receiver inputs present a high-impedance to the bus for reduced system loading.

#### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 8.3 Feature Description

The device can be configured using the G and  $\overline{G}$  logic inputs to select receiver output. The high voltage or logic 1 on the G pin allows the device to operate on an active-high, and having a low voltage or logic 0 on the  $\overline{G}$  enables active low operation. These are simple ways to configure the logic to match that of the receiving or transmitting controller or microprocessor.

#### 8.4 Device Functional Modes

The receivers implemented in these RS-485 device can be configured using the G and  $\overline{G}$  logic pins to be enabled or disabled. This allows users to ignore or filter out transmissions as desired.

表 1. Function Table<sup>(1)</sup>

| INPUT                                                     | FNAF | INPUT ENABLES |             |  |  |  |  |  |

|-----------------------------------------------------------|------|---------------|-------------|--|--|--|--|--|

| A - B (V <sub>ID</sub> )                                  | G    | G             | OUTPUT<br>Y |  |  |  |  |  |

|                                                           | Н    | X             |             |  |  |  |  |  |

| V <sub>ID</sub> ≤ −0.2 V                                  | Х    | L             | L           |  |  |  |  |  |

| 0.2.1/ . 1/ . 0.04.1/                                     | Н    | Х             | 2           |  |  |  |  |  |

| $-0.2 \text{ V} < \text{V}_{\text{ID}} < -0.01 \text{ V}$ | Х    | L             | ?           |  |  |  |  |  |

| 0.04.1/<.1/                                               | Н    | X             | 11          |  |  |  |  |  |

| -0.01 V ≤ V <sub>ID</sub>                                 | Χ    | L             | Н           |  |  |  |  |  |

| X                                                         | L    | Н             | Z           |  |  |  |  |  |

| ^                                                         | OPEN | OPEN          | ۷           |  |  |  |  |  |

| Short circuit                                             | Н    | X             | Н           |  |  |  |  |  |

| Short circuit                                             | Χ    | L             | 17          |  |  |  |  |  |

| Open circuit                                              | Н    | X             | Н           |  |  |  |  |  |

<sup>(1)</sup> H = high level, L = low level, X = irrelevant, Z = high impedance (off), ? = indeterminate

#### 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

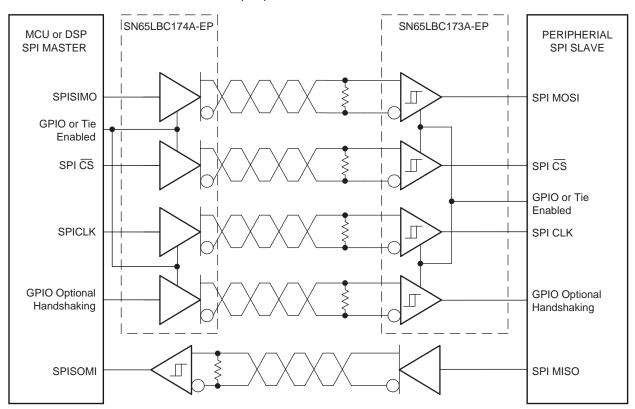

Extending SPI operation over RS-485 link.

#### 9.2 Typical Application

The following block diagram shows an MCU host connected via RS-485 to a SPI slave device. This device can be an ADC, DAC, MCU, or other SPI slave peripheral.

Copyright © 2016, Texas Instruments Incorporated

图 12. DSP-to-DSP Link via Serial Peripheral Interface

#### 9.2.1 Design Requirements

This application can be implemented using standard SPI protocol on DSP or MCU devices. The interface is independent of the specific frame or data requirements of the host or slave device. An additional but not required handshake bit is provided that can be used for customer purposes.

#### 9.2.2 Detailed Design Procedure

The interface design requirements are fairly straight forward in this single source/destination scenario. Trace lengths and cable lengths need to be matched to maximize SPI timing. If there is a benefit to put the interface to sleep, GPIOs can be used to control the enable signals of the transmitter and receiver. If GPIOs are not available, or constant uptime needed, both the enables on transmit and receive can be hard tied enabled.

## Typical Application (接下页)

The link shown can operate at up to 50 Mbps, well within the capability of most SPI links.

### 9.2.3 Application Curves

#### 10 Power Supply Recommendations

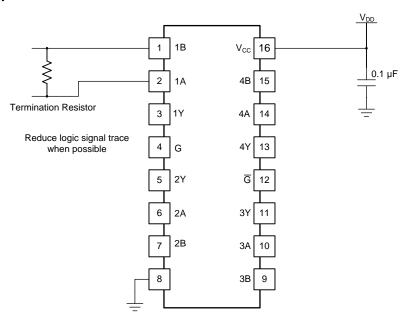

Place 0.1-μF bypass capacitors close to the power-supply pins to reduce errors coupling in from noisy or highimpedance power supplies.

#### 11 Layout

#### 11.1 Layout Guidelines

For best operational performance of the device, use good PCB layout practices including:

- Noise can propagate into analog circuitry through the power pins of the circuit as a whole, as well as the

operational amplifier. Bypass capacitors are used to reduce the coupled noise by providing low impedance

power sources local to the analog circuitry.

- Connect low-ESR, 0.1-μF ceramic bypass capacitors between each supply pin and ground, placed as close to the device as possible.

- Place termination resistor as close as possible to the input pins (if end point node).

- Keep trace lengths from input pins to buss as short as possible to reduce stub lengths and reflections on any nodes that are not end points of bus.

- To reduce parasitic coupling, run the input traces as far away from the supply or output traces as possible. If

it is not possible to keep them separate, it is much better to cross the sensitive trace perpendicular as

opposed to in parallel with the noisy trace.

#### 11.2 Layout Example

图 14. Layout with PCB Recommendations

www.ti.com.cn

#### 12 器件和文档支持

#### 12.1 接收文档更新通知

如需接收文档更新通知,请访问 www.ti.com.cn 网站上的器件产品文件夹。点击右上角的提醒我 (Alert me) 注册后,即可每周定期收到已更改的产品信息。有关更改的详细信息,请查阅已修订文档中包含的修订历史记录。

#### 12.2 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.3 商标

E2E is a trademark of Texas Instruments.

LinBiCMOS is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.4 静电放电警告

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可能会损坏集成电路。

E el

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。 精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

ZHCSFQ1 - NOVEMBER 2016 www.ti.com.cn

## 13 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。这些信息是针对指定器件可提供的最新数据。这些数据会在无通知且不对本文档进行修订的情况下发生改变。欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

### PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| SN65LBC173AMDREP | ACTIVE | SOIC         | D                  | 16   | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -55 to 125   | LBC173AEP               | Samples |

| V62/13623-02XE   | ACTIVE | SOIC         | D                  | 16   | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -55 to 125   | LBC173AEP               | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

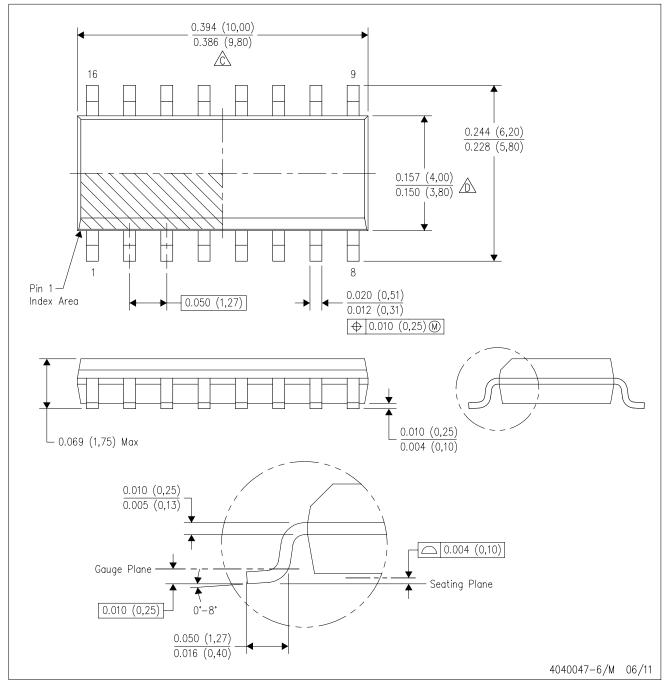

## D (R-PDS0-G16)

### PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AC.

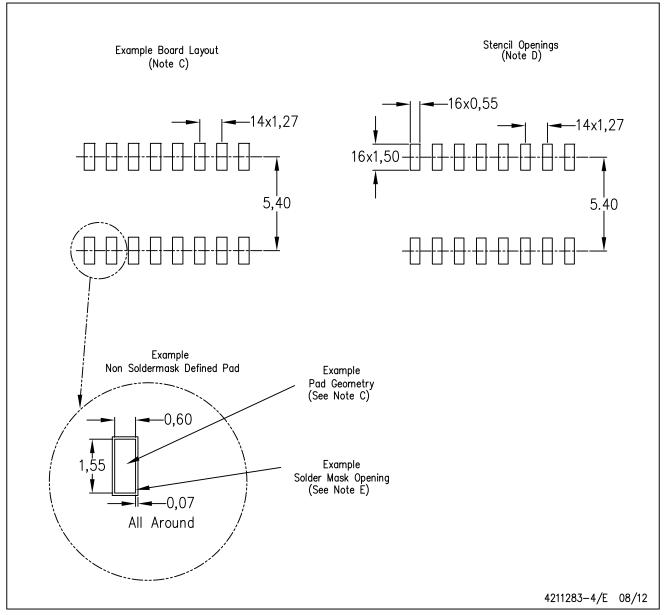

# D (R-PDSO-G16)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### 重要声明和免责声明

TI 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任: (1)针对您的应用选择合适的TI产品; (2)设计、验证并测试您的应用; (3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI 所提供产品均受TI 的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2020 德州仪器半导体技术(上海)有限公司