# LOW PIN COUNT, LOW V<sub>IN</sub> (2.5 V TO 5.5 V) SYNCHRONOUS BUCK DC-TO-DC CONTROLLER WITH ENABLE

## FEATURES

- 2.25-V to 5.5-V Input

- Output Voltage from 0.6 V to 90% of VIN

- High-Side Drive for N-Channel FET

- Supports Pre-Biased Outputs

- Adaptive Anti-Cross Conduction Gate Drive

- 1%, 0.6-V Reference

- Two Fixed Switching Frequency Versions, TPS40040 (300 kHz) and TPS40041 (600 kHz)

- Three Selectable Short Circuit Protection Levels of 105 mV, 180 mV and 310 mV

- Hiccup Restart from Faults

- Voltage Mode Control

- Active Low Enable

- Thermal Shutdown Protection at 145C

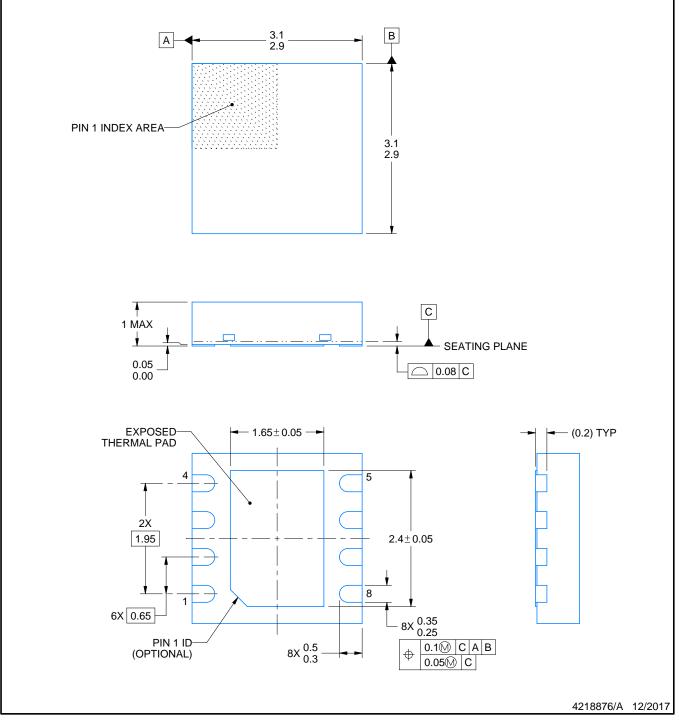

- 8-Pin, 3-mm x 3-mm SON with Ground Connection to Thermal Pad

## **APPLICATIONS**

- Point of Load

- Telecommunications

- DC to DC Modules

- Set Top Boxes

## CONTENTS

| Device Ratings             | 2  |

|----------------------------|----|

| Electrical Characteristics | 3  |

| Device Information         | 8  |

| Application Information    | 10 |

| Design Examples            | 19 |

| Additional References      | 32 |

## DESCRIPTION

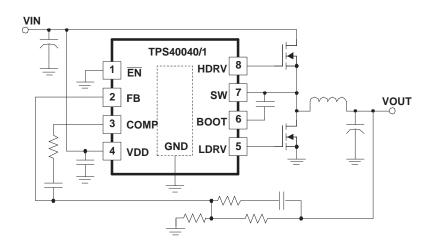

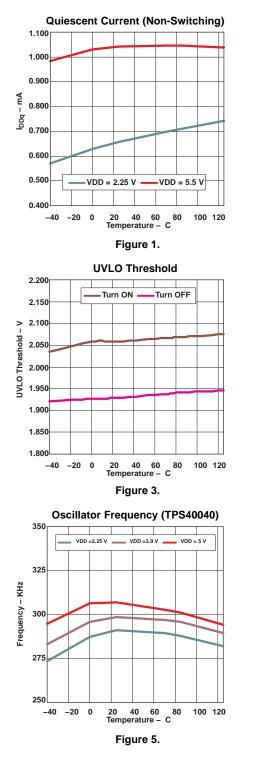

The TPS40040 and TPS40041 dc-to-dc controllers are designed to operate from a 2.25-V to 5.5-V input source. To reduce the number of external components, several operating parameters are fixed internally; namely, frequency, soft start time, and short circuit protection (SCP) levels. For example, the operating frequencies of TPS40040/1 are 300 kHz/600 kHz, respectively.

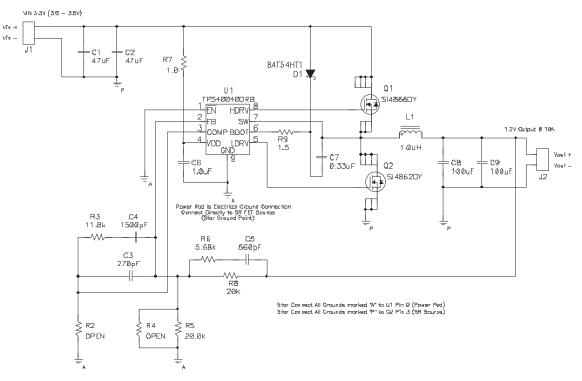

## SIMPLIFIED APPLICATION DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

Predictive Gate Drive is a registered trademark of Texas Instruments.

## **DESCRIPTION (CONT.)**

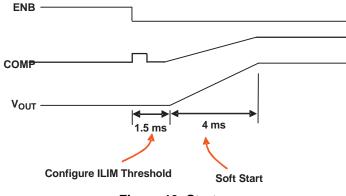

One of three short circuit threshold levels may be selected by the addition of an external resistor from the COMP pin to circuit ground. During power on, and before the internal soft start commands the output voltage to rise, the TPS40040/1 enters a calibration cycle, measures the current out of the COMP pin, and selects an internal SCP threshold voltage. At the end of the 1.6-ms calibration time, the output voltage is allowed to rise for a 4-ms soft start. During operation, the selected SCP threshold voltage is compared to the upper MOSFET's voltage drop during its ON time to determine whether there is an overload condition.

The packaging of the TPS40040/1 is unique in that the PowerPAD<sup>™</sup> is used as an electrical ground connection as well as a thermal connection.

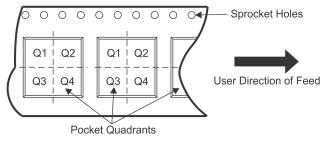

|                     | •••••••                 |                    |              |

|---------------------|-------------------------|--------------------|--------------|

| OPERATING FREQUENCY | PACKAGE                 | TAPE AND REEL QTY. | PART NUMBER  |

| 300 kHz             | Plastic 8-pin SON (DRB) | 250                | TPS40040DRBT |

| 300 kHz             | Plastic 8-pin SON (DRB) | 3000               | TPS40040DRBR |

| 600 kHz             | Plastic 8-pin SON (DRB) | 250                | TPS40041DRBT |

| 600 kHz             | Plastic 8-pin SON (DRB) | 3000               | TPS40041DRBR |

## **ORDERING INFORMATION**

## **DEVICE RATINGS**

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted, all voltages are with respect to GND.)

| PARAMETER                      | VALUE        | UNIT |  |

|--------------------------------|--------------|------|--|

| VDD                            | 6.5          |      |  |

| SW                             | -3 to 10.5   |      |  |

| SW transient (< 50 ns)         | -5           |      |  |

| BOOT                           | SW+6.5       | V    |  |

| HDRV                           | SW to SW+6.5 |      |  |

| EN, FB, LDRV                   | -0.3 to 6.5  |      |  |

| COMP                           | -0.3 to 3    |      |  |

| Operating junction temperature | -40 to 150   | – C  |  |

| Storage junction temperature   | -55 to 150   |      |  |

## **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER            |      | TYP | MAX | UNIT |

|-----------------|----------------------|------|-----|-----|------|

| V <sub>IN</sub> | Input voltage        | 2.25 |     | 5.5 | V    |

| TJ              | Junction temperature | -40  |     | 125 | С    |

## **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

| PARAMETER        | MIN    | TYP | MAX | UNIT |

|------------------|--------|-----|-----|------|

| Human body model | 2500 V |     |     | V    |

| CDM              | 1500   |     | V   |      |

## PACKAGE DISSIPATION RATINGS<sup>(1)</sup>

| THERMAL IMPEDANCE<br>JUNCTION-TO-AMBIENT | T <sub>A</sub> = 25C POWER RATING | T <sub>A</sub> = 85C POWER RATING |

|------------------------------------------|-----------------------------------|-----------------------------------|

| 48C/W                                    | 2W                                | 0.8W                              |

(1) For more information on the DRB package and the test method, refer to TI technical brief, literature number SZZA017.

## ELECTRICAL CHARACTERISTICS

$T_J$  = -40 C to 85C VDD = 5 V, (unless otherwise noted)

|                                    | PARAMETER                                                | TEST CONDITIONS                                              | MIN   | TYP   | MAX   | UNIT |  |

|------------------------------------|----------------------------------------------------------|--------------------------------------------------------------|-------|-------|-------|------|--|

| Input Supp                         | ly                                                       |                                                              |       |       |       |      |  |

| VDD                                | Input voltage range                                      |                                                              | 2.25  |       | 5.5   | V    |  |

| DD <sub>sd</sub>                   | Shutdown                                                 | EN = VDD                                                     |       | 100   | 180   | μA   |  |

| DDq                                | Quiescent                                                | FB = 0.8 V                                                   |       | 1.0   | 2.0   | ~ ^  |  |

| DDs                                | Switching current                                        | No load at HDRV/LDRV                                         |       | 2.0   |       | mA   |  |

| JVLO <sub>ON</sub>                 | Minimum turn-on voltage                                  |                                                              | 1.95  | 2.05  | 2.15  | V    |  |

| JVLO <sub>HYS</sub>                | Hysteresis                                               |                                                              | 80    | 130   | 200   | mV   |  |

| Oscillator/                        | Ramp Generator                                           |                                                              |       |       |       |      |  |

| PWM                                | TPS40040 PWM frequency                                   | 2.25 V < VDD < 5.5 V                                         | 250   | 300   | 350   | kHz  |  |

| PWM                                | TPS40040 PWM frequency                                   | $VDD = 5.0 V, 0C < T_J < 70C$                                | 270   | 300   | 330   | kHz  |  |

| PWM                                | TPS40041 PWM frequency                                   | 2.25 V < VDD < 5.5 V                                         | 500   | 600   | 700   | kHz  |  |

| PWM                                | TPS40041 PWM frequency                                   | $VDD = 5.0 V, 0C < T_{J} < 70C$                              | 540   | 600   | 660   | kHz  |  |

| / <sub>RAMP</sub>                  | Ramp amplitude PP                                        | V <sub>PEAK</sub> – V <sub>VALLEY</sub>                      | 0.75  | 0.87  | 1.0   | V    |  |

| VVALLEY                            | Ramp valley voltage                                      |                                                              |       | 0.37  |       | V    |  |

| PWM                                | L                                                        | · · ·                                                        |       | I     |       |      |  |

| MAXDUTY                            | Maximum duty cycle, TPS40040                             | V <sub>FB</sub> = 0 V, 2.25 V < VDD < 5.5 V                  | 90    | 95    |       |      |  |

|                                    | Maximum duty cycle, TPS40041                             | V <sub>FB</sub> = 0 V, 2.25 V < VDD < 5.5 V                  | 88    | 95    |       | %    |  |

| MINDUTY                            | Minimum duty cycle                                       |                                                              |       |       | 0     |      |  |

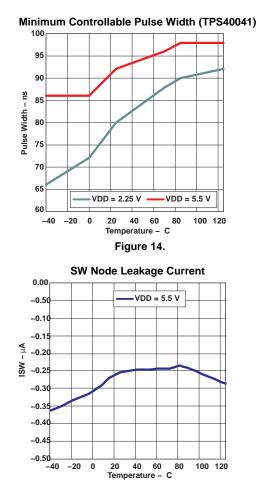

| /IN pulse<br>vidth <sup>(1)</sup>  | Minimum controllable pulse width                         | Minimum width control range before jumping to zero.          |       | 90    | 150   | ns   |  |

| Error Ampl                         | ifier                                                    | · · ·                                                        |       | I     |       |      |  |

| -                                  |                                                          | VDD = 5.0 V, 0C < T <sub>J</sub> < 70C                       | 593.5 | 600.0 | 606.5 |      |  |

| / <sub>FB</sub>                    | FB input voltage                                         | 2.25 V < VDD < 5.5 V, -40C < T <sub>J</sub> < 125C           | 590   |       | 610   | mV   |  |

| FB                                 | FB input bias current                                    |                                                              |       | 50    | 150   | nA   |  |

| / <sub>OH</sub>                    | High level output voltage                                | $I_{OH}$ = 0.5 mA, $V_{FB}$ = 0 V, VDD = 5.5 V               | 2.0   | 2.5   |       | V    |  |

| / <sub>OL</sub>                    | Low level output voltage                                 | $I_{OL} = 0.5 \text{ mA}, V_{FB} = \text{VDD}$               |       | 80    | 150   | mV   |  |

| ОН                                 | Output source current                                    | $V_{COMP} = 0.7 \text{ V}, V_{FB} = GND$                     | 1     | 6     |       |      |  |

| OL                                 | Output sink current                                      | $V_{COMP} = 0.7 \text{ V}, V_{FB} = \text{VDD}$              | 2     | 8     |       | mA   |  |

| G <sub>BW</sub> <sup>(1)</sup>     | Gain bandwidth                                           |                                                              | 5     | 10    |       | MHz  |  |

| AOL                                | Open loop gain                                           |                                                              | 55    | 85    |       | dB   |  |

|                                    | it Protection                                            |                                                              |       |       |       |      |  |

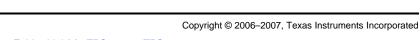

| ſH1                                | Low short circuit threshold voltage                      | Resistor COMP to GND = 2.4 k $\Omega$ , T <sub>J</sub> = 25C | 80    | 105   | 130   |      |  |

| / <sub>TH2</sub>                   | Medium short circuit threshold voltage                   | Default: No resistor COMP to GND, $T_J = 25C$                | 145   | 180   | 215   | mV   |  |

| / <sub>TH3</sub>                   | High short circuit threshold voltage                     | Resistor COMP to GND = 12 k $\Omega$ , T <sub>J</sub> = 25C  | 250   | 310   | 370   |      |  |

| / <sub>TH(tc)</sub> <sup>(1)</sup> | Threshold temperature coefficient                        |                                                              |       | 3100  |       | ppm  |  |

| ON(oc) (1)                         | Minimum HDRV pulse time in over current                  |                                                              |       | 200   |       |      |  |

| SWOCblank<br>(1)                   | SW leading edge blanking pulse in over current detection |                                                              |       | 100   |       | ns   |  |

| HICCUP                             | Hiccup time between restarts                             | 1                                                            |       | 40    |       | ms   |  |

(1) Ensured by design. Not production tested.

## **ELECTRICAL CHARACTERISTICS (continued)**

$T_J = -40 \text{ C}$  to 85C VDD = 5 V, (unless otherwise noted)

| PARAMETER                        |                                          | TEST CONDITIONS                                           | MIN  | ТҮР  | MAX  | UNIT |

|----------------------------------|------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| Soft Start/                      | Enable                                   |                                                           |      |      |      |      |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibration time before softstart begins |                                                           | 1.0  | 1.6  | 2.5  |      |

| t <sub>SS</sub> <sup>(2)</sup>   | Soft start time                          | FB rise time from 0 V to 600 mV                           | 3.0  | 4.0  | 6.0  | ms   |

| t <sub>REG</sub>                 | Time to voltage regulation               | Sum of t <sub>CAL</sub> plus t <sub>SS</sub>              | 4.0  | 5.6  | 8.5  |      |

| V <sub>EN</sub>                  | Enable threshold                         | EN voltage w.r.t. VDD                                     | -0.8 | -1.2 | -1.6 | V    |

| V <sub>ENHYS</sub>               | Enable hysteresis                        |                                                           |      | 50   |      | mV   |

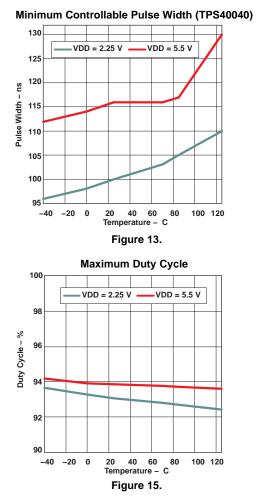

| Bootstrap                        |                                          |                                                           |      |      |      |      |

| R <sub>BOOT3V3</sub>             | Boototrop quitch registeress             | $V_{BOOT}$ to VDD, VDD = 3.3 V                            |      | 50   |      | Ω    |

| R <sub>BOOT5V</sub>              | Bootstrap switch resistances             | $V_{BOOT}$ to VDD, VDD = 5 V                              |      | 30   |      | Ω    |

| Output Dri                       | ver                                      |                                                           |      |      |      |      |

| R <sub>HDHI3V3</sub>             | HDRV pull-up resistance                  | $V_{BOOT}$ - $V_{SW}$ = 3.3 V, I <sub>SRCE</sub> = 100 mA |      | 3.0  | 5.5  |      |

| R <sub>HDLO3V3</sub>             | HDRV pull-down resistance                | $V_{BOOT}$ - $V_{SW}$ = 3.3 V, $I_{SINK}$ = 100 mA        |      | 1.5  | 3    | Ω    |

| R <sub>LDHI3V3</sub>             | LDRV pull-up resistance                  | VDD = 3.3 V, I <sub>SOURCE</sub> = 100 mA                 |      | 3.0  | 5.5  |      |

| R <sub>LDLO3V3</sub>             | LDRV pull-down resistance                | VDD = 3.3 V, I <sub>SINK</sub> = 100 mA                   |      | 1.0  | 2.0  |      |

| t <sub>RISE</sub> <sup>(3)</sup> | LDRV, HDRV rise time                     | C <sub>LOAD</sub> = 1 nF                                  |      | 15   | 35   |      |

| t <sub>FALL</sub> <sup>(3)</sup> | LDRV, HDRV fall time                     | C <sub>LOAD</sub> = 1 nF                                  |      | 10   | 25   |      |

| T <sub>DEAD</sub> HL             | Adaptive timing HDRV to LDRV             | No load                                                   | 15   | 30   |      | ns   |

| T <sub>DEAD</sub> LH             | Adaptive timing LDRV to HDRV             | No load                                                   | 5    | 15   |      |      |

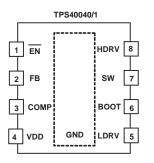

| SW Node                          |                                          |                                                           |      |      |      |      |

| I <sub>LEAK</sub>                | Leakage current                          | EN = VDD                                                  | -2   |      |      | μΑ   |

| Thermal S                        | hutdown                                  |                                                           |      |      | 1    |      |

| t <sub>SD</sub> <sup>(3)</sup>   | Shutdown temperature                     |                                                           |      | 145  |      | 0    |

|                                  | Hysteresis                               |                                                           |      | 15   |      | С    |

$t_{\text{CAL}}$  and  $t_{\text{SS}}$  track with temperature and input voltage Ensured by design. Not production tested. (2) (3)

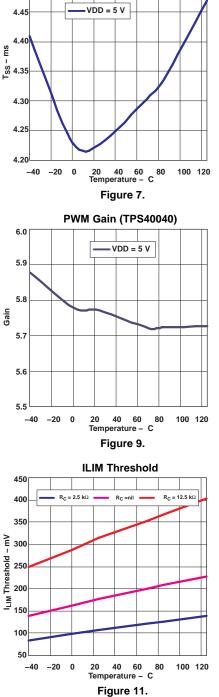

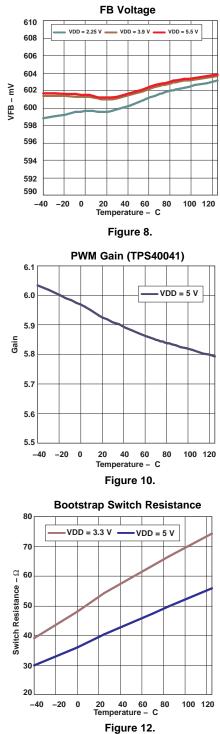

## **TYPICAL CHARACTERISTICS**

4.50

#### SLUS700D-MARCH 2006-REVISED DECEMBER 2007

## **TYPICAL CHARACTERISTICS (continued)**

Figure 16.

## TPS40040, TPS40041

SLUS700D-MARCH 2006-REVISED DECEMBER 2007

## **DEVICE INFORMATION**

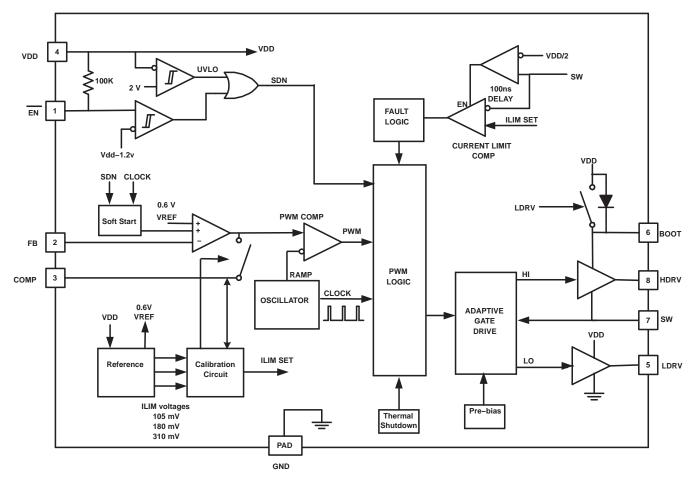

## **TERMINAL CONFIGURATION**

The package is an 8-pin SON (DRB) package. Note: The thermal pad is an electrical ground connection.

## Figure 17. DRB Package Terminal Configuration (Top View)

| TERMINAL |             | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.         | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| воот     | 6           | I   | Input (bootstrapped) supply to the high-side gate driver for PWM enabling the gate of the high side FET to be driven above the input supply rail. Connect a ceramic capacitor from this pin to SW. This capacitor is charged from the VDD pin voltage through an internal switch. The switch is turned ON during the off time of the converter. To slow down the turn on of the external MOSFET, a small resistor (1 $\Omega$ to 3 $\Omega$ ) may be placed in series with the bootstrap capacitor. See Applications Section to calculate the appropriate value. |

| СОМР     | 3           | 0   | <ul> <li>Output of the error amplifier and connection node for loop feedback components. The voltage at this pin determines the duty cycle for the PWM. Optionally, a resistor from this pin to ground is used to determine the voltage threshold used for short circuit protection. (See Application Section)</li> <li>Low threshold R = 2.4 kΩ, +/-10%</li> <li>Mid threshold R = not installed</li> <li>High threshold R = 12 kΩ, +/-10%</li> </ul>                                                                                                           |

| EN       | 1           | I   | Active low enable input allows ON/OFF operation of the controller. If power is applied to the TPS40040/1 while the $\overline{EN}$ pin is allowed to float high, the TPS40040/1 remains disabled (both external switches are held OFF). Only when the $\overline{EN}$ pin is pulled to 1.2 V below VDD is the TPS40040/1 allowed to start. An internal 100-k $\Omega$ resistor is connected between VDD and $\overline{EN}$ to provide pull up. Connect this pin to GND to bypass the enable function.                                                           |

| FB       | 2           | I   | Inverting input of the error amplifier. In closed loop operation, the voltage at this pin is at the internal reference level of 600 mV. A series resistor divider from the converter output to ground, with the center connection tied to this pin, determines the value of the regulated output voltage. This pin is also a connection node for loop feedback components.                                                                                                                                                                                       |

| HDRV     | 8           | 0   | This is the gate drive output for the high side N-channel MOSFET switch for PWM. It is referenced to SW and is bootstrapped for enhancement of the high-side switch.                                                                                                                                                                                                                                                                                                                                                                                             |

| LDRV     | 5           | 0   | Gate drive output for the low-side synchronous rectifier (SR) N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDD      | 4           | I   | Power input to the device. This pin should be locally bypassed to GND with a low ESR ceramic capacitor of 1 $\mu\text{F}$ or greater.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SW       | 7           | 0   | Connection to the switched node of the converter and the power return for the upper gate driver. There should be a high current return path from the source of the upper MOSFET to this pin. It is also used by the adaptive gate drive circuits to minimize the dead time between upper and lower MOSFET conduction.                                                                                                                                                                                                                                            |

| GND      | Thermal Pad |     | Ground connection to the device. This is also the thermal pad used to conduct heat from the device. This connection serves a twofold purpose. The first is to provide an electrical ground connection for the device. The second is to provide a low thermal impedance path from the device die to the PCB. This pad should be tied externally to a ground plane. See Application Section for PC board layout information.                                                                                                                                       |

## Table 1. TERMINAL FUNCTIONS

## **Block Diagram**

Figure 18. Functional Block Diagram

## **APPLICATION INFORMATION**

## **Functional Description**

The TPS40040 (300 kHz) and TPS40041 (600 kHz) are fixed-frequency voltage-mode synchronous buck controllers. In operation, the synchronous rectifier (SR) is allowed to conduct current in both directions, allowing a converter to operate in continuous mode, even under no load conditions, simplifying feedback loop compensation requirements. During startup, internal circuitry modulates the switching of the synchronous rectifier to prevent discharging of the output if a pre-biased condition exists.

#### Voltage Reference

The 600-mV bandgap reference voltage cell is internally connected to the non-inverting input of the error amplifier. The voltage reference is trimmed with the error amplifier in a unity gain configuration to remove amplifier offset from the final regulation voltage.

#### Voltage Error Amplifier

The error amplifier has a bandwidth of greater than 5 MHz, and open loop gain of at least 55 dB. The output voltage swing is limited to just above and below the oscillator ramp levels to improve transient response.

## Loop Compensation

Voltage mode buck type converters are typically compensated using Type III networks. Please refer to the Design Example for detailed methodology in designing feedback loops for voltage mode converters.

## Oscillator

The oscillator frequency is internally fixed. The TPS40040/1 operating frequencies are 300 kHz/600 kHz, respectively.

## UVLO

When the input voltage is below the UVLO threshold, the TPS40040/1 turns off the internal oscillator and holds all gate drive outputs in the low (OFF) state. When the input rises above the UVLO threshold, and the  $\overline{EN}$  pin is below the turn ON threshold, the start-up sequence is allowed to begin.

## **Enable and Start-Up Sequence**

The EN pin of the TPS40040/1s internally pulled to VDD. When power is applied to VDD, the EN pin is allowed to float high, and the TPS40040/1 remains OFF. Only when the EN pin is externally pulled below the threshold voltage of VDD - 1.2 V is the TPS40040/1 allowed to start. When enabled, the TPS40040/1 enters a calibration cycle where the short circuit current threshold is determined. The TPS40040/1 monitors the current out of the COMP pin and selects a threshold based on the sensed value of the current. See Selecting the Short Circuit Current Limit Threshold section for for details. When this calibration time is completed, the soft-start cycle is allowed to begin. See Figure 19 below.

Figure 19. Startup

| DESIGN<br>HINT: | If the enable function is not used, the $\overline{EN}$ pin should be connected to ground (GND). |

|-----------------|--------------------------------------------------------------------------------------------------|

|                 |                                                                                                  |

**DESIGN** When designing the feedback loop compensation, ensure the capacitors used are not so large that they distort the COMP pin calibration waveform.

## Soft Start

At the end of a calibration cycle, the TPS40040/1 slowly increases the voltage to the non-inverting input of the error amplifier. In this way, the output voltage slowly ramps up until the voltage on the non-inverting input to the error amplifier reaches the internal reference voltage. At that time, the voltage at the non-inverting input to the error amplifier remains at the reference voltage.

During the soft-start interval, pulse-by-pulse current limiting is active. If seven consecutive current limit pulses are detected, overcurrent is declared and a timeout period equivalent to seven calibration/soft-start cycles goes into effect. See Output Short Circuit Protection section for details.

## **Pre-Bias Startup**

The TPS40040/1 supports pre-biased output voltage applications. In cases where the output voltage is held up by external means while the TPS40040/1 is off, full synchronous rectification is disabled during the initial phase of soft starting the output voltage. When the first PWM pulses are detected during soft start, the controller slowly initiates synshronous rectification by starting the synchronous rectifier with a narrow on time. It then increments that on time on a cycle-by-cycle basis until it coincides with the time dictated by (1-D), where D is the duty cycle of the converter. This approach prevents the sinking of current from a pre-biased output, and ensures the output voltage startup and ramp to regulation is smooth and controlled.

#### NOTE:

If the output is pre-biased, PWM pulses start when the internal soft-start voltage rises above the error amplifier input (FB pin).

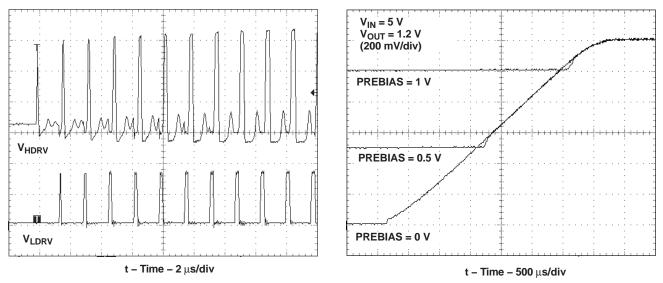

Figure 20 below depicts the waveform of the HDRV and LDRV output signals at the beginning PWM pulses. When HDRV turns off, diode rectification is enabled. Before the next PWM cycle starts, LDRV is turned on for a short pulse. With every clock cycle, the leading edge of LDRV is modulated, increasing the on time of the synchronous rectifier. Eventually, the leading edge of LDRV coincides with the falling edge of HDRV to achieve full synchronous rectification. During normal operation of the converter, the TPS40040/1 operates in full two quadrant source/sink mode.

Figure 21 shows the startup waveform of a 1.2-V output converter under three different pre-biased output conditions. The lowest trace is when there is no pre-bias on the output. The center and top most traces indicate converter startup with 0.5-V and 1.0-V pre-bias conditions.

Figure 20. MOSFET Drivers at Beginning of Soft Start

Figure 21. Startup Waveforms

The recommended output voltage pre-bias range is less than or equal to 90% of the final regulation voltage. A pre-biased output voltage of 90% to 100% of final regulation could lead to the sinking of current from the pre-bias source. If the pre-biased voltage is greater than the designed converter output regulation voltage, then upon the completion of the soft-start interval, the TPS40040/1 draws current from the output to bring the output voltage into regulation.

## **Output Short Circuit Protection**

To minimize circuit losses, the TPS40040/1 uses the  $R_{DS(on)}$  of the upper MOSFET switch as the current sensing element. The current limit comparator, initially blanked during the first portion of each switching cycle, senses the voltage across the high-side MOSFET when it is fully ON. This voltage is compared to an internally selected short circuit current (SCC) limit threshold voltage. If the comparator senses a voltage drop across the high-side MOSFET greater than the SCC limit threshold, it outputs an OC pulse. This terminates the current PWM pulse preventing further current ramp-up, and sets the fault counter to count up one count on the next clock cycle. Similarly, if no OC pulse is detected, the fault counter decrements by one count. If seven OC pulses are summed, a fault condition is declared and the upper switch of the PWM output of the chip is immediately disabled (turned OFF) and remains that way until the fault time-out period has elapsed. Both HDRV and LDRV drivers are kept OFF during the fault time-out.

The fault time-out period is determined by cycling through seven internal soft-start time periods. At the end of the fault time-out period, startup is attempted again.

The main purpose is for hard fault protection of the power switches. The internal SCC voltage has a positive temperature coefficient designed to improve the short circuit threshold tolerance variation with temperature. However, given the tolerance of the voltage thresholds and the R<sub>DS(on)</sub> range for a MOSFET, it is possible to apply a load that thermally damages the external MOSFETs.

## Selecting the Short Circuit Current Limit Threshold

The TPS40040/1 uses one of three user selectable voltage thresholds. During the calibration interval at power on or enable (Figure 19), the TPS40040/1 monitors the current out of the COMP pin and selects a threshold based on the sensed value. If the current is zero; that is, no resistor is connected between COMP and GND, then the threshold voltage level is 180 mV. If a 2.4-k $\Omega$  resistor is connected between COMP and GND, then the threshold voltage level is 105 mV. If a 12-k $\Omega$  resistor is connected between COMP and GND, then the threshold voltage level is 105 mV. If a 12-k $\Omega$  resistor is connected between COMP and GND, then the threshold voltage is 310 mV.

Once calibration is complete, the selected SCP threshold level is latched into place and remains constant. In addition, the sensing circuits on COMP pin during calibration are disconnected from the COMP pin, and soft start is allowed to begin.

#### **Synchronous Rectification and Gate Drive**

In a buck converter, when the upper switch MOSFET turns off, current is flowing in the inductor to the load. This current cannot be stopped immediately without using infinite voltage. To give this current a path to flow and maintain voltage levels at a safe level, a rectifier or catch device is used. This device can be either a diode, or it can be a controlled active device. The TPS40040/1 provides a signal to drive an N-channel MOSFET as a synchronous rectifier (SR). This control signal is carefully coordinated with the drive signal for the main switch so that there is minimum dead time from the time that the SR turns OFF and the upper switch MOSFET turns ON, and minimum delay from when the upper switch MOSFET turns OFF and the SR turns ON.

#### NOTE:

The longer the time spent in diode conduction during the rectifier conduction period, the lower the converter efficiency.

The drivers for the external HDRV and LDRV MOSFETs are capable of driving a gate to source voltage of approximately 5 V. At VDD = 5 V, the drivers are capable of driving MOSFETs appropriate for a 15-A converter. The LDRV driver switches between VDD and ground, while HDRV driver is referenced to SW and switches between BOOT and SW. The drivers have non-overlapping timing that is governed by an adaptive delay circuit that minimizes body diode conduction in the synchronous rectifier.

#### Gate Drive Resistors

The TPS40040/41's adaptive gate delay circuitry monitors the HDRV-to-SW and LDRV-to-GND voltages to determine the state of the external MOSFET switches. Any voltage drop across an external series gate drive resistor is sensed as reduced gate voltage during turn-off and may interfere with the MOSFET timing.

**DESIGN** A resistor should never be placed in series with the synchronous rectifiers gate and the gate trace should be kept as short as practical in the layout.

#### **Total Gate Charge**

The internal voltage sensing of the external MOSFET gate voltages used by the TPS40040/1 to control the dead-times between turn-off and turn-on can be sensitive to large MOSFET gate charges, especially when different gate charges are used for the high-side and low-side MOSFETs. Increased gate charge increases MOSFET switching times and decreases the dead-time between the MOSFETs switching.

|        | MOSFETs with no more than 40 nC of total gate charge should be selected.   |

|--------|----------------------------------------------------------------------------|

| DESIGN | The upper switch MOSFET's gate charge should be no less than 60% of the    |

| HINT:  | synchronous rectifier's gate charge to minimize the turn-on/turn-off delay |

|        | mismatch between the high-side and low-side MOSFET.                        |

#### Synchronous Rectifier dV/dt Turn-On

As the upper switch MOSFET turns on, the switch node voltage rises from close to ground to VIN in a very short period of time (typically 10 ns to 30 ns) resulting in very high voltage spikes on the switch node. The construction of a MOSFET creates parasitic capacitances between its terminals, particularly the gate-to-drain and gate-to-source, creating a capacitive divider between the drain and source of the MOSFET with the gate at its mid-point. If the gate-to-drain charge ( $Q_{GD}$ ) is larger than the gate-to-source charge ( $Q_{GS}$ ), the capacitive divider places proportionally more charge on the gate of the MOSFET as the switch node voltage rises than is shunted to GND. In extreme cases, this can cause the synchronous rectifier gate voltage to rise above the turn on threshold voltage of the MOSFET and causes cross-conduction. This is called dV/dt turn-on. It increases power dissipation in both the high-side and the low-side MOSFET, reducing efficiency.

| DESIGN<br>HINT: | Select a synchronous rectifier MOSFET with a $Q_{GD}$ to $Q_{GS}$ ratio of less than one and provide a wide, low resistance, low inductance loop in the synchronous rectifier gate drive circuit. (See Layout Consideration) |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                                                                                                                                                                                                                              |

**DESIGN HINT:** A resistor in series with the boost capacitor slows the turn on of the high-side MOSFET, and reduces the dV/dt of the switch node. See Boost Capacitor Series Resistor section.

## Bootstrap for N-Channel MOSFET Drive

The PWM duty cycle is limited to a maximum of 95%, allowing the bootstrap capacitor to charge during every cycle. During each PWM OFF period, the voltage on VDD charges the bootstrap capacitor. When the PWM switch is next commanded to turn ON, the voltage used to drive the MOSFET is derived from the voltage on this capacitor. Since this is a charge transfer circuit, the value of the bootstrap capacitor must be sized such that the energy stored in the capacitor on a per cycle basis is greater then the gate charge requirement of the MOSFET being used. See the Design Example section for details.

#### **Bootstrap Capacitor Series Resistor**

Since resistors should not be placed in series with the high-side gate, it may be necessary to place a small 1- $\Omega$  to 3- $\Omega$  resistor in series with the bootstrap capacitor to control the turn-on of the main switching MOSFET and reduce the dV/dt rate of rise of the switch node voltage. A resistor placed between the BOOT pin and the bootstrap capacitor increases the series resistance during the turn-on of the high-side MOSFET, and has no effect during the high-side MOSFET's turn-off period. This prevents the TPS40040/1 from sensing the upper switch MOSFET's turn-off to early and reducing the upper switch MOSFET turn-off to the SR MOSFET turn-on delay timing too far.

**DESIGN** To reduce EMI, place a small  $1-\Omega$  to  $3-\Omega$  resistor in series with the boost capacitor to control the turn-on of the main switching FET.

#### External Schottky Diode for Low Input Voltage

The TPS40040/1 uses an internal P-channel MOSFET switch between VDD and BOOT to charge the bootstrap capacitor during synchronous rectifier conduction time. At low input voltages, a MOSFET can not be turned on hard enough to rapidly replenish the charge required to turn on an (high gate charge) external high-side MOSFET. For this situation, an external Schottky diode between the VDD and BOOT pins may be added. While the diode carries very small average current ( $Q_G \times F_{SW}$ ) it may be required to carry several hundred mA of peak surge current. The diode should be rated for at least 500 mA of surge current. For higher input voltage applications, if a resistor is used in series with the boost capacitor, connect the diode to the junction of the resistor and capacitor to remove the added resistance from the capacitor's charge path.

**DESIGN HINT:** For low input voltages, and a high gate charge upper switch MOSFET, a small Schottky diode should be placed from VDD to BOOT. Do not use a resistor in series with the boost capacitor.

## **VDD Bypass and Filtering**

To prevent switching noise from being injected into the TPS40040/1 control circuitry, a ceramic capacitor (1  $\mu$ F minimum) must be placed as close to the VDD pin and GND pad as possible.

(1)

#### **VDD Filter Resistor**

To further limit the noise on VDD, a small  $1-\Omega$  to  $2-\Omega$  resistor may be placed between the input voltage and the VDD pin to create a small filter to VDD. The resistor should connect near the drain of the upper switch MOSFET to prevent trace IR drops from increasing the sensed voltage drop. The resistor itself should be placed close to Pin 4.

The current through the resistor includes the device's no-load switching current of 2 mA plus gate switching current. The voltage drop induced across this resistor reduces the VDD-to-SW voltage sensed by the over current protection circuitry within the device. This results with the apparent voltage drop across the upper switch MOSFET being increased, thereby decreasing the current at which protection will occur. To minimize this effect, the resistor value should be selected to yield less than a 25-mV drop.

## **Thermal Shutdown**

If the junction temperature of the device reaches the thermal shutdown level, the PWM and the oscillator are turned off and HDRV and LDRV are driven off. When the junction cools to the required level, the PWM soft starts as during a normal power-up cycle.

## **Package Power Dissipation**

The power dissipation in a controller is largely dependent on the MOSFET driver currents and the input voltage. The driver current is proportional to the total gate charge,  $Q_G$ , of the external MOSFETs, and the operating frequency of the converter. Driver power, neglecting external gate resistance, is calculated from:

$$P_{D(driver)} = Q_{G} \times V_{DRIVE} \times F_{SW} W/driver$$

And the total power dissipation, assuming the same MOSFET is selected for both the high side and synchronous rectifier is:

$$P_{T} = \left(\frac{2 \times P_{D}}{V_{DRIVE}} + I_{Q}\right) \times V_{DD} W$$

(2)

or

$$P_{T} = (2 \times G_{Q} \times F_{SW} + I_{Q}) \times V_{DD} W$$

(3)

where  $I_Q$  is the quiescent operating current (neglecting drivers).

The max power capability of the PowerPad<sup>™</sup> package is dependent on the layout as well as air flow. The thermal impedance from junction-to-air assuming 2-oz copper trace and thermal pad with solder and no air flow is detailed in Reference [5].

## **PCB Layout Guidelines**

A synchronous BUCK power stage has two primary current loops, the input current loop that carries high ac discontinuous current and an output current loop that carries high dc continuous current. The output current loop carries low ac inductor ripple current.

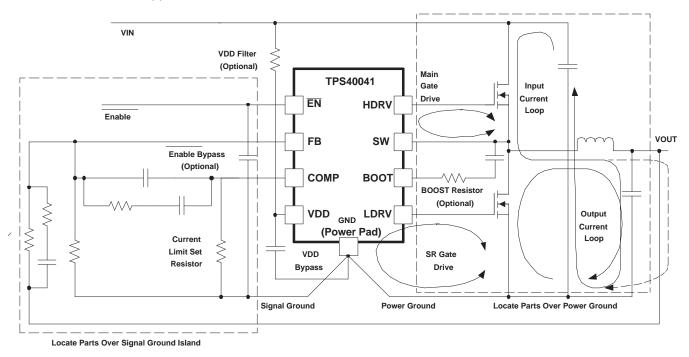

Figure 22. Synchronous BUCK Power Stage

#### **Power Component Routing**

As shown in Figure 22, the input current loop contains the input capacitors, the switching MOSFET, the inductor, the output capacitors, and the ground path back to the input capacitors. To keep this loop as small as possible, it is good practice to place some ceramic capacitance directly between the drain of the main switching MOSFET and the source of the synchronous rectifier (SR) through a power ground plane directly under the MOSFETs.

The output current loop includes the filter inductor, the output capacitors, and the ground return between the output capacitors and the source of the synchronous rectifier MOSFET. As with the input current loop, the ground return between the output capacitor ground and the source of the SR source should be routed under the inductor and MOSFETs to minimize the power loop area.

#### Device to Power Stage Interface

The TPS40040/1 uses a very fast break-before-make anti-cross conduction circuit to minimize power loss. Adding external impedance in series with the gates of the switching MOSFETs adversely affects the converter's operation and must be avoided. The loop impedance (HDRV-to-gate plus source-to-SW and LDRV-to-SR gate plus SR source-to-GND) should be kept to less than 20 nH to avoid possible cross-conduction. The HDRV and LDRV connections should widen to 20 mils as soon as possible out from the device pin.

The return for the main switching MOSFET gate drive is the SW pin of the TPS40040/1. The SW pin should be routed to the source of the main switching FET with at least a 20-mils wide trace as close to the HDRV trace as possible to minimize loop impedance.

The return for the SR MOSFET gate drive is the TPS40040/1 GND pad. The GND pad should be connected directly to the source of the SR with at least a 20-mil wide trace directly under the LDRV trace. Use a minimum of 2 parallel vias to connect the GND pad to the source of the SR if multiple layers are used.

A small, less than  $3-\Omega$  resistor may be added in series with the BOOT pin to slow the turn-on of the upper switch MOSFET, thereby reducing the rising edge slew-rate of the switch node. In turn, this reduces EMI, increases upper MOSFET OFF to SR ON dead time, and minimizes induced dV/dt turn-on of the SR when the upper switch MOSFET turns on. It is recommended customers make provisions on their boards for this resistor and not use resistors in series with MOSFET gate leads.

#### VDD Filtering

A ceramic capacitor, 1  $\mu$ F minimum, must be placed as close to the VDD pin and GND pad as possible with a 15-mil wide (or greater) trace. If used, a small series connected resistor (1  $\Omega$  to 2  $\Omega$ ) may be placed less than 100 mils from the TPS40040/1 between the supply input voltage and the VDD pin to further reduce switching noise on the VDD pin.

#### NOTE:

The voltage drop across this resistor affects the level at which the over-current circuit operates by filtering the sensed VDD voltage.

#### **Device Connections**

If a current limit resistor is used (COMP to GND), it must be placed within 100 mils of the COMP pin to limit noise injection into the PWM comparator. Compensation components (feedback divider, and associated error amplifier components) should be placed over a signal ground island connected to the power ground at the GND pad through a 10-mil wide trace. If multiple layers are used, connect to GND through a single via on an internal layer opposite the connection to the source of the synchronous rectifier.

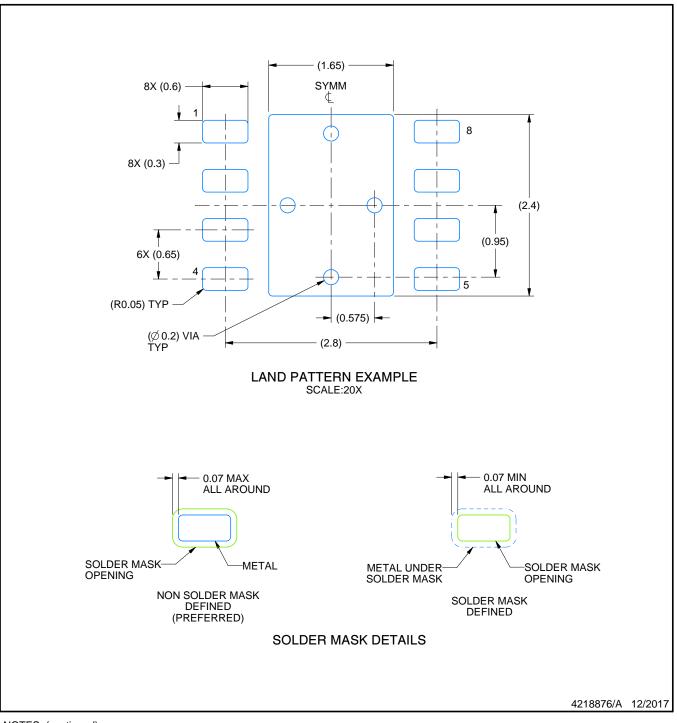

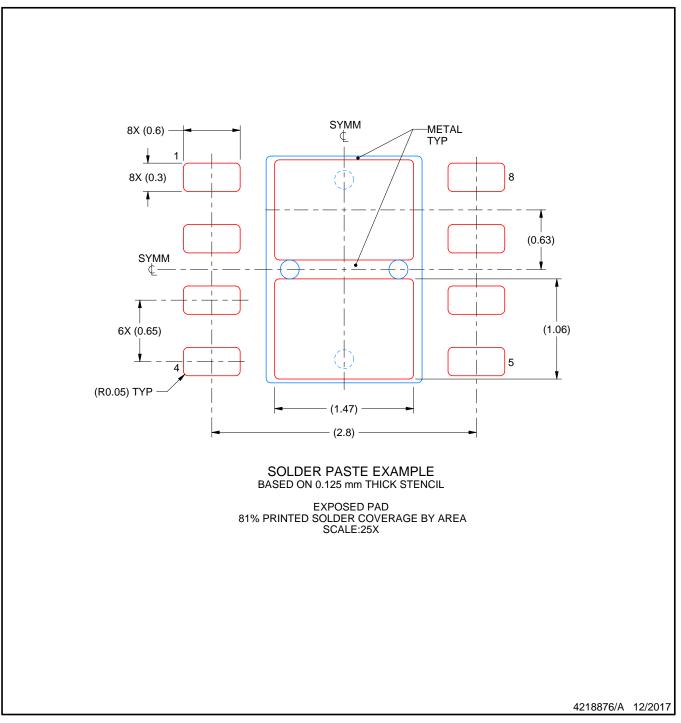

#### PowerPAD<sup>™</sup> Layout

The PowerPAD<sup>™</sup> package provides low thermal impedance for heat removal from the device. The PowerPAD<sup>™</sup> derives its name and low thermal impedance from the large bonding pad on the bottom of the device. The circuit board must have an area of solder-tinned-copper underneath the package. The dimensions of this area depend on the size of the PowerPAD<sup>™</sup> package. See PCB Layout Guidelines for further information.

Thermal vias connect this area to internal or external copper planes and should have a drill diameter sufficiently small so that the via hole is effectively plugged when the barrel of the via is plated with copper. This plug is needed to prevent wicking the solder away from the interface between the package body and the solder-tinned area under the device during solder reflow. Drill diameters of 0.33 mm (13 mils) works well when 1-oz copper is plated at the surface of the board while simultaneously plating the barrel of the via. If the thermal vias are not plugged when the copper plating is performed, then a solder mask material should be used to cap the vias with a diameter equal to the via diameter plus 0.1 mm minimum. This capping prevents the solder from being wicked through the thermal vias and potentially creating a solder void under the package. Refer to PowerPAD<sup>TM</sup> Thermally Enhanced Package<sup>[2]</sup> for more information on the PowerPAD<sup>TM</sup> package.

## **DESIGN EXAMPLES**

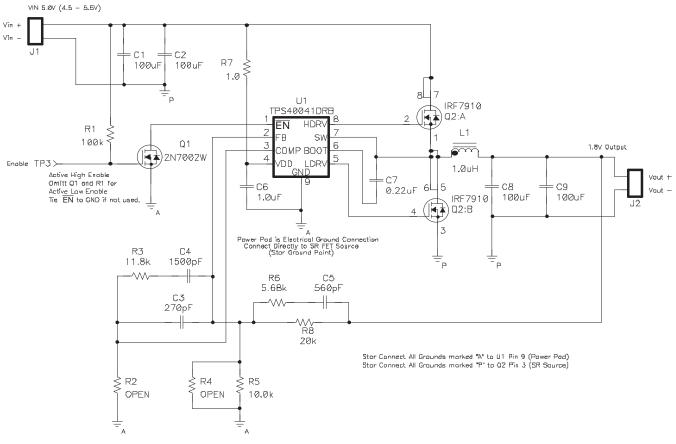

## Example 1. A 5-V to 1.8-V DC-to-DC Converter Using a TPS40041

The following example illustrates the design process and component selection for a 5-V to 1.8-V point-of-load synchronous buck converter. The design goal parameters are given in the table below. A list of symbol definitions is found at the end of this section.

| SYMBOL                | PARAMETER           | TEST CONDITION                                               | MIN   | TYP  | MAX   | UNIT<br>V       |  |

|-----------------------|---------------------|--------------------------------------------------------------|-------|------|-------|-----------------|--|

| V <sub>IN</sub>       | Input voltage       |                                                              | 4.5   |      | 5.5   |                 |  |

| V <sub>INripple</sub> | Input ripple        | I <sub>OUT</sub> = 6 A                                       |       |      | 75    | mV              |  |

| V <sub>OUT</sub>      | Output voltage      | $I_{OUT} = 0 \text{ A}, \text{ V}_{IN} = 5 \text{ V}$        | 1.764 | 1.8  | 1.836 | V               |  |

|                       | Line regulation     | V <sub>IN</sub> = 4.5 A to 5.5 V                             |       | 0.5% |       |                 |  |

|                       | Load regulation     | $I_{OUT} = 0 A to 6 A$                                       |       | 0.5% |       |                 |  |

| V <sub>RIPPLE</sub>   | Output ripple       | I <sub>OUT</sub> = 6 A                                       |       |      | 36    | mV              |  |

| V <sub>TRANS</sub>    | Transient deviation | $I_{OUT} = 1 \text{ A to 5 A}, I_{OUT} = 5 \text{ A to 1 A}$ |       | 50   |       |                 |  |

| I <sub>OUT</sub>      | Output current      | V <sub>IN</sub> = 4.5 V to 5.5 V                             | 0     |      | 6     | А               |  |

| F <sub>SW</sub>       | Switching frequency |                                                              |       | 600  |       | kHz             |  |

|                       | Size                |                                                              |       |      | 1     | ln <sup>2</sup> |  |

#### **Design Goal Parameters**

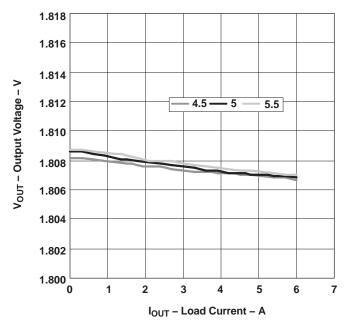

For this example, the schematic shown in Figure 23 is used. The TPS40041, with  $F_{SW}$  = 600 kHz, is selected to reduce inductor and capacitor sizes.

Figure 23. TPS40041 Sample Schematic

#### Inductor Selection

The inductor is typically sized for 30% peak-to-peak ripple current (I<sub>RIPPLE</sub>) Given this target ripple current, the required inductor size is calculated by:

$$L = \frac{V_{IN(max)} - V_{OUT}}{0.3 \times I_{OUT}} \times \frac{V_{OUT}}{V_{IN(max)}} \times \frac{1}{F_{SW}}$$

(4)

Solving with  $V_{IN(max)} = 5.5$  V, an inductor value of 1.12  $\mu$ H is obtained. A standard value of 1.0  $\mu$ H is selected, resulting in 2-A peak-peak ripple. The RMS current through the inductor is approximated by the equation:

$$I_{L(rms)} = \sqrt{\left(I_{L(avg)}\right)^{2} + \frac{1}{12}\left(I_{RIPPLE}\right)^{2}} = \sqrt{\left(I_{OUT}\right)^{2} + \frac{1}{12}\left(I_{RIPPLE}\right)^{2}}$$

(5)

Using Equation 5, the maximum RMS current in the inductor is about 6.03 A.

#### **Output Capacitor Selection (C8 & C9)**

The selection of the output capacitor is typically driven by the output load transient response requirement. Equation 6 and Equation 7 estimate the output capacitance required for a given output voltage transient deviation.

$$C_{OUT(min)} = \frac{I_{TRAN(max)}^{2} \times L}{\left(V_{IN(min)} - V_{OUT}\right) \times V_{TRAN}} \text{ when } V_{IN(min)} < 2 \times V_{OUT}$$

$$C_{OUT(min)} = \frac{I_{TRAN(max)}^{2} \times L}{\left(V_{OUT}\right) \times V_{TRAN}} \text{ when } V_{IN(min)} > 2 \times V_{OUT}$$

(6)

(7)

For this example, Equation 7 is used in calculating the minimum output capacitance.

Based on a 4-A load transient with a maximum 50-mV deviation, a minimum of  $178\mu$ F output of capacitance is required.

The output ripple is divided into two components. The first is the ripple voltage generated by inductor ripple current flowing through the output capacitor's capacitance, and the second is the voltage generated by the ripple current flowing in the output capacitor's ESR. The maximum allowable ESR is then determined by the maximum ripple voltage and is approximated by:

$$ESR_{MAX} = \frac{V_{RIPPLE(total)} - V_{RIPPLE(cap)}}{I_{RIPPLE}} = \frac{V_{RIPPLE(total)} - \left(\frac{I_{RIPPLE}}{C_{OUT} \times F_{SW}}\right)}{I_{RIPPLE}}$$

(8)

Based on 178  $\mu$ F of capacitance, 2-A ripple current, 600-kHz switching frequency and a design goal of 36-mV ripple voltage, we calculate a capacitive ripple component of 18.7 mV and a maximum ESR of 8.6 m $\Omega$ . Two 1206, 100- $\mu$ F, 6.3-V, X5R ceramic capacitors are selected to provide significantly less than 8.6 m $\Omega$  of ESR.

IEXAS IRUMENTS

(10)

## **Peak Current Rating of Inductor**

TEXAS RUMENTS

With output capacitance known, it is now possible to calculate the charging current during start-up and determine the minimum saturation current rating for the inductor. The start-up charging current is approximated by:

$$I_{CHARGE} = \frac{V_{OUT} \times C_{OUT}}{T_{SS}}$$

(9)

Using the TPS40041's fixed 4.5-ms soft-start time,  $C_{OUT} = 200 \ \mu\text{F}$  and  $V_{OUT} = 1.8 \ \text{V}$ ,  $I_{CHARGE}$  is found to be 80 mA. The peak current rating of the inductor is now found by:

$$L_{L(peak)} = I_{OUT(max)} + \frac{1}{2}(I_{RIPPLE}) + I_{CHARGE}$$

The inductor requirements are summarized in the table below.

#### **Inductor Requirements**

| PARAMETER                        | SYMBOL               | VALUE | UNITS |

|----------------------------------|----------------------|-------|-------|

| Inductance                       | L                    | 1.0   | μH    |

| RMS current (thermal rating)     | I <sub>L(rms)</sub>  | 6.03  | А     |

| Peak current (saturation rating) | I <sub>L(peak)</sub> | 7.08  |       |

A PG0083.102, 1.0 µH is selected for its small size, low DCR and high current handling capability.

## Input Capacitor Selection (C1 & C2)

The input voltage ripple is divided between capacitance and ESR. For this design,  $V_{RIPPLE(CAP)} = 50 \text{ mV}$  and  $V_{RIPPLE(ESR)} = 25 \text{ mV}$ . The minimum capacitance and maximum ESR are estimated by:

$$C_{IN(min)} = \frac{I_{LOAD} \times V_{OUT}}{V_{RIPPLE(cap)} \times V_{IN} \times F_{SW}}$$

(11)

$$ESR_{MAX} = \frac{V_{RIPPLE(ESR)}}{I_{LOAD} + \frac{1}{2}(I_{RIPPLE})}$$

(12)

For this design,  $C_{IN} > 80 \ \mu$ F and ESR < 3.5 m $\Omega$ . The RMS current in the input capacitors is estimated by:

$$I_{\text{RMS(cin)}} = I_{\text{IN(rms)}} - I_{\text{IN(avg)}} = \sqrt{\left[ \left( I_{\text{OUT}} \right)^2 + \frac{1}{12} \left( I_{\text{RIPPLE}} \right)^2 \right]} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} - \frac{V_{\text{OUT}} \times I_{\text{OUT}}}{V_{\text{IN}}}$$

(13)

With  $V_{IN} = V_{IN(max)}$ , the input capacitors must support a ripple current of 1.56 A<sub>RMS</sub>. Two 1206, 100- $\mu$ F, X5R ceramic capacitors with about 5-m $\Omega$  ESR and a 2-A RMS current rating are selected. It is important to check the dc bias voltage derating curves to ensure the capacitors provide sufficient capacitance at the working voltage.

## MOSFET Switch Selection (Q1 & Q2)

The switching losses for the upper switch MOSFET are estimated by:

$$P_{G1SW} = \frac{1}{2} \times V_{IN} \times I_{OUT} \times (T_{RISE} + T_{FALL}) \times F_{SW} = V_{IN} \times I_{OUT} \times \frac{Q_{GS2\_Q1} + Q_{GD\_Q1}}{\frac{V_{DD} - V_{TH}}{R_{DRIVE}}} \times F_{SW}$$

(14)

For this design, switching losses are higher at low input voltage due to the lower gate drive current. Designing for 1 W of total losses in both MOSFETS and 20% of the total MOSFET losses in switching losses, we can estimate our maximum gate-to-drain charge for the design at:

$$Q_{GS2_Q1} + Q_{GD_Q1} < \frac{P_{G1SW}}{V_{IN} \times I_{OUT}} \times \frac{V_{DD} - V_t}{R_{DRIVE}} \times \frac{1}{F_{SW}}$$

(15)

For a low-gate threshold MOSFET, and the TPS40041's 5  $\Omega$  and 3  $\Omega$  drive resistances, we estimate a maximum  $Q_{GS2}+Q_{GD}$  of 10.8 nC.

The conduction losses in the upper switch MOSFET are estimated by the RMS current through the MOSFET times its  $R_{DS(on)}$ :

$$P_{\text{CON}\_Q1} = D \times \left[ \left( I_{\text{OUT}} \right)^2 + \frac{1}{12} \left( I_{\text{RIPPLE}} \right)^2 \right] \times R_{\text{DS(on)}} = \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times I_{\text{L(rms)}}^2 \times R_{\text{DS(on}\_Q1)}$$

(16)

Estimating about 30% of total MOSFET losses to be high-side conduction losses, the maximum  $R_{DS(on)}$  of the high-side MOSFET can be estimated by:

$$R_{DS(on_Q1)} = \frac{P_{CON_Q1}}{I_{L(rms)}^2 \times \frac{V_{OUT}}{V_{IN}}}$$

(17)

For this design, with I<sub>L RMS</sub> = 6 A<sub>RMS</sub> and 4.5 V to 1.8 V,  $R_{DS(on Q1)}$  is < 19.5 m $\Omega$  for the upper switch MOSFET.

Estimating 50% of total MOSFET losses are in the SR as conduction losses, repeat equation 14. Then calculate the maximum  $R_{DS(on)}$  of the SR by the equation:

$$R_{DS(on_Q2)} = \frac{P_{CON_Q2}}{I_{L(rms)}^2 \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

(18)

RUMENTS

For this design I<sub>L\_RMS</sub> = 6 A at 5.5 V to 1.8 V R<sub>DS(on\_Q2)</sub> < 19.6 m $\Omega$ . The table below summarizes the MOSFET requirements.

#### **MOSFET Requirements**

| PARAMETER                         | SYMBOL                                  | VALUE | UNITS |

|-----------------------------------|-----------------------------------------|-------|-------|

| High-side FET R <sub>DS(on)</sub> | R <sub>DS(on_Q1)</sub>                  | 19.5  | mΩ    |

| High-side FET turn-on charge      | Q <sub>GS2_Q1</sub> +Q <sub>GD_Q1</sub> | 10.8  | nC    |

| Low-side FET R <sub>DS(on)</sub>  | R <sub>DS(on_Q2)</sub>                  | 19.6  | mΩ    |

IRF7910 has an  $R_{DSON(max)}$  of 15 m $\Omega$  at 4.5-V gate drive,  $Q_{GD}$  of 6.2 nC, and  $Q_{GS2}$  of 2 nC.

## **Bootstrap Capacitor (C7)**

To ensure proper charging of the upper switch MOSFET gate, limit the ripple voltage on the bootstrap capacitor to < 5% of the minimum gate drive voltage of 3.0 V.

$$C_{BOOST} = \frac{20 \times Q_{GS_Q1}}{V_{IN(min)}}$$

(19)

Based on the IRF7910 MOSFET with a maximum total gate charge of 26 nC, calculate a minimum of 116 nF of capacitance. The next higher standard value of 220 nF is selected.

#### VDD Bypass Capacitor (C6)

Select a  $1.0-\mu$ F ceramic bypass capacitor for VDD.

#### VDD Filter Resistor (R7)

An optional resistor in series with VDD helps filter switching noise from the device. Driving the two IRF7910 MOSFETs, with a typical total  $Q_G$  of 17 nC each, we calculate a maximum  $I_{DD}$  current of 22 mA. The result of equation 19, leads to selecting a 1- $\Omega$  resistor, and limits the voltage drop across this resistor to less than 25 mV.

$$R_{VDD} < \frac{V_{RVDD(max)}}{I_{DD}} = \frac{25 \text{ mV}}{2 \text{ mA} + (Q_{G_Q1} + Q_{G_Q2})F_{SW}}$$

(20)

#### Short Circuit Protection (R2)

The TPS40040/1 use the forward drop across the upper switch MOSFET during the ON time to measure the inductor current. The voltage drop across the high-side MOSFET is given by:

$$V_{\rm CS} = I_{\rm L(peak)} \times R_{\rm DS(on_Q1)}$$

<sup>(21)</sup>

When  $V_{IN} = 4.5$  V to 5.5 V,  $I_{L_{PEAK}} = 7.2$ A. Using the IRF7910 MOSFET, we calculate the peak voltage drop to be 108 mV. The TPS40041's internal 3100-ppm temperature coefficient helps compensate for the MOSFET's  $R_{DS(on)}$  temperature coefficient. For this design, select the short circuit protection voltage threshold of 180 mV by selecting R2 = OPEN.

#### Feedback Loop Design

To design feedback circuit, a small signal average modeling technique is employed. Further information on this technique may be found in the references.

## Modeling the Power Stage

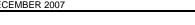

The peak-to-peak ramp voltage given in the Electrical Specification table allows the modulator gain to be calculated as:

$$A_{MOD} = \frac{V_{IN}}{V_{RAMP(p-p)}}$$

(22)

For this design, a modulator gain of 7.3 (17.3 dB) is calculated.

The LC filter applies a double pole at the resonance frequency:

$$F_{RES} = \frac{1}{2 \times \pi \times \sqrt{L \times C}}$$

(23)

For this design, the resonance frequency is about 11.3 kHz. Below this frequency, the power stage has the dc gain of 17.3 dB and above this frequency the power stage gain drops off at -40 dB per decade. The ESR zero is approximated by:

$$F_{ESR} = \frac{1}{2 \times \pi \times C_{OUT} \times R_{ESR}}$$

(24)

For  $C_{OUT} = 2 \times 100 \mu$ F and  $R_{ESR} = 2.5 m\Omega$   $F_{ESR} = 318$  kHz. This is greater than 1/5th the switching frequency and outside the scope of the error amplifier design. The gain of the power stage would change to -20 dB per decade above  $F_{ESR}$ . The straight line approximation the power stage gain is approximated in Figure 24.

Frequency (Log Scale)

## Feedback Divider (R4, R5 & R8)

Select R8 be between 10 k $\Omega$  and 100 k $\Omega$ . For this design, select 20 k $\Omega$ . Next, R5 is selected to produce the desired output voltage when V<sub>FB</sub> = 0.600 V using the following formula.

R5 in paralell with R4 =

$$\frac{V_{FB} \times R8}{V_{OUT} - V_{FB}}$$

(25)

VFB = 0.600 V and R8 = 20 k $\Omega$  for VOUT = 1.8 V, R5 = 10 k $\Omega$ . If the calculated value is not a standard resistor, select a slightly higher resistor value and add R4 in parallel to reduce the parallel combination of R4 and R5 to produce desired output voltage.

(26)

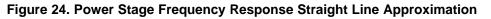

#### **Error Amplifier Pole-Zero Selection**

Place two zeros at 80% and 125% of the resonance frequency to keep the actual resonance frequency between the two zeros over the L and C tolerance. For  $F_{RES} = 11.3$  kHz,  $F_{Z1} = 9.0$  kHz and  $F_{Z2} = 14$  kHz. Selecting the cross-over frequency ( $F_{CO}$ ) of the control loop between 3 times the LC filter resonance and 1/5th the switching frequency. For most applications 1/10th the switching frequency provides a good balance between ease of design and fast transient response.

If

$$F_{ESR} < F_{CO}$$

;  $F_{P1} = F_{CO}$  and  $F_{P2} = 2x F_{CO}$ .

If  $F_{ESR} > 2x F_{CO}$ ;  $F_{P1} = F_{CO}$  and  $F_{P2} = 4x F_{CO}$ .

For this design with  $F_{SW}$  = 600 kHz,  $F_{RES}$  = 11.3 kHz and  $F_{ESR}$  = 318 kHz.

$F_{CO}$  = 60 kHz and since  $F_{ESR}$  > 2x  $F_{CO}$ ,  $F_{P1}$  =  $F_{CO}$  and  $F_{P2}$  = 4x  $F_{CO}$ .

Since  $F_{CO} < F_{ESR}$  the power stage gain at the desired cross-over can be approximated by:

$$A_{PS(fcc)} = A_{MOD} - 40 \times LOG\left(\frac{F_{CO}}{F_{RES}}\right)$$

$A_{PS}(F_{CO}) = -11.7 \text{ dB}$ , so the error amplifier gain between the two poles should be  $10^{(11.7/20)} = 3.84$ .

If the error amplifier gain is greater than 0 dB at  $F_{SW}$ , the converter can achieve a stable bi-modal operation with duty cycles alternating between two stable values, and the output regulated with a output ripple component at  $F_{SW}$ . To prevent this effect, check  $F_{P2}$  by the equation:

$$F_{P2(max)} = \frac{F_{SW}}{A_{MID(band)}}$$

(27)

Since  $F_{P2} > F_{P2(max)}$ , it is possible for this control loop to obtain bi-modal operation. To prevent this bi-modal operation, reduce  $F_{CO}$  and re-calculate  $A_{PC}(F_{CO})$ ,  $F_{P1}$ , and  $F_{P2(max)}$ .

Now,  $F_{CO} = 50$  kHz,  $A_{MID-BAND} = 2.67$ ,  $F_{P1} = 50$  kHz and  $F_{P2} = 200$  kHz.

The table below summarizes the error amplifier compensation network design criteria.

#### **Error Amplifier Compensation Network**

| PARAMETER             | SYMBOL                | VALUE | UNITS |

|-----------------------|-----------------------|-------|-------|

| First zero frequency  | F <sub>Z1</sub>       | 9     | kHz   |

| Second zero frequency | F <sub>Z2</sub>       | 14    |       |

| First pole frequency  | F <sub>P1</sub>       | 50    |       |

| Second pole frequency | F <sub>P2</sub>       | 200   |       |

| Mid-band gain         | A <sub>MID-BAND</sub> | 2.67  | V/V   |

## Feedback Components (R3, R6, C3, C4, C5)

Approximate C5 with the formula:

4

$$C5 = \frac{1}{2 \times \pi \times R8 \times F_{Z2}}$$

(28)

C5 = 560 pF (closest standard capacitor value to calculated 568 pF) and approximate R6 with the formula:

$$R6 = \frac{1}{2 \times \pi \times C5 \times F_{P1}}$$

(29)

R6 = 4.75 k $\Omega$  (closest standard resistor value to calculated 4.74 k $\Omega$ ) Calculate R3 by the formula:

$$R3 = \frac{A_{\text{MID(band)}} \times (R6 \times R8)}{R6 + R8}$$

(30)

With  $A_{\text{MID}\_\text{BAND}} = 3.84$ , R6 = 4.75 k $\Omega$  and R8 = 20 k $\Omega$ , R3 = 14.7 k $\Omega$  (closest standard resistor value to calculated 14.7 k $\Omega$ ) Calculate C3 and C4 by the equations:

$$C4 = \frac{1}{2 \times \pi \times R3 \times F_{Z1}}$$

$$C3 = \frac{1}{2 \times \pi \times R3 \times F_{P2}}$$

(31)

(32)

For R3 = 14.7 k $\Omega$ , C3 = 47 pF (closest standard value to 45 pF) C4 = 1200 pF (closest standard value to 1.2 nF) Error Amplifier straight line approximation transfer function looks like Figure 25.

Frequency (Log Scale)

Figure 25. Error Amplifier Frequency Response Straight Line Approximation

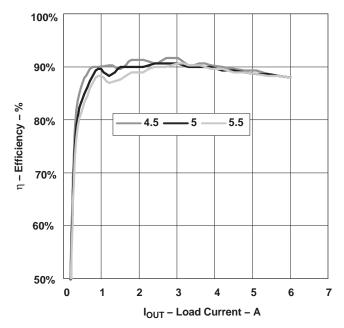

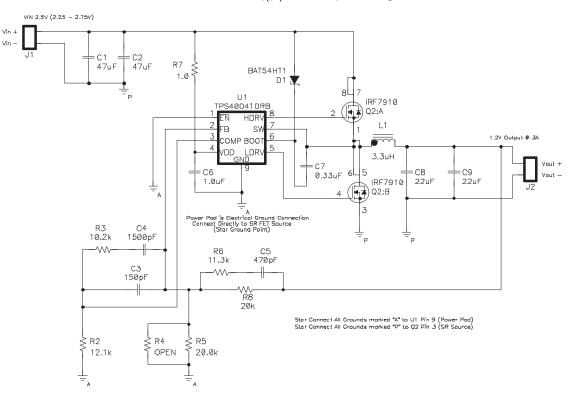

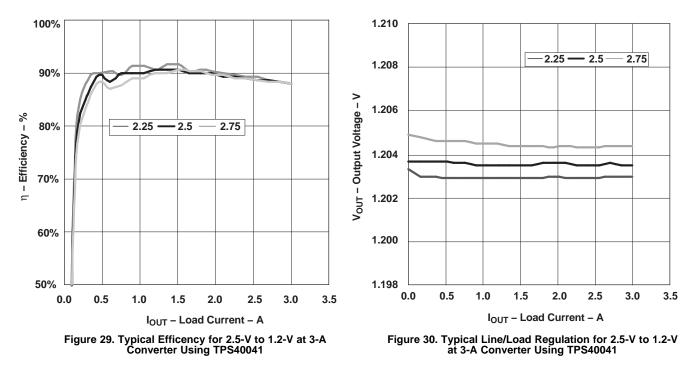

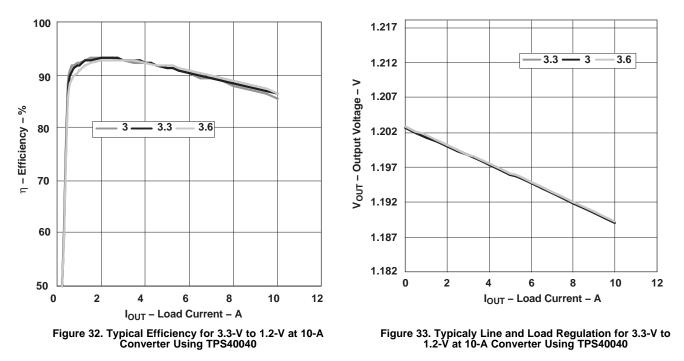

Figure 26. Typical Efficency for 5-V to 1.8-V at 6-A Converter Using TPS40041

Figure 27. Typical Line/Load Regulation for 5-V to 1.8-V at 6-A Converter Using TPS40041

## List of Materials

| REF | QTY                                                                                | DESCRIPTION                                                           | MFR         | PART NUMBER    |  |  |  |  |  |

|-----|------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------|----------------|--|--|--|--|--|

| C1  | 1                                                                                  | Capacitor, ceramic, 6.3 V, X5R, 20%, 100 µF, 1210                     | TDK         | C325X5R0J107M  |  |  |  |  |  |

| C2  | 1                                                                                  | Capacitor, ceramic, 6.3 V, X5R, 20%, 100 µF, 1210                     | TDK         | C3225X5R0J107M |  |  |  |  |  |

| C3  | 1                                                                                  | Capacitor, ceramic, 50 V, X7R, 20%, 270pF, 0402                       | TDK         | C1005C01H271M  |  |  |  |  |  |

| C4  | 1                                                                                  | Capacitor, ceramic, 50 V, X7R, 20%, 1500 pF, 0402                     | TDK         | C1005X7R1H152M |  |  |  |  |  |

| C5  | 1                                                                                  | Capacitor, ceramic, 50 V, X7R, 20%, 560 pF, 0402                      | TDK         | C1005X7R1H561M |  |  |  |  |  |

| C6  | 1                                                                                  | Capacitor, ceramic, 6.3 V, X5R, 20%, 1.0 µF, 0402                     | TDK         | C1005X7R0J105M |  |  |  |  |  |

| C7  | 1                                                                                  | Capacitor, ceramic, 6.3 V, X5R, 20%, 0.22 µF, 0402                    | TDK         | C1005X7R0J224M |  |  |  |  |  |

| C8  | 1                                                                                  | Capacitor, ceramic, 6.3 V, X5R, 20%, 100 µF, 1210                     | TDK         | C3225X5R0J107M |  |  |  |  |  |

| C9  | 1                                                                                  | Capacitor, ceramic, 6.3 V, X5R, 20%, 100 µF, 1210                     | TDK         | C3225X5R0J107M |  |  |  |  |  |

| L1  | 1                                                                                  | Inductor, SMT, 1.0 μH, 12 A, 6.6 mΩ, ED1514, 0.268 x 0.268            | Pulse       | PG0083.102     |  |  |  |  |  |

| Q2  | 1                                                                                  | MOSFET, dual N-channel, 20 V, 6.6 A, 29 m $\Omega$ , 1.0 $\mu$ H, SO8 | IR          | IRF7311        |  |  |  |  |  |

| R2  | 1                                                                                  | Resistor, chip, 1/16 W, %, IRF7910, 0402                              | Std         | Std            |  |  |  |  |  |

| R3  | 1                                                                                  | Resistor, chip, 1/16 W, 1%, OPEN, 0402                                | Std         | Std            |  |  |  |  |  |

| R4  | 1                                                                                  | Resistor, chip, 1/16 W, 1%, 11.8 kΩ, 0402                             | Std         | Std            |  |  |  |  |  |

| R5  | 1                                                                                  | Resistor, chip, 1/16 W, 1%, OPEN, 0402                                | Std         | Std            |  |  |  |  |  |

| R6  | 1                                                                                  | Resistor, chip, k 1/1 W, 1%, 10.0 kΩ, 0402                            | Std         | Std            |  |  |  |  |  |

| R7  | 1                                                                                  | Resistor, chip, k, 1/16 W, 1%, 5.62 kΩ, 0402                          | Std         | Std            |  |  |  |  |  |

| R8  | 1                                                                                  | Resistor, chip, k 1/16 W, 1%, 20 kΩ, 0402                             | Std         | Std            |  |  |  |  |  |

| U1  | 1 Device, Low Voltage DC to DC Synchronous Buck Controller,<br>TPS40041DRB, SON-8P |                                                                       | TPS40041DRB | ТІ             |  |  |  |  |  |

|     |                                                                                    | Active High Enable Circuit                                            |             |                |  |  |  |  |  |

| R1  | 1                                                                                  | Resistor, chip, 100 kΩ, 1/16 W, 1%, 100 kΩ, 0402                      | Std         | Std            |  |  |  |  |  |

| Q1  | Mosfet N-channel VDS 60 V RDS 2 0 JD 115 mA                                        |                                                                       | 2N7002W-7   | Diodes Inc     |  |  |  |  |  |

## **Definition of Symbols**

| SYMBOL                  | DESCRIPTION                                                                                                                              |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IN(max)</sub>    | Maximum operating input voltage                                                                                                          |

| V <sub>IN(min)</sub>    | Minimum operating input voltage                                                                                                          |

| VINRIPPLE               | Peak-to-peak ac ripple voltage on V <sub>IN</sub>                                                                                        |

| V <sub>OUT</sub>        | Target output voltage                                                                                                                    |

| VOUTRIPPLE              | Peak-to-peak ac ripple voltage on V <sub>OUT</sub>                                                                                       |

| I <sub>OUT(max)</sub>   | Maximum operating load current                                                                                                           |

| I <sub>RIPPLE</sub>     | Peak-to-peak ripple current through the output filter inductor                                                                           |

| I <sub>L_PEAK</sub>     | Peak ripple current through the output filter inductor                                                                                   |

| I <sub>L_RMS</sub>      | Root mean squared current through the output filter inductor                                                                             |

| I <sub>RMS_CIN</sub>    | Root mean squared current in input capacitor                                                                                             |

| F <sub>SW</sub>         | Switching frequency                                                                                                                      |

| F <sub>CO</sub>         | Desired control loop cross-over frequency                                                                                                |

| A <sub>MOD</sub>        | Low frequency gain of the pulse width modulator                                                                                          |

| V <sub>CONTROL</sub>    | PWM control voltage (error amplifier output voltage - V <sub>COMP</sub> )                                                                |

| F <sub>RES</sub>        | L-C filter resonant frequency                                                                                                            |

| F <sub>ESR</sub>        | Output capacitors' ESR zero frequency                                                                                                    |

| F <sub>P1</sub>         | First pole frequency in error amplifier compensation                                                                                     |

| F <sub>P2</sub>         | Second pole frequency in error amplifier compensation                                                                                    |

| F <sub>Z1</sub>         | First zero frequency in error amplifier compensation                                                                                     |

| F <sub>Z2</sub>         | Second pole frequency in error amplifier compensation                                                                                    |

| Q <sub>G1_Q1</sub>      | Total gate charge of upper switch MOSFET                                                                                                 |

| Q <sub>G2_Q2</sub>      | Total gate charge of synchronous rectifier MOSFET                                                                                        |

| R <sub>DS(on_Q1)</sub>  | "ON" drain-to-source resistance of upper switch MOSFET                                                                                   |

| R <sub>DS(on_Q2)</sub>  | "ON" drain-to-source resistance of synchronous rectifier MOSEFT                                                                          |

| P <sub>CON_Q1</sub>     | Conduction losses in upper switch MOSFET                                                                                                 |

| P <sub>SW_Q1</sub>      | Switching losses in upper switch MOSFET                                                                                                  |

| P <sub>CON_Q2</sub>     | Conduction losses in synchronous rectifier MOSFET                                                                                        |

| Q <sub>GD_Q1</sub>      | Gate-to-drain charge of upper switch MOSFET                                                                                              |

| Q <sub>GS2_Q1</sub>     | Post threshold gate-to-source charge of the upper switch MOSFET. (Estimate from $Q_G$ vs. $V_{GS}$ if not provided in MOSFET data sheet) |

| V <sub>FB</sub>         | Internal reference voltage as measured on FB pin.                                                                                        |

| V <sub>RAMP_slope</sub> | Slope of internal PWM ramp                                                                                                               |

| A <sub>PS(Fco)</sub>    | V <sub>COMP</sub> to V <sub>OUT</sub> gain at desired loop cross-over frequency. (dB)                                                    |

| A <sub>MID-BAND</sub>   | V <sub>OUT</sub> to V <sub>COMP</sub> gain at desired loop cross-over frequency (V/V)                                                    |

## TEXAS INSTRUMENTS www.ti.com

## Example 2. A 2.5-V to 1.2-V DC-to-DC Converter Using a TPS40041