# ADI公司欢迎 Hittite Microwave公司

所附文档的内容未做任何更改

# 本页空白

#### 产品特性

• 高速模式(12位/8位)

四通道模式: F<sub>Smax</sub> = 160/250 MSPS 双通道模式: F<sub>Smax</sub> = 320/500 MSPS 单通道模式: F<sub>Smax</sub> = 640/1000 MSPS

SNR: 70 dB; SFDR: 60/75 dB [1](12位单通道模式)

- HMCAD1511和HMCAD1510中描述的8位模式

- 精密模式(14位)

四通道高达105 MSPS

SNR: 74 dB; SFDR: 83 dB(70 MHz)

SNR: 72.5 dB; SFDR: 78 dB(140 MHz)

- 带瞬时开关功能的集成式交叉点开关

- 内部低抖动可编程时钟分频器

- 超低功耗

490 mW(包括I/O, 12位、640 MSPS)

- 从休眠状态启动的时间: 0.5 μs, 从掉电状态启动的时间: 15 μs

- 内部基准电压源电路, 无需外部元件

- 粗调和精调增益控制

- 针对每个ADC提供数字增益精调能力

- 内部失调校正

- 电源电压: 1.8 V

- 控制接口引脚具有1.7 3.6 V CMOS逻辑电压

- 串行LVDS输出 提供12、14、16和双通道8位模式

- 7x7mm48QFN封装

- [1] 包括/不包括交错杂散

#### 典型应用

- 精密示波器

- 频谱分析仪

- 分集接收机

- 高端超声

- 通信测试

- 无损检测

#### 引脚兼容器件

HMCAD1520与HMCAD1511和HMCAD1510引脚兼容,并且可配置为像HMCAD1511和HMCAD1510一样工作,后面两款器件的功能和性能参见HMCAD1511和HMCAD1510数据手册。

#### 功能框图 84 9 [4] 4 [4] 4 [4] [4] [4] ကြ [2] AVDD AVDD 36 CROSS POINT SWITCHES (MUX ARRAY) Clock 1/2/4/8 CLKP CSN CLKN **SDATA** ADC3 SPI SCLK OVDD 33 Inter-AVDD2 RESETN (32 AVSS2 PD(31 6 Digital Digital Gain Digital Digital DVDD DVDD $\overline{2}$ (30 DVSS DVSS 8 29 PLL DP1A 9 DN4B LVDS LVDS -(28 DN1A DP4B 10)--(27 LVDS LVDS LVDS DP1B DN4A 11)--(26 DN1B DP4A 12 - 25 PACKAGE LCLKN FCLKP FCLPN AVSS 功能框图

#### 概述

HMCAD1520是一款多功能、高性能、低功耗模数转换器(ADC),采用交错式高速模式来提升采样速率。集成式交叉点开关激活用户选择的输入。

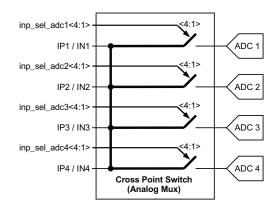

在单通道模式下,可以选择四个输入中的一个作为单个ADC通道的有效输入。在双通道模式下,可以为每一个ADC通 道选择四个输入中的任意两个。在四通道模式和精密模式下,任意输入都可分配至任意ADC通道。

内部低抖动可编程时钟分频器使得针对所有工作模式采用单个时钟源成为可能。

HMCAD1520基于专利结构,采用内部基准电压源电路、串行控制接口和串行LVDS输出数据。数据和帧同步时钟用于接收机的数据捕捉。针对每一个ADC可单独设置内部数字精调增益,以便校准增益误差。

通过串行控制接口(SPI),可向ADC施加各种模式和配置设置。每个通道都可独立关断,并且输出数据格式可通过此接口选择。可使用单个外部引脚设置全芯片空闲模式。寄存器设置决定了此引脚的确切功能。

HMCAD1520设计为可轻松与多个供应商提供的现场可编程门阵列(FPGA)实现接口。

## 电气规格

#### 直流规格

除非另有说明,AVDD = DVDD = OVDD =  $1.8\,\mathrm{V}$ , $F_s$  =  $160\,\mathrm{MSPS}$ ,四通道12位高速模式,50%时钟占空比, $-1\,\mathrm{dBFS}$  70 MHz 输入信号, $1x/0\,\mathrm{dB}$ 数字增益(精调和粗调)。

| 参数                  | 描述                      | 最小值                  | 典型值                  | 最大值                                            | 单位  |

|---------------------|-------------------------|----------------------|----------------------|------------------------------------------------|-----|

| 直流精度                |                         |                      |                      |                                                |     |

| 无失码                 |                         | 保证                   |                      |                                                |     |

| 失调                  | 内部数字失调校正后的失调误差          |                      | 1                    |                                                | LSB |

| G <sub>abs</sub>    | 增益误差                    |                      |                      | ±6                                             | %FS |

| G <sub>rel</sub>    | 通道间增益匹配。<br>最差情况下为±3 Σ值 |                      | ±0.5                 |                                                | %FS |

| DNL                 | 微分非线性                   |                      | ±0.2                 |                                                | LSB |

| INL                 | 积分非线性                   |                      | ±0.6                 |                                                | LSB |

| V <sub>CM,out</sub> | 共模电压输出                  |                      | V <sub>AVDD</sub> /2 |                                                |     |

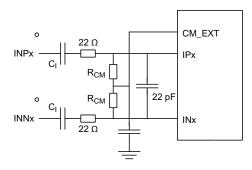

| 模拟输入                |                         |                      |                      |                                                |     |

| V <sub>CM,in</sub>  | 模拟输入共模电压                | V <sub>CM</sub> -0.1 |                      | V <sub>CM</sub> +0.2                           | V   |

| FSR                 | 差分输入电压满量程范围             |                      | 2                    |                                                | Vpp |

| C <sub>in,Q</sub>   | 差分输入电容,四通道模式            |                      | 5                    |                                                | pF  |

| C <sub>in,D</sub>   | 差分输入电容,双通道模式            |                      | 7                    |                                                | pF  |

| C <sub>in,S</sub>   | 差分输入电容,单通道模式            |                      | 11                   |                                                | pF  |

| 电源                  |                         |                      |                      |                                                |     |

| V <sub>AVDD</sub>   | 模拟电源电压                  | 1.7                  | 1.8                  | 2                                              | V   |

| V <sub>DVDD</sub>   | 数字和输出驱动器电源电压            | 1.7                  | 1.8                  | 2                                              | V   |

| V <sub>OVDD</sub>   | 数字CMOS输入电源电压            | 1.7                  | 1.8                  | 3.6                                            | V   |

|                     |                         |                      |                      | <u>.                                      </u> |     |

| T <sub>A</sub>      | 自由空气下的工作温度              | -40                  |                      | 85                                             | °C  |

## 交流规格 - 高速模式

除非另有说明, AVDD = DVDD = OVDD = 1.8 V, 50%时钟占空比, -1 dBFS 70 MHz输入信号, 增益 = 1X, 12位输出, RSDS输出数据电平。

| 参数                    | 描述                                                                                                                                    | 最小值 | 典型值  | 最大值 | 单位   |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| 性能                    |                                                                                                                                       |     | ,    |     | ,    |

| SNR                   | 信噪比,不包括交错杂散                                                                                                                           |     |      |     |      |

|                       | 单通道模式,F <sub>s</sub> = 640 MSPS                                                                                                       |     | 70   |     | dBFS |

|                       | 双通道模式,F <sub>s</sub> = 320 MSPS                                                                                                       |     | 70   |     | dBFS |

|                       | 四通道模式,F <sub>s</sub> = 160 MSPS                                                                                                       |     | 70   |     | dBFS |

| SINAD                 | 信纳比,包括交错杂散                                                                                                                            |     |      |     |      |

|                       | 单通道模式,F <sub>s</sub> = 640 MSPS                                                                                                       |     | 58   |     | dBFS |

|                       | 双通道模式,F <sub>s</sub> = 320 MSPS                                                                                                       |     | 58   |     | dBFS |

|                       | 四通道模式,F <sub>s</sub> = 160 MSPS                                                                                                       |     | 58   |     | dBFS |

| SINAD <sub>excl</sub> | 信纳比,不包括交错杂散                                                                                                                           |     |      |     |      |

|                       | 单通道模式,F <sub>s</sub> = 640 MSPS                                                                                                       |     | 67   |     | dBFS |

|                       | 双通道模式,F <sub>s</sub> = 320 MSPS                                                                                                       |     | 68   |     | dBFS |

|                       | 四通道模式,F <sub>s</sub> = 160 MSPS                                                                                                       |     | 68   |     | dBFS |

| SFDR <sub>incl</sub>  | 无杂散动态范围,包括交错杂散                                                                                                                        |     |      |     |      |

|                       | 单通道模式,F <sub>s</sub> = 640 MSPS                                                                                                       |     | 60   |     | dBc  |

|                       | 双通道模式,F <sub>s</sub> = 320 MSPS                                                                                                       |     | 60   |     | dBc  |

|                       | 四通道模式,F <sub>s</sub> = 160 MSPS                                                                                                       |     | 60   |     | dBc  |

| SFDR <sub>excl</sub>  | 无杂散动态范围,不包括交错杂散                                                                                                                       |     |      |     |      |

|                       | 单通道模式,F <sub>s</sub> = 640 MSPS                                                                                                       |     | 75   |     | dBc  |

|                       | 双通道模式,F <sub>s</sub> = 320 MSPS                                                                                                       |     | 77   |     | dBc  |

|                       | 四通道模式,F <sub>s</sub> = 160 MSPS                                                                                                       |     | 78   |     | dBc  |

| HD2/3                 | 最差HD2/HD3                                                                                                                             |     |      |     |      |

|                       | 单通道模式,F <sub>S</sub> = 640 MSPS                                                                                                       |     | 75   |     | dBc  |

|                       | 双通道模式,F <sub>S</sub> = 320 MSPS                                                                                                       |     | 77   |     | dBc  |

|                       | 四通道模式,F <sub>s</sub> = 160 MSPS                                                                                                       |     | 78   |     | dBc  |

| ENOB                  | 有效位数                                                                                                                                  |     |      |     |      |

|                       | 单通道模式,F <sub>s</sub> = 640 MSPS                                                                                                       |     | 10.8 |     | 位    |

|                       | 双通道模式,F <sub>s</sub> = 320 MSPS                                                                                                       |     | 11.0 |     | 位    |

|                       | 四通道模式,F <sub>s</sub> = 160 MSPS                                                                                                       |     | 11.0 |     | 位    |

| X <sub>tlk,HS2</sub>  | 串扰,双通道模式。信号施加于一个通道(F <sub>INo</sub> )。<br>以满量程在另一个通道(F <sub>IN1</sub> )上进行测量。<br>F <sub>IN1</sub> = 71 MHz,F <sub>IN0</sub> = 70 MHz。 |     | 70   |     | dBc  |

| $X_{tlk,HS4}$         | 串扰,四通道模式。信号施加于一个通道(F <sub>INO</sub> )。<br>以满量程在另一个通道(F <sub>IN1</sub> )上进行测量。<br>F <sub>IN1</sub> = 71 MHz,F <sub>INO</sub> = 70 MHz。 |     | 70   |     | dBc  |

| 电源                    | 单通道: F <sub>s</sub> = 640 MSPS; 双通道: F <sub>s</sub> = 320 MSPS;<br>四通道: F <sub>s</sub> = 160 MSPS。                                    |     |      |     |      |

| I <sub>AVDD</sub>     | 模拟电源电流                                                                                                                                |     | 190  |     | mA   |

| I <sub>DVDD</sub>     | 数字和输出驱动器电源电流                                                                                                                          |     | 82   |     | mA   |

| P <sub>AVDD</sub>     | 模拟电源                                                                                                                                  |     | 342  |     | mW   |

#### 交流规格 - 高速模式

除非另有说明,AVDD = DVDD = OVDD = 1.8 V, 50%时钟占空比, -1 dBFS 70 MHz输入信号,增益 = 1X, 12位输出, RSDS输出数据电平。

| 参数                     | 描述                              | 最小值            | 典型值 | 最大值          | 单位   |

|------------------------|---------------------------------|----------------|-----|--------------|------|

| P <sub>DVDD</sub>      | 数字电源                            |                | 148 |              | mW   |

| P <sub>TOT</sub>       | 总功耗                             |                | 490 |              | mW   |

| P <sub>PD</sub>        | 掉电模式功耗                          |                | 15  |              | μW   |

| P <sub>SLP</sub>       | 深度休眠模式功耗                        |                | 66  |              | mW   |

| P <sub>SLPCH</sub>     | 所有通道都处于休眠模式(轻度休眠)的功耗            |                | 121 |              | mW   |

| P <sub>SLPCH_SAV</sub> | 每关闭一个通道节省的功耗                    |                | 92  |              | mW   |

| 模拟输入                   |                                 |                |     |              |      |

| FPBW                   | 全功率带宽                           |                | 700 |              | MHz  |

| 时钟输入                   |                                 |                |     |              |      |

| F <sub>Smax</sub>      | 不同模式下的最大转换速率:<br>单通道/双通道<br>四通道 | 640/320<br>160 |     |              | MSPS |

| F <sub>Smin</sub>      | 不同模式下的最小转换速率:<br>单通道/双通道<br>四通道 |                |     | 120/60<br>30 | MSPS |

## 交流规格 - 精密模式

除非另有说明, AVDD = DVDD = OVDD = 1.8 V, FS = 105 MHz, 50%时钟占空比, -1 dBFS 70 MHz输入信号, 增益 = 1X, 双通道8位输出, RSDS输出数据电平。

| 参数    | 描述                                                   | 最小值 | 典型值  | 最大值 | 单位   |

|-------|------------------------------------------------------|-----|------|-----|------|

| 性能    |                                                      |     |      |     |      |

| SNR   | 信噪比                                                  |     |      |     |      |

|       | F <sub>s</sub> = 80 MSPS                             |     | 75   |     | dBFS |

|       | F <sub>s</sub> = 105 MSPS                            |     | 74   |     | dBFS |

|       | $F_s = 105 \text{ MSPS}, F_{in} = 105 \text{ MSPS}$  |     | 72.5 |     | dBFS |

| SINAD | 信纳比                                                  |     |      |     |      |

|       | F <sub>s</sub> = 80 MSPS                             |     | 73   |     | dBFS |

|       | F <sub>s</sub> = 105 MSPS                            |     | 72.5 |     | dBFS |

|       | $F_s = 105 \text{ MSPS}, F_{in} = 105 \text{ MSPS}$  |     | 71   |     | dBFS |

| SFDR  | 无杂散动态范围                                              |     |      |     |      |

|       | F <sub>s</sub> = 80 MSPS                             |     | 85   |     | dBc  |

|       | F <sub>s</sub> = 105 MSPS                            |     | 83   |     | dBc  |

|       | F <sub>s</sub> = 105 MSPS,F <sub>in</sub> = 105 MSPS |     | 78   |     | dBc  |

| HD2   | 二阶谐波杂散                                               |     |      |     |      |

|       | F <sub>S</sub> = 80 MSPS                             |     | 90   |     | dBc  |

|       | F <sub>S</sub> = 105 MSPS                            |     | 90   |     | dBc  |

|       | $F_s = 105 \text{ MSPS}, F_{in} = 105 \text{ MSPS}$  |     | 80   |     | dBc  |

| HD3   | 三阶谐波杂散                                               |     |      |     |      |

## 交流规格 - 精密模式

除非另有说明,AVDD = DVDD = OVDD = 1.8 V,FS = 105 MHz,50%时钟占空比,-1 dBFS 70 MHz输入信号,增益 = 1X,双通道8位输出,RSDS输出数据电平。

| 参数                     | 描述                                                                                                                          | 最小值 | 典型值  | 最大值 | 单位   |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                        | F <sub>s</sub> = 80 MSPS                                                                                                    |     | 85   |     | dBc  |

|                        | F <sub>s</sub> = 105 MSPS                                                                                                   |     | 83   |     | dBc  |

|                        | F <sub>s</sub> = 105 MSPS, F <sub>in</sub> = 105 MSPS                                                                       |     | 78   |     | dBc  |

| ENOB                   | 有效位数                                                                                                                        |     |      |     |      |

|                        | F <sub>S</sub> = 80 MSPS                                                                                                    |     | 11.8 |     | 位    |

|                        | F <sub>s</sub> = 105 MSPS                                                                                                   |     | 11.8 |     | 位    |

|                        | F <sub>s</sub> = 105 MSPS, F <sub>in</sub> = 105 MSPS                                                                       |     | 11.5 |     | 位    |

| X <sub>tlk</sub>       | 串扰。信号施加于一个通道(F <sub>IN0</sub> )。以满量程在另一个通道(F <sub>IN1</sub> )上<br>进行测量。F <sub>IN1</sub> = 71 MHz,F <sub>IN0</sub> = 70 MHz。 |     | 70   |     | dBc  |

| 电源                     |                                                                                                                             |     | •    | •   |      |

| I <sub>AVDD</sub>      | 模拟电源电流                                                                                                                      |     | 229  |     | mA   |

| I <sub>DVDD</sub>      | 数字和输出驱动器电源电流                                                                                                                |     | 106  |     | mA   |

| P <sub>AVDD</sub>      | 模拟电源                                                                                                                        |     | 412  |     | mW   |

| P <sub>DVDD</sub>      | 数字电源                                                                                                                        |     | 191  |     | mW   |

| P <sub>TOT</sub>       | 总功耗                                                                                                                         |     | 603  |     | mW   |

| P <sub>PD</sub>        | 掉电模式功耗                                                                                                                      |     | 15   |     | μW   |

| P <sub>SLP</sub>       | 深度休眠模式功耗                                                                                                                    |     | 66   |     | mW   |

| P <sub>SLPCH</sub>     | 所有通道都处于休眠模式(轻度休眠)的功耗                                                                                                        |     | 131  |     | mW   |

| P <sub>SLPCH_SAV</sub> | 每关闭一个通道节省的功耗                                                                                                                |     | 118  |     | mW   |

| 模拟输入                   |                                                                                                                             |     |      |     |      |

| FPBW                   | 全功率带宽                                                                                                                       |     | 700  |     | MHz  |

| 时钟输入                   |                                                                                                                             |     |      | •   | •    |

| F <sub>Smax</sub>      | 最大转换速率                                                                                                                      | 105 |      |     | MSPS |

| F <sub>Smin</sub>      | 最小转换速率                                                                                                                      |     |      | 15  | MSPS |

|                        | 1                                                                                                                           |     |      |     |      |

#### 数字和开关规格

除非另有说明, AVDD = DVDD = OVDD = 1.8 V, RSDS输出数据电平。

| 参数                   | 描述                            | 最小值   | 典型值               | 最大值                    | 单位   |

|----------------------|-------------------------------|-------|-------------------|------------------------|------|

| 时钟输入                 |                               |       |                   |                        |      |

| 直流                   | 占空比,高速模式                      | 40    |                   | 60                     | 高电平% |

| 直流                   | 占空比,精密模式                      | 30    |                   | 70                     | 高电平% |

| 顺从电压                 | 支持LVDS,最高700 Mbps             | LVPEC | L、正弦波、CM          | IOS, LVDS              |      |

| V <sub>CK,sine</sub> | 差分输入电压摆幅,正弦波时钟输入              | 1500  |                   |                        | mVpp |

| V <sub>CK,CMOS</sub> | 电压输入范围CMOS(CLKN接地)            |       | V <sub>OVDD</sub> |                        |      |

| V <sub>CM,CK</sub>   | 输入共模电压。<br>将电压保持在地和OVDD电压范围内。 | 0.3   |                   | V <sub>OVDD</sub> -0.3 | V    |

| C <sub>ck</sub>      | 差分输入电容                        |       | 3                 |                        | pF   |

| 逻辑输入(CMOS)           |                               |       |                   |                        |      |

## 数字和开关规格

除非另有说明, AVDD = DVDD = OVDD = 1.8 V, RSDS输出数据电平。

| 参数                   | 描述                                               | 最小值                      | 典型值                      | 最大值                      | 单位       |

|----------------------|--------------------------------------------------|--------------------------|--------------------------|--------------------------|----------|

| V <sub>HI</sub>      | 高电平输入电压。 V <sub>OVDD</sub> ≥ 3.0 V               | 2                        |                          |                          | V        |

| V <sub>HI</sub>      | 高电平输入电压。 V <sub>OVDD</sub> = 1.7 V - 3.0 V       | 0.8 ·V <sub>OVDD</sub>   |                          |                          | V        |

| V <sub>LI</sub>      | 低电平输入电压。 V <sub>OVDD</sub> ≥ 3.0 V               | 0                        |                          | 0.8                      | V        |

| V <sub>LI</sub>      | 低电平输入电压。 V <sub>OVDD</sub> = 1.7 V - 3.0 V       | 0                        |                          | 0.2 · V <sub>OVDD</sub>  | V        |

| I <sub>HI</sub>      | 高电平输入漏电流                                         |                          |                          | +/-10                    | μΑ       |

| I <sub>u</sub>       | 低电平输入漏电流                                         |                          |                          | +/-10                    | μΑ       |

| C <sub>i</sub>       | 输入电容                                             |                          | 3                        |                          | pF       |

| 数据输出                 |                                                  |                          |                          |                          |          |

| 顺从电压                 |                                                  |                          | LVDS / RSDS              |                          |          |

| V <sub>out</sub>     | 差分输出电压,LVDS                                      |                          | 350                      |                          | mV       |

| V <sub>out</sub>     | 差分输出电压,RSDS                                      |                          | 150                      |                          | mV       |

| V <sub>CM</sub>      | 输出共模电压                                           |                          | 1.2                      |                          | V        |

| 输出编码                 | 默认/可选                                            | 偏移                       | 5二进制/二进制剂                | <b>小码</b>                |          |

| 时序特性                 |                                                  | •                        |                          |                          | •        |

| t <sub>A,HS</sub>    | 孔径延迟,高速模式                                        |                          | 1.5                      |                          | ns       |

| t <sub>A,PM</sub>    | 孔径延迟,精密模式                                        |                          | 1.4                      |                          | ns       |

| t <sub>j,HS</sub>    | 孔径抖动,jitter_ctrl<7:0>中的所有位设为"1",高速模式             |                          | 120                      |                          | fsrms    |

| t <sub>j,HS</sub>    | 孔径抖动,jitter_ctrl<7:0>中的一位设为"1",高速模式              |                          | 160                      |                          | fsrms    |

| t <sub>j,PM</sub>    | 孔径抖动,jitter_ctrl<7:0>中的所有位设为"1",精密模式             |                          | 75                       |                          | fsrms    |

| t <sub>j,PM</sub>    | 孔径抖动,jitter_ctrl<7:0>中的一位设为"1",精密模式              |                          | 130                      |                          | fsrms    |

| T <sub>skew</sub>    | ADC通道间的时序偏斜,高速模式                                 |                          | 2.5                      |                          | psrms    |

| T <sub>su</sub>      | 从掉电模式和深度休眠模式到活动模式的启动时间(单位为μs)。<br>详情参见"时钟频率1"部分。 |                          | 15                       |                          | μs       |

| T <sub>SLPCH</sub>   | 从休眠通道模式到活动模式的启动时间                                |                          | 0.5                      |                          | μs       |

| T <sub>OVR</sub>     | 超范围                                              |                          | 1                        |                          | 时钟周期     |

| T <sub>LATPM</sub>   | 流水线延迟,精密模式                                       |                          | 15                       |                          | 时钟周期     |

| T <sub>LATHSMQ</sub> | 流水线延迟,四通道高速模式                                    |                          | 32                       |                          | 时钟周期     |

| T <sub>LATHSMD</sub> | 流水线延迟,双通道高速模式                                    |                          | 64                       |                          | 时钟周期     |

| T <sub>LATHSMS</sub> | 流水线延迟,单通道高速模式                                    |                          | 128                      |                          | 时钟周期     |

| LVDS输出时序             | 特性                                               | 1                        |                          |                          |          |

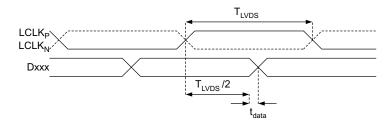

| t <sub>data</sub>    | LCLK至数据延迟时间(不包括可编程相移)                            |                          | 50                       |                          | ps       |

| T <sub>PROP</sub>    | 时钟传播延迟。                                          | 6*T <sub>LVDS</sub> +2.2 | 7*T <sub>LVDS</sub> +3.5 | 7*T <sub>LVDS</sub> +5.0 | ns       |

|                      | LVDS位时钟占空比                                       | 45                       | -                        | 55                       | % LCLK周期 |

|                      | 帧时钟周期间抖动                                         |                          |                          | 2.5                      | % LCLK周期 |

| T <sub>EDGE</sub>    | 数据上升和下降时间20%至80%                                 |                          | 0.7                      |                          | ns       |

| T <sub>CLKEDGE</sub> | 时钟上升和下降时间20%至80%                                 |                          | 0.7                      |                          | ns       |

#### 绝对最大额定值

对引脚施加的电压超过表1所示额定值可能会永久损坏电路。

#### 表1: 最大电压额定值

| 引脚          | 基准引脚        | 额定值           |

|-------------|-------------|---------------|

| AVDD        | AVSS        | -0.3 V至+2.3 V |

| DVDD        | DVSS        | -0.3 V至+2.3 V |

| OVDD        | AVSS        | -0.3 V至+3.9 V |

| AVSS / DVSS | DVSS / AVSS | -0.3 V至+0.3 V |

| 模拟输入和输出     | AVSS        | -0.3 V至+2.3 V |

| CLKx        | AVSS        | -0.3 V至+3.9 V |

| LVDS输出      | DVSS        | -0.3 V至+2.3 V |

| 数字输入        | DVSS        | -0.3 V至+3.9 V |

#### 表2: 所示为最大外部温度额定值

| 工作温度      | -40至+85°C  |

|-----------|------------|

| 存储温度      | -60至+150°C |

| 最高结温      | 110°C      |

| 热阻(Rth)   | 29°C/W     |

| 焊接温度曲线评定  | J- STD-020 |

| ESD灵敏度HBM | 1C类        |

| ESD灵敏度CDM | Ⅲ类         |

## 静电敏感器件,请遵守操作规范

注意,超出上述绝对最大额定值可能会导致器件永久性损坏。这只是额定最值,并不能以这些条件或者在任何其他超出本技术规范操作章节中所示规格的条件下,推断器件能否正常工作。长期在绝对最大额定值条件下工作会影响器件的可靠性。

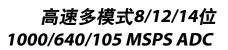

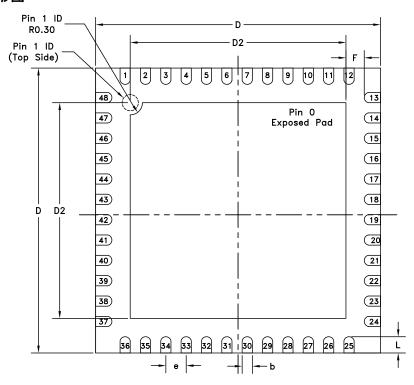

图1: 引脚图

## 表3: 引脚描述

| 引脚名称   | 描述                                          | 引脚编号  | 引脚数 |

|--------|---------------------------------------------|-------|-----|

| AVDD   | 模拟电源,1.8 V                                  | 1, 36 | 2   |

| CSN    | 片选使能。低电平有效                                  | 2     | 1   |

| SDATA  | 串行数据输入                                      | 3     | 1   |

| SCLK   | 串行时钟输入                                      | 4     | 1   |

| RESETN | 复位SPI接口。低电平有效                               | 5     | 1   |

| PD     | 掉电输入。<br>施加电源后激活,以便正确初始化ADC。<br>或者使用SPI掉电特性 | 6     | 1   |

| DVDD   | 数字和I/O电源, 1.8 V                             | 7, 30 | 2   |

| DVSS   | 数字地                                         | 8, 29 | 2   |

| DP1A   | LVDS通道1A,正输出                                | 9     | 1   |

| DN1A   | LVDS通道1A,负输出                                | 10    | 1   |

| DP1B   | LVDS通道1B,正输出                                | 11    | 1   |

| DN1B   | LVDS通道1B,负输出                                | 12    | 1   |

| DP2A   | LVDS通道2A,正输出                                | 13    | 1   |

| DN2A   | LVDS通道2A,负输出                                | 14    | 1   |

| DP2B   | LVDS通道2B,正输出                                | 15    | 1   |

| DN2B   | LVDS通道2B,负输出                                | 16    | 1   |

## 表3: 引脚描述

| 引脚名称  | 描述              | 引脚编号       | 引脚数 |

|-------|-----------------|------------|-----|

| LCLKP | LVDS位时钟,正输出     | 17         | 1   |

| LCLKN | LVDS位时钟,负输出     | 18         | 1   |

| FCLKP | LVDS帧时钟(1X),正输出 | 19         | 1   |

| FCLKN | LVDS帧时钟(1X),负输出 | 20         | 1   |

| DP3A  | LVDS通道3A,正输出    | 21         | 1   |

| DN3A  | LVDS通道3A,负输出    | 22         | 1   |

| DP3B  | LVDS通道3B,正输出    | 23         | 1   |

| DN3B  | LVDS通道3B,负输出    | 24         | 1   |

| DP4A  | LVDS通道4A,正输出    | 25         | 1   |

| DN4A  | LVDS通道4A,负输出    | 26         | 1   |

| DP4B  | LVDS通道4B,正输出    | 27         | 1   |

| DN4B  | LVDS通道4B,负输出    | 28         | 1   |

| AVSS2 | 模拟地域2           | 31         | 1   |

| AVDD2 | 模拟电源域2, 1.8 V   | 32         | 1   |

| OVDD  | 数字CMOS输入电源电压    | 33         | 1   |

| CLKN  | 负差分输入时钟。        | 34         | 1   |

| CLKP  | 正差分输入时钟         | 35         | 1   |

| IN4   | 负差分输入信号,通道4     | 37         | 1   |

| IP4   | 正差分输入信号,通道4     | 38         | 1   |

| AVSS  | 模拟地             | 39, 42, 45 | 3   |

| IN3   | 负差分输入信号,通道3     | 40         | 1   |

| IP3   | 正差分输入信号,通道3     | 41         | 1   |

| IP2   | 负差分输入信号,通道2     | 43         | 1   |

| IP2   | 正差分输入信号,通道2     | 44         | 1   |

| IN1   | 负差分输入信号,通道1     | 46         | 1   |

| IP1   | 正差分输入信号,通道1     | 47         | 1   |

| VCM   | 共模输出引脚,0.5*AVDD | 48         | 1   |

#### 动初始化

作为HMCAD1520上电序列的一部分,复位和掉电周期均须应用,以确保启动初始化正确。复位有以下两种方式:

- 1. 对RESETN引脚施加一个趋低脉冲(最短20 ns)(异步)。

- 2. 利用串行接口将rst位设为高电平。此位置1时,内部寄存器复位到默认值。rst位自复位到0。使用这种方法时,请勿对RESETN引脚施加趋低脉冲。

#### 掉电循环有以下两种方式:

- 1. 对PD引脚施加一个趋高脉冲(最短20 ns)(异步)。

- 2. 将寄存器0Fhex中的pd位先设为1(十六进制寄存器值0200), 再设为0(十六进制寄存器值0000)。

#### 寄存器初始化

要将HMCAD1520设置为精密模式,必须更改如下寄存器的默认值。建议值为:

| 地址   | 数据     | 功能                             |

|------|--------|--------------------------------|

| 0x31 | 0x0008 | 设置HMCAD1520为精密模式,<br>时钟分频器系数为1 |

| 0x53 | 0x0004 | 设置双通道8位模式的LVDS输出               |

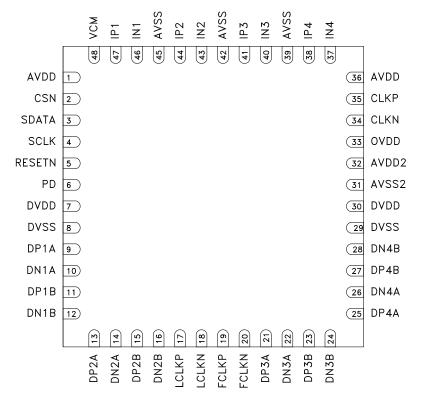

#### 串行接口

HMCAD1520配置寄存器可通过一个串行接口访问,该串行接口由SDATA(串行接口数据)、SCLK(串行接口时钟)和CSN(片选,低电平有效)引脚组成。当CSN设为低电平时,发生下列事件:

- 串行数据移入芯片

- 在SCLK的每个上升沿,锁存SDATA上存在的值

- 在SCLK的每第24个上升沿, SDATA载入寄存器

在一个有效CSN脉冲内可加载多个24位字。若在一个有效CSN脉冲期间将24位以上的数据载入SDATA,则仅保留前24位。 多余的位会被忽略。每个24位字分为两部分:

- 前8位是寄存器地址

- 其余16位是寄存器数据

支持的SCLK频率为20 MHz至数Hz。不必严格控制占空比。

#### 时序图

图2显示了串行端口接口的时序。表4解释了图2所用的时序变量。

图2: 串行端口接口时序

#### 表4: 串行端口接口时序定义

| 参数              | 描述              | 最小值 | 单位 |

|-----------------|-----------------|-----|----|

| t <sub>cs</sub> | CSN与SCLK之间的建立时间 | 8   | ns |

| t <sub>ch</sub> | CSN与SCLK之间的保持时间 | 8   | ns |

| t <sub>hi</sub> | SCLK高电平时间       | 20  | ns |

| t <sub>io</sub> | SCLK低电平时间       | 20  | ns |

| t <sub>ck</sub> | SCLK周期          | 50  | ns |

| t <sub>s</sub>  | 数据建立时间          | 5   | ns |

| t <sub>h</sub>  | 数据保持时间          | 5   | ns |

#### 时序图

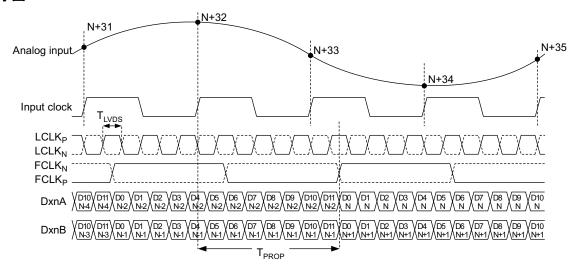

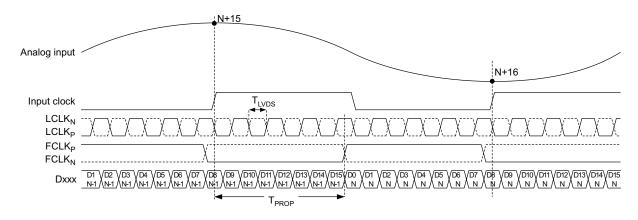

图3: 四通道 - LVDS时序12位输出

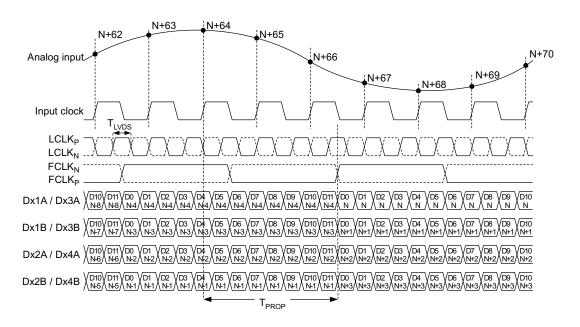

图4: 双通道 - LVDS时序12位输出

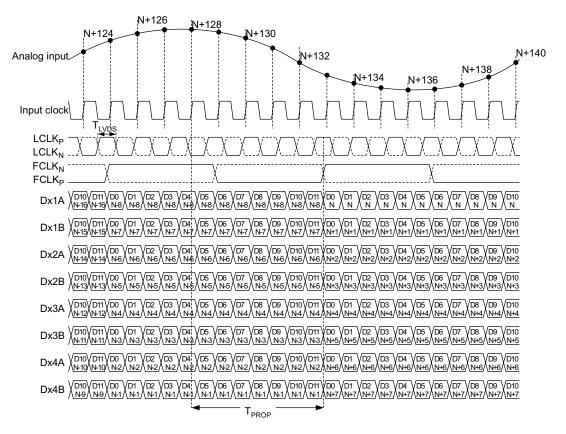

图5: 单通道 - LVDS时序12位输出

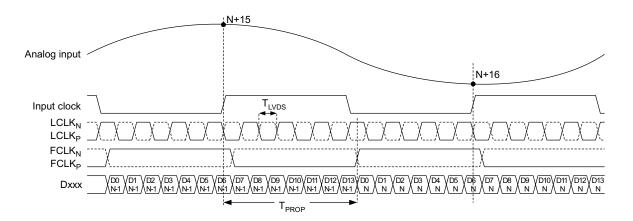

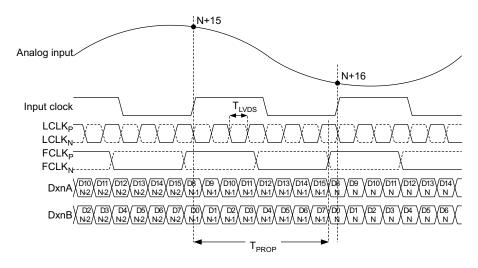

图6: 精密 - LVDS时序14位输出

图7:精密-LVDS时序16位输出

图8: 精密 - LVDS时序双通道8位输出

图9: LVDS数据时序

## 表5: 寄存器映射

| 名称                     | 描述                                        | 默认              | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

|------------------------|-------------------------------------------|-----------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| rst *                  | 自清零软件复位。                                  | 无效              |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | х  | 0x00       |

| sleep4_ch<br><4:1>     | 四通道设置的<br>特定通道休眠模式。                       | 无效              |     |     |     |     |     |     |    |    |    |    |    |    | х  | х  | х  | х  |            |

| sleep2_ch<br><2:1>     | 双通道设置的<br>特定通道休眠模式。                       | 无效              |     |     |     |     |     |     |    |    |    |    | х  | х  |    |    |    |    |            |

| sleep1_ch1             | 单通道设置的<br>特定通道休眠模式。                       | 无效              |     |     |     |     |     |     |    |    |    | х  |    |    |    |    |    |    | 0x0F       |

| sleep                  | 进入休眠模式。                                   | 无效              |     |     |     |     |     |     |    | Х  |    |    |    |    |    |    |    |    |            |

| pd                     | 进入掉电模式。                                   | 无效              |     |     |     |     |     |     | Х  |    |    |    |    |    |    |    |    |    |            |

| pd_pin_cfg<br><1:0>    | 配置PD引脚功能。                                 | PD引脚配置为<br>掉电模式 |     |     |     |     | x   | х   |    |    |    |    |    |    |    |    |    |    |            |

| ilvds_lclk<br><2:0>    | LCLKP和LCLKN引脚的<br>LVDS电流驱动编程。             | 3.5 mA驱动        |     |     |     |     |     |     |    |    |    |    |    |    |    | х  | х  | х  |            |

| ilvds_frame<br><2:0>   | FCLKP和FCLKN引脚的<br>LVDS电流驱动编程。             | 3.5 mA驱动        |     |     |     |     |     |     |    |    |    | х  | х  | х  |    |    |    |    | 0x11       |

| ilvds_dat<br><2:0>     | 输出数据引脚的<br>LVDS电流驱动编程。                    | 3.5 mA驱动        |     |     |     |     |     | х   | Х  | х  |    |    |    |    |    |    |    |    |            |

| en_lvds_<br>term       | 使能LVDS缓冲器的<br>内部端接。                       | 端接禁用            |     | х   |     |     |     |     |    |    |    |    |    |    |    |    |    |    |            |

| term_lclk<br><2:0>     | LCLKN和LCLKP缓冲器的<br>可编程端接。                 | 端接禁用            |     | 1   |     |     |     |     |    |    |    |    |    |    |    | х  | х  | х  |            |

| term_frame<br><2:0>    | FCLKN和FCLKP缓冲器的<br>可编程端接。                 | 端接禁用            |     | 1   |     |     |     |     |    |    |    | х  | х  | х  |    |    |    |    | 0x12       |

| term_dat<br><2:0>      | 输出数据缓冲器的<br>可编程端接。                        | 端接禁用            |     | 1   |     |     |     | х   | Х  | х  |    |    |    |    |    |    |    |    |            |

| invert4_ch<br><4:1>    | 四通道设置的特定通道<br>模拟输入信号交换。                   | IPx为正输入         |     |     |     |     |     |     |    |    |    |    |    |    | х  | х  | х  | х  |            |

| invert2_ch<br><2:1>    | 双通道设置的特定通道<br>模拟输入信号交换。                   | IPx为正输入         |     |     |     |     |     |     |    |    |    |    | х  | х  |    |    |    |    | 0x24       |

| invert1_ch1            | 单通道设置的特定通道<br>模拟输入信号交换。                   | IPx为正输入         |     |     |     |     |     |     |    |    |    | х  |    |    |    |    |    |    |            |

| en_ramp                | 使能输出重复的<br>满量程斜坡图形。                       | 无效              |     |     |     |     |     |     |    |    |    | х  | 0  | 0  |    |    |    |    |            |

| dual_<br>custom_pat    | 使能输出在两个规定代码<br>之间切换的模式。                   | 无效              |     |     |     |     |     |     |    |    |    | 0  | х  | 0  |    |    |    |    | 0x25       |

| single_<br>custom_pat  | 使能输出始终为<br>某个指定代码的模式。                     | 无效              |     |     |     |     |     |     |    |    |    | 0  | 0  | х  |    |    |    |    |            |

| bits_custom1<br><15:0> | 单个自定义模式码和<br>双自定义模式码的第一个<br>代码的位。<0>为LSB。 | 0x0000          | х   | х   | х   | х   | х   | х   | х  | х  | х  | х  | х  | х  | х  | x  | х  | х  | 0x26       |

## 表5: 寄存器映射

| <b>水ン:</b> 可                   | 存器映射                        |                  |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |            |

|--------------------------------|-----------------------------|------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| 名称                             | 描述                          | 默认               | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

| bits_custom2<br><15:0>         | 双自定义模式码的<br>第二个代码的位。        | 0x0000           | x   | х   | х   | х   | х   | х   | Х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | 0x27       |

| cgain4_ch1<br><3:0>            | 四通道设置中通道1的<br>可编程粗调增益。      | 1x增益             |     |     |     |     |     |     |    |    |    |    |    |    | х  | х  | х  | х  |            |

| cgain4_ch2<br><3:0>            | 四通道设置中通道2的<br>可编程粗调增益。      | 1x增益             |     |     |     |     |     |     |    |    | х  | х  | х  | х  |    |    |    |    |            |

| cgain4_ch3<br><3:0>            | 四通道设置中通道3的<br>可编程粗调增益。      | 1x增益             |     |     |     |     | х   | х   | х  | х  |    |    |    |    |    |    |    |    | 0x2A       |

| cgain4_ch4<br><3:0>            | 四通道设置中通道4的<br>可编程粗调增益。      | 1x增益             | х   | х   | х   | х   |     |     |    |    |    |    |    |    |    |    |    |    |            |

| cgain2_ch1<br><3:0>            | 双通道设置中通道1的<br>可编程粗调增益。      | 1x增益             |     |     |     |     |     |     |    |    |    |    |    |    | х  | х  | х  | х  |            |

| cgain2_ch2<br><3:0>            | 双通道设置中通道2的<br>可编程粗调增益。      | 1x增益             |     |     |     |     |     |     |    |    | х  | х  | х  | х  |    |    |    |    | 0x2B       |

| cgain1_ch1<br><3:0>            | 单通道设置中通道1的<br>可编程粗调增益。      | 1x增益             |     |     |     |     | х   | х   | Х  | х  |    |    |    |    |    |    |    |    |            |

| jitter_ctrl<br><7:0>           | 时钟抖动调整。                     | 160 fsrms        |     |     |     |     |     |     |    |    | х  | х  | х  | х  | х  | х  | х  | х  | 0x30       |

| precision_<br>mode *           | 使能四通道14位<br>精密模式。           | 无效               |     |     |     |     |     |     |    |    |    |    |    |    | х  |    |    |    |            |

| high_speed_<br>mode *<br><2:0> | 使能高速模式,<br>单通道、<br>双通道或四通道。 | 高速模式 -<br>四通道    |     |     |     |     |     |     |    |    |    |    |    |    |    | х  | х  | х  | 0x31       |

| clk_divide<br><1:0> *          | 定义时钟分频器系数:<br>1、2、4或8。      | 1分频              |     |     |     |     |     |     | Х  | Х  |    |    |    |    |    |    |    |    |            |

| coarse_<br>gain_cfg            | 配置粗调增益设置。                   | x增益使能            |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | х  | 0x33       |

| fine_gain_en                   | 启用精调增益。                     | 禁用               |     |     |     |     |     |     |    |    |    |    |    |    |    |    | Х  |    |            |

| fgain_<br>branch1<br><6:0>     | 分支1的可编程精调增益。                | 1x/0dB增益         |     |     |     |     |     |     |    |    |    | х  | х  | х  | х  | х  | х  | х  | 0:04       |

| fgain_<br>branch2<br><6:0>     | 分支2的可编程精调增益。                | 1x/0dB增益         |     | х   | х   | х   | х   | х   | Х  | х  |    |    |    |    |    |    |    |    | 0x34       |

| fgain_<br>branch3<br><6:0>     | 分支3的可编程精调增益。                | 1x/0dB增益         |     |     |     |     |     |     |    |    |    | х  | х  | х  | х  | х  | х  | х  | 0,05       |

| fgain_<br>branch4<br><6:0>     | 分支4的可编程精调增益。                | 1x/0dB增益         |     | х   | х   | х   | х   | х   | х  | х  |    |    |    |    |    |    |    |    | 0x35       |

| fgain_<br>branch5<br><6:0>     | 分支5的可编程精调增益。                | 1x/0dB增益         |     |     |     |     |     |     |    |    |    | х  | х  | х  | х  | х  | х  | х  | 0.00       |

| fgain_<br>branch6<br><6:0>     | 分支6的可编程精调增益。                | 1x/0dB增益         |     | х   | х   | х   | х   | х   | х  | х  |    |    |    |    |    |    |    |    | 0x36       |

| fgain_<br>branch7<br><6:0>     | 分支7的可编程精调增益。                | 1x/0dB增益         |     |     |     |     |     |     |    |    |    | х  | х  | х  | х  | х  | х  | х  | 0v27       |

| fgain_<br>branch8<br><6:0>     | 分支8的可编程精调增益。                | 1x/0dB增益         |     | х   | х   | х   | х   | х   | х  | х  |    |    |    |    |    |    |    |    | 0x37       |

| inp_sel_adc1<br><4:0>          | adc 1的输入选择。                 | 信号输入:<br>IP1/IN1 |     |     |     |     |     |     |    |    |    |    |    | х  | х  | х  | х  | Х  | 0~34       |

| inp_sel_adc2<br><4:0>          | adc 2的输入选择。                 | 信号输入:<br>IP2/IN2 |     |     |     | х   | х   | х   | Х  | х  |    |    |    |    |    |    |    |    | 0x3A       |

## 表5: 寄存器映射

| 名称                              | 描述                       | 默认                | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

|---------------------------------|--------------------------|-------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| inp_sel_adc3<br><4:0>           | adc 3的输入选择。              | 信号输入:<br>IP3/ IN3 |     |     |     |     |     |     |    |    |    |    |    | х  | х  | х  | х  | х  | 0::00      |

| inp_sel_adc4<br><4:0>           | adc 4的输入选择。              | 信号输入:<br>IP4/ IN4 |     |     |     | х   | х   | х   | Х  | х  |    |    |    |    |    |    |    |    | 0x3B       |

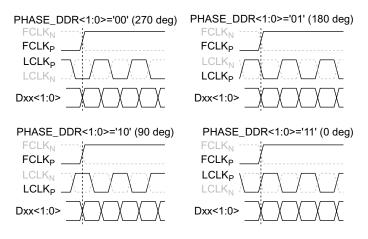

| phase_ddr<br><1:0>              | 控制LCLK输出<br>相对于数据的相位。    | 90度               |     |     |     |     |     |     |    |    |    | х  | х  |    |    |    |    |    | 0x42       |

| pat_deskew                      | 使能去偏斜模式码模式。              | 无效                |     |     |     |     |     |     |    |    |    |    |    |    |    |    | 0  | Х  | 0x45       |

| pat_sync                        | 使能同步模式码模式。               | 无效                |     |     |     |     |     |     |    |    |    |    |    |    |    |    | х  | 0  | 0x45       |

| btc_mode                        | ADC输出数据的<br>二进制补码格式。     | 直接偏移二进制           |     |     |     |     |     |     |    |    |    |    |    |    |    | х  |    |    | 0.40       |

| msb_first                       | 串行ADC输出数据<br>MSB优先送出。    | LSB优先             |     |     |     |     |     |     |    |    |    |    |    |    | х  |    |    |    | 0x46       |

| adc_curr<br><2:0>               | ADC电流调整。                 | 标称                |     |     |     |     |     |     |    |    |    |    |    |    |    | х  | х  | х  | 0450       |

| ext_vcm_bc<br><1:0>             | VCM缓冲器驱动<br>强度控制。        | 标称                |     |     |     |     |     |     |    |    |    |    | Х  | Х  |    |    |    |    | 0x50       |

| lvds_pd_<br>mode                | 控制LVDS<br>掉电模式。          | 高阻态               |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | Х  | 0x52       |

| lvds_output_<br>mode<br><2:0> * | 设置LVDS<br>输出位数。          | 12位               |     |     |     |     |     |     |    |    |    |    |    |    |    | х  | х  | х  |            |

| low_clk_<br>freq *              | 使用低时钟频率。                 | 无效                |     |     |     |     |     |     |    |    |    |    |    |    | Х  |    |    |    |            |

| lvds_<br>advance                | LVDS数据位和帧时钟<br>提前一个时钟周期。 | 无效                |     |     |     |     |     |     |    |    |    |    | 0  | х  |    |    |    |    | 0x53       |

| lvds_delay                      | LVDS数据位和帧时钟<br>延迟一个时钟周期。 | 无效                |     |     |     |     |     |     |    |    |    |    | х  | 0  |    |    |    |    |            |

| fs_cntrl<br><5:0>               | 精调ADC满量程范围。              | 0 %变化             |     |     |     |     |     |     |    |    |    |    | х  | х  | х  | х  | х  | х  | 0x55       |

| startup_ctrl<br><2:0> *         | 控制启动时间。                  | '000'             |     |     |     |     |     |     |    |    |    |    |    |    |    | х  | х  | х  | 0x56       |

不得写入未定义的寄存器地址, 否则可能引发错误行为。

对寄存器编程时,未使用的寄存器位(表格空白单元)必须设为0。

当芯片处于掉电模式时, 可写入所有寄存器。

\*写入这些寄存器时,需要执行掉电循环(参见"启动初始化"部分)。

## 寄存器描述

#### 软件复位

| 名称  | 描述           | 默认 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制 地址 |

|-----|--------------|----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---------|

| rst | 自清零软件<br>复位。 | 无效 |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | Х  | 0x00    |

rst寄存器位设为1将恢复所有内部寄存器的默认值,包括rst寄存器位本身。

#### 工作模式

| 名称                        | 描述                          | 默认            | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

|---------------------------|-----------------------------|---------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| precision_mode            | 使能四通道14位<br>精密模式。           | 无效            |     |     |     |     |     |     |    |    |    |    |    |    | х  |    |    |    |            |

| high_speed_<br>mode <2:0> | 使能高速模式,<br>单通道、<br>双通道或四通道。 | 高速模式 –<br>四通道 |     |     |     |     |     |     |    |    |    |    |    |    |    | х  | х  | х  | 0x31       |

| clk_divide<1:0>           | 定义时钟分频器系数:<br>1、2、4或8。      | 1分频           |     |     |     |     |     |     | х  | х  |    |    |    |    |    |    |    |    |            |

HMCAD1520有四种主要工作模式,由表6所示的寄存器位precision\_mode和high\_speed\_mode控制。如"启动初始化"部分所述,工作模式变更期间或之后,必须激活掉电模式以确保正常工作。所有高速模式都利用交错来实现高采样速率。四通道模式交错2个ADC分支,双通道模式交错4个ADC分支,单通道模式交错全部8个ADC分支。精密模式下不需要交错,每个ADC通道仅使用一个ADC分支。

#### 表6: 工作模式

| precision_<br>mode | hi | igh_speed_mod<br><2:0> | le | 工作模式       | 描述                                              |

|--------------------|----|------------------------|----|------------|-------------------------------------------------|

| 0                  | 0  | 0                      | 1  | 单通道12位高速模式 | 单通道,交错ADC1至ADC4                                 |

| 0                  | 0  | 1                      | 0  | 双通道12位高速模式 | 双通道,通道1交错ADC1和ADC2,<br>通道2交错ADC3和ADC4           |

| 0                  | 1  | 0                      | 0  | 四通道12位高速模式 | 四通道,通道1对应ADC1,通道2对应ADC2,<br>通道3对应ADC3,通道4对应ADC4 |

| 1                  | 0  | 0                      | 0  | 四通道14位精密模式 | 四通道,通道1对应ADC1,通道2对应ADC2,<br>通道3对应ADC3,通道4对应ADC4 |

同一时间只能激活四位中的一位。

clk\_divide<1:0>允许用户施加高于采样速率的输入时钟频率。时钟分频器对输入时钟频率进行1、2、4或8分频,分频系数由clk\_divide<1:0>寄存器定义。相对于channel\_num<2:0>值设置clk\_divide<1:0>值,便可将相同输入时钟频率用于多个通道的所有设置。例如:通道数从1增加到4时,最大采样速率降低4倍。让clk\_divide<1:0>跟随channel\_num<2:0>值变化,即从1变为4,则内部时钟分频器可降低采样速率,而无需改变输入时钟频率。

表7: 时钟分频器系数

| clk_divide<1:0> | 时钟分频器系数 | 采样速率(FS) |

|-----------------|---------|----------|

| 00(默认值)         | 1       | 输入时钟频率/1 |

| 01              | 2       | 输入时钟频率/2 |

| 10              | 4       | 输入时钟频率/4 |

| 11              | 8       | 输入时钟频率/8 |

#### 输入选择

| 名称                    | 描述          | 默认               | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

|-----------------------|-------------|------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| inp_sel_adc1<br><4:0> | adc 1的输入选择。 | 信号输入:<br>IP1/IN1 |     |     |     |     |     |     |    |    |    |    |    | х  | х  | х  | х  | 0  | 0x3A       |

| inp_sel_adc2<br><4:0> | adc 2的输入选择。 | 信号输入:<br>IP2/IN2 |     |     |     | х   | х   | х   | х  | 0  |    |    |    |    |    |    |    |    | UXSA       |

| inp_sel_adc3<br><4:0> | adc 3的输入选择。 | 信号输入:<br>IP3/IN3 |     |     |     |     |     |     |    |    |    |    |    | х  | х  | х  | х  | 0  | 0x3B       |

| inp_sel_adc4<br><4:0> | adc 4的输入选择。 | 信号输入:<br>IP4/IN4 |     |     |     | х   | х   | х   | х  | 0  |    |    |    |    |    |    |    |    | UXSD       |

每个ADC通过一个全柔性交叉点开关(由inp\_sel\_adcx设置)连接四个输入信号。在单通道模式下,可以选择四个输入中的任何一个作为单个ADC通道的有效输入。在双通道模式下,可以为每一个ADC通道选择四个输入中的任意两个。在四通道模式和精密模式下,任意输入都可分配至任意ADC通道。输入切换可以在正常工作期间进行,无需额外的操作。切换会在每个SPI命令结束时立即发生。

表8: ADC输入选择

| inp_sel_adcx<4:0> | 所选输入    |

|-------------------|---------|

| 0001 0            | IP1/IN1 |

| 0010 0            | IP2/IN2 |

| 0100 0            | IP3/IN3 |

| 1000 0            | IP4/IN4 |

| 其他                | 不使用     |

图10: ADC输入信号通过交叉点开关

#### 满量程控制

| 名称                | 描述              | 默认       | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

|-------------------|-----------------|----------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| fs_cntrl<br><5:0> | 精调ADC<br>满量程范围。 | 0%<br>变化 |     |     |     |     |     |     |    |    |    |    | Х  | Х  | х  | х  | х  | х  | 0x55       |

HMCAD1520满量程电压范围可以利用内部6位DAC(由fs\_cntrl寄存器控制)进行调整。寄存器值改变一步,满量程范围即调整大约0.3%。因此,最大调整范围为±10%。表9显示了寄存器设置与满量程范围的对应关系。注意,满量程范围调整值是近似值。不过,DAC可保证单调性。

满量程控制和可编程增益特性有两大不同:

- 1. 满量程控制功能是模拟功能,而可编程增益则是数字功能。

- 2. 可编程增益功能的增益步进粗略得多,范围比满量程控制功能要大。

#### 表9: 寄存器值和对应的满量程范围变化

| fs_cntrl<5:0> | 满量程范围调整 |

|---------------|---------|

| 111111        | 9.7 %   |

| 111110        | 9.4 %   |

|               |         |

| 100001        | 0.3 %   |

| 100000        | 0%      |

| 011111        | -0.3 %  |

|               |         |

| 000001        | -9,7%   |

| 000000        | -10,0%  |

#### 电流控制

| 名称                  | 描述                | 默认 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

|---------------------|-------------------|----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| adc_curr<br><2:0>   | ADC电流<br>调整。      | 标称 |     |     |     |     |     |     |    |    |    |    |    |    |    | Х  | х  | х  |            |

| ext_vcm_bc<br><1:0> | VCM缓冲器<br>驱动强度控制。 | 标称 |     |     |     |     |     |     |    |    |    |    | Х  | Х  |    |    |    |    | 0x50       |

有两个寄存器会影响性能和功耗。

adc\_curr寄存器可调整ADC内核的电流消耗。标称设置时保证性能。降低adc\_curr值可实现更低的功耗,参见表10。 对性能的影响取决于ADC采样速率。

表10: ADC电流控制设置

| adc_curr<2:0> | ADC内核电流 |

|---------------|---------|

| 100           | -40%    |

| 101           | -30%    |

| 110           | -20%    |

| 111           | -10%    |

| 000(默认值)      | 标称      |

| 001           | 不使用     |

| 010           | 不使用     |

| 011           | 不使用     |

ext\_vcm\_bc寄存器控制缓冲器的驱动强度,其提供VCM引脚电压。如果不使用此引脚,可以断开缓冲器。如果从VCM引脚汲取电流,则可提高驱动强度以使此引脚电压保持正确电平。

表11: 外部共模电压缓冲器驱动强度

| ext_vcm_bc<1:0> | VCM缓冲器驱动强度[μA]<br>VCM引脚流入/流出最大电流,<br>电压变化小于20 mV。 |

|-----------------|---------------------------------------------------|

| 00              | 关(VCM浮空)                                          |

| 01(默认值)         | ±20                                               |

| 10              | ±400                                              |

| 11              | ±700                                              |

#### 启动和时钟抖动控制

| 名称                    | 描述     | 默认           | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

|-----------------------|--------|--------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| startup_ctrl<br><2:0> | 控制启动时间 | '000'        |     |     |     |     |     |     |    |    |    |    |    |    |    | Х  | х  | х  | 0x56       |

| jitter_ctrl<br><7:0>  | 时钟抖动调整 | 160<br>fsrms |     |     |     |     |     |     |    |    | х  | х  | х  | Х  | х  | х  | х  | х  | 0x30       |

为了优化启动时间,提供了一个用于设置启动时间(单位为时钟周期)的寄存器。某些内部电路的启动时间与时钟频率无关。 默认计数器值支持最大时钟频率(采样速率)时的启动时间。因此,时钟频率较低时,启动时间会延长。将此寄存器的值 设为最接近的较高时钟频率会降低内部计数器的计数值,以便更好地适应实际启动时间,从而缩短启动时间。从掉电和 休眠模式启动的时间由此寄存器设置更改。如果使用时钟分频器(设为非1值),必须将输入时钟频率除以分频器系数以 得出正确的时钟频率范围(参见表7)。

## 表12: 启动时间控制设置

|                       | 精密模式             |                 |              |  |  |  |  |  |  |  |

|-----------------------|------------------|-----------------|--------------|--|--|--|--|--|--|--|

| startup_<br>ctrl<2:0> | 时钟频率<br>范围[MSPS] | 启动延迟<br>[时钟周期数] | 启动延迟<br>[μs] |  |  |  |  |  |  |  |

| 100                   | 80 - 125         | 1536            | 12.3 - 19.2  |  |  |  |  |  |  |  |

| 000                   | 50 - 80          | 992             | 12.4 - 19.8  |  |  |  |  |  |  |  |

| 001                   | 32,5 - 50        | 640             | 12.8 - 19.7  |  |  |  |  |  |  |  |

| 010                   | 20 - 32,5        | 420             | 12.9 - 21    |  |  |  |  |  |  |  |

| 011                   | 15 - 20          | 260             | 13 - 17.3    |  |  |  |  |  |  |  |

| 其他                    | 不使用              | -               | -            |  |  |  |  |  |  |  |

|                       | 四通道 - 高速         |                 |              |  |  |  |  |  |  |

|-----------------------|------------------|-----------------|--------------|--|--|--|--|--|--|

| startup_<br>ctrl<2:0> | 时钟频率<br>范围[MSPS] | 启动延迟<br>[时钟周期数] | 启动延迟<br>[μs] |  |  |  |  |  |  |

| 100                   | 160 - 250        | 3072            | 12.3 – 19.2  |  |  |  |  |  |  |

| 000                   | 100 - 160        | 1984            | 12.4 - 19.8  |  |  |  |  |  |  |

| 001                   | 65 - 100         | 1280            | 12.8 - 19.7  |  |  |  |  |  |  |

| 010                   | 40 - 65          | 840             | 12.9 - 21    |  |  |  |  |  |  |

| 011                   | 30 - 40          | 520             | 13 - 17.3    |  |  |  |  |  |  |

| 其他                    | 不使用              | -               | -            |  |  |  |  |  |  |

| 四通道 - 高速              |                  |                 |              |  |  |  |  |  |

|-----------------------|------------------|-----------------|--------------|--|--|--|--|--|

| startup_<br>ctrl<2:0> | 时钟频率<br>范围[MSPS] | 启动延迟<br>[时钟周期数] | 启动延迟<br>[μs] |  |  |  |  |  |

| 100                   | 320 - 500        | 6144            | 12.3 – 19.2  |  |  |  |  |  |

| 000                   | 200 - 320        | 3968            | 12.4 - 19.8  |  |  |  |  |  |

| 001                   | 130 – 200        | 2560            | 12.8 - 19.7  |  |  |  |  |  |

| 010                   | 80 - 130         | 1680            | 12.9 - 21    |  |  |  |  |  |

| 011                   | 60 – 80          | 1040            | 13 - 17.3    |  |  |  |  |  |

| 其他                    | 不使用              | -               | -            |  |  |  |  |  |

|                       | 单通道 - 高速         |                 |              |  |  |  |  |  |  |

|-----------------------|------------------|-----------------|--------------|--|--|--|--|--|--|

| startup_<br>ctrl<2:0> | 时钟频率<br>范围[MSPS] | 启动延迟<br>[时钟周期数] | 启动延迟<br>[μs] |  |  |  |  |  |  |

| 100                   | 640 - 1000       | 12288           | 12.3 – 19.2  |  |  |  |  |  |  |

| 000                   | 400 - 640        | 7936            | 12.4 - 19.8  |  |  |  |  |  |  |

| 001                   | 260 - 400        | 5120            | 12.8 - 19.7  |  |  |  |  |  |  |

| 010                   | 160 - 260        | 3360            | 12.9 - 21    |  |  |  |  |  |  |

| 011                   | 120 - 160        | 2080            | 13 - 17.3    |  |  |  |  |  |  |

| 其他                    | 不使用              | -               | -            |  |  |  |  |  |  |

jitter\_ctrl<7:0>允许用户实现功耗与时钟抖动的平衡。如果寄存器的所有位都为0,则时钟信号停止。时钟抖动取决于jitter\_ctrl<7:0>寄存器中设为1的位数。哪些位设为1不影响结果。

## 表13: 时钟抖动性能

| jitter_ctrl<7:0>中<br>1的位数 | 时钟抖动性能 - 精密模式<br>[fsrms] | 时钟抖动性能 - 高速模式<br>[fsrms] | 模块功耗[mA] |

|---------------------------|--------------------------|--------------------------|----------|

| 1                         | 130                      | 160                      | 1        |

| 2                         | 100                      | 150                      | 2        |

| 3                         | 92                       | 136                      | 3        |

| 4                         | 85                       | 130                      | 4        |

| 5                         | 82                       | 126                      | 5        |

| 6                         | 80                       | 124                      | 6        |

| 7                         | 77                       | 122                      | 7        |

| 8                         | 75                       | 120                      | 8        |

| 0                         | 时钟停止                     | 时钟停止                     |          |

#### LVDS输出配置和控制

| 名称                         | 描述                       | 默认          | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制 地址 |

|----------------------------|--------------------------|-------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---------|

| lvds_output_<br>mode <2:0> | 设置LVDS输出位数。              | 12位         |     |     |     |     |     |     |    |    |    |    |    |    |    | х  | Х  | х  |         |

| low_clk_freq               | 使用低时钟频率。                 | 无效          |     |     |     |     |     |     |    |    |    |    |    |    | х  |    |    |    |         |

| lvds_<br>advance           | LVDS数据位和帧时钟<br>提前一个时钟周期。 | 无效          |     |     |     |     |     |     |    |    |    |    | 0  | х  |    |    |    |    | 0x53    |

| lvds_delay                 | LVDS数据位和帧时钟<br>延迟一个时钟周期。 | 无效          |     |     |     |     |     |     |    |    |    |    | х  | 0  |    |    |    |    |         |

| phase_<br>ddr<1:0>         | 控制LCLK输出<br>相对于数据的相位。    | 90度         |     |     |     |     |     |     |    |    |    | Х  | х  |    |    |    |    |    | 0x42    |

| btc_mode                   | ADC输出数据的<br>二进制补码格式。     | 直接偏移<br>二进制 |     |     |     |     |     |     |    |    |    |    |    |    |    | х  |    |    | 0x46    |

| msb_first                  | 串行ADC输出数据<br>MSB优先送出。    | LSB优先       |     |     |     |     |     |     |    |    |    |    |    |    | х  |    |    |    | UX40    |

HMCAD1520串行LVDS输出有四种不同模式,通过寄存器lvds\_output\_mode进行选择,如表14所示。如"启动初始化"部分所述,输出位数变更期间或之后,必须激活掉电模式以确保正常工作。

## 表14: LVDS输出位数

| lvds_output_mode <2:0> | 位数  | 注释                             |

|------------------------|-----|--------------------------------|

| 000                    | 8位  | 8位模式,最高1 GSPS(参见HMCAD1511数据手册) |

| 001                    | 12位 | 高速模式推荐设置(默认)                   |

| 101                    | 14位 | 最高70 MSPS的推荐设置(精密模式)           |

| 011                    | 16位 |                                |

| 100                    | 双8位 | 超过70 MSPS的推荐设置(精密模式)           |

| 其他                     | 不使用 |                                |

12位LVDS模式是所有工作模式的默认设置。若要使用另一种LVDS模式,必须相应地更改lvds\_output\_mode寄存器设置。使用8位LVDS模式时,LSB会被截断,数据输出具有8位分辨率。详情参见HMCAD1511和HMCAD1510数据手册。 选择14或16位LVDS输出模式时,输出数据为13位左对齐字,LSB侧用0填充。不同的高速模式使用表15所定义的LVDS输出。

## 表15: 高速模式和使用的LVDS输出

| 高速模式/通道 | 使用的LVDS输出                       |

|---------|---------------------------------|

| 单通道     | D1A、D1B、D2A、D2B、D3A、D3B、D4A、D4B |

| 双通道,通道1 | D1A、D1B、D2A、D2B                 |

| 双通道,通道2 | D3A、D3B、D4A、D4B                 |

| 四通道,通道1 | D1A、D1B                         |

| 四通道,通道2 | D2A、D2B                         |

| 四通道,通道3 | D3A、D3B                         |

| 四通道,通道4 | D4A、D4B                         |

对于14位精密模式,应使用14、16或双8位LVDS模式。若使用默认12位LVDS模式,数据输出会被截断为12位。若使用16位LVDS模式,输出数据为14位左对齐字,LSB侧用00填充。如果使用双通道8位输出模式,14位数据字的8个MSB将通过LVDS A输出提供,剩余6位左对齐并填充00,通过LVDS B输出,参见表16。

表16: 精密模式和使用的LVDS输出

| 精密模式              | 使用的LVDS输出        |

|-------------------|------------------|

| 通道1 - 12、14、16位输出 | D1A(D1B掉电 – 高阻态) |

| 通道1 - 双8位输出       | D1A、D1B          |

| 通道2 - 12、14、16位输出 | D2A(D2B掉电 - 高阻态) |

| 通道2 - 双8位输出       | D2A、D2B          |

| 通道3 - 12、14、16位输出 | D3A(D3B掉电 - 高阻态) |

| 通道3 - 双8位输出       | D3A、D3B          |

| 通道4 - 12、14、16位输出 | D4A(D4B掉电 - 高阻态) |

| 通道4 - 双8位输出       | D4A、D4B          |

HMCAD1520的最大数据输出比特率为1 Gb/s。不同配置的最大采样速率参见表17。采样速率由输入时钟频率(FS)设置。LVDS输出的帧速率(即FCLK信号频率)取决于所选的模式和采样频率(FS),如表18所示。

表17: HMCAD1520不同配置的最大采样速率与输出位数

| 位数  | 单通道 – 高速<br>[MSPS] | 双通道 – 高速<br>[MSPS] | 四通道 – 高速<br>[MSPS] | 四通道 - 精密<br>[MSPS] |

|-----|--------------------|--------------------|--------------------|--------------------|

| 8   | 1000               | 500                | 250                | -                  |

| 12  | 660                | 330                | 165                | 82.5               |

| 14  | 560                | 280                | 140                | 70                 |

| 16  | 500                | 250                | 125                | 62.5               |

| 双8位 | -                  | -                  | -                  | 125                |

表18: 输出数据帧速率

| 工作模式   | 帧速率(FCLK频率)        |

|--------|--------------------|

| 高速、单通道 | F <sub>s</sub> /8  |

| 高速、双通道 | F <sub>s</sub> / 4 |

| 高速、四通道 | F <sub>s</sub> / 2 |

| 精密模式   | F <sub>s</sub>     |

如果在较低采样速率下使用HMCAD1520,则寄存器位low\_clk\_freq必须设为1。对于不同工作模式,何时使用此寄存器 参见表19。

表19: 寄存器位low\_clk\_freq的使用

| 工作模式   | 激活low_clk_freq的限值        |

|--------|--------------------------|

| 高速、单通道 | F <sub>s</sub> < 240 MHz |

| 高速、双通道 | F <sub>s</sub> < 120 MHz |

| 高速、四通道 | F <sub>s</sub> < 60 MHz  |

| 精密模式   | F <sub>s</sub> < 30 MHz  |

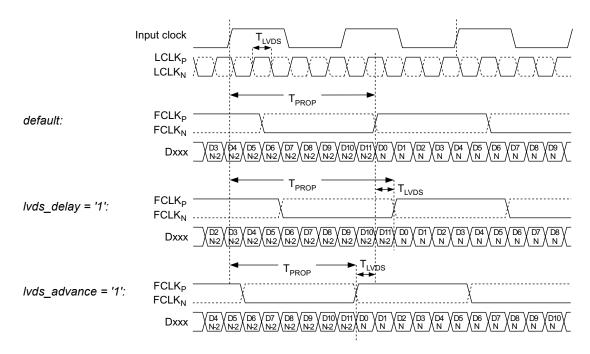

使用多个HMCAD1520时,为了缓解接收器的时序,该器件具有调整输出数据时序和帧时钟的选项。利用lvds\_delay或lvds\_advance,相对于ADC输入时钟的传播延迟可以前移或后移一个LVDS时钟周期。详情参见图11。注意,LCLK不受lvds\_delay或lvds\_advance设置影响。

图11: LVDS输出时序调整

HMCAD1520的LVDS输出接口为DDR接口。默认设置是LCLK上升沿和下降沿在交替数据窗口的中央转换。LCLK相对于输出帧时钟和数据位的相位可利用phase\_ddr<1:0>编程。LCLK相位模式如图12所示。默认时序与设置phase\_ddr<1:0>=10相同。

图12: LCLK相位编程模式

默认数据输出格式为偏移二进制。将btc\_mode位设为1以使MSB反转,可选择二进制补码模式。

默认设置下,帧的第一位(FCLKP上升沿之后)是ADC输出的LSB。设置msb\_first模式导致位序反转,MSB成为FCLKP上升沿之后输出的第一位。

#### LVDS驱动强度编程

| 名称                   | 描述                            | 默认           | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

|----------------------|-------------------------------|--------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| ilvds_lclk<br><2:0>  | LCLKP和LCLKn引脚的<br>LVDS电流驱动编程。 | 3.5 mA<br>驱动 |     |     |     |     |     |     |    |    |    |    |    |    |    | х  | х  | х  |            |

| ilvds_frame<br><2:0> | FCLKP和FCLKn引脚的<br>LVDS电流驱动编程。 | 3.5 mA<br>驱动 |     |     |     |     |     |     |    |    |    | х  | х  | х  |    |    |    |    | 0x11       |

| ilvds_dat<br><2:0>   | 输出数据引脚的<br>LVDS电流驱动编程。        | 3.5 mA<br>驱动 |     |     |     |     |     | х   | х  | х  |    |    |    |    |    |    |    |    |            |

LVDS输出驱动器提供的电流可按照表20所示进行配置。默认电流为3.5 mA,这是LVDS标准规定的值。

对于精心布局的LVDS线路,LVDS接口在RSDS(低摆幅差分信号)下具有良好的鲁棒性。与默认3.5 mA LVDS相比,使用 1.5 mA RSDS可大幅降低功耗。

ilvds\_lclk<2:0>寄存器控制LCLKP和LCLKN引脚上LVDS时钟输出的电流驱动强度。

ilvds\_frame<2:0>寄存器控制FCLKP和FCLKN引脚上帧时钟输出的电流驱动强度。

ilvds\_dat<2:0>寄存器控制D[8:1]P和D[8:1]N引脚上数据输出的电流驱动强度。

#### 表20: LCLK、FCLK和数据的LVDS输出驱动强度

| ilvds_*<2:0> | LVDS驱动强度      |

|--------------|---------------|

| 000          | 3.5 mA(默认值)   |

| 001          | 2.5 mA        |

| 101          | 1.5 mA (RSDS) |

| 011          | 0.5 mA        |

| 100          | 7.5 mA        |

| 101          | 6.5 mA        |

| 110          | 5.5 mA        |

| 111          | 4.5 mA        |

## LVDS内部端接编程

| 名称                  | 描述                        | 默认   | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制<br>地址 |

|---------------------|---------------------------|------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| en_lvds_term        | 使能LVDS缓冲器的<br>内部端接。       | 端接禁用 |     | х   |     |     |     |     |    |    |    |    |    |    |    |    |    |    |            |

| term_lclk<br><2:0>  | LCLKn和LCLKP<br>缓冲器的可编程端接。 | 端接禁用 |     | 1   |     |     |     |     |    |    |    |    |    |    |    | х  | х  | х  | 0.40       |

| term_frame<br><2:0> | FCLKn和FCLKP<br>缓冲器的可编程端接。 | 端接禁用 |     | 1   |     |     |     |     |    |    |    | х  | Х  | Х  |    |    |    |    | 0x12       |

| term_dat<br><2:0>   | 输出数据缓冲器的<br>可编程端接。        | 端接禁用 |     | 1   |     |     |     | х   | х  | х  |    |    |    |    |    |    |    |    |            |

LVDS缓冲器的片外负载可能代表一个不与PCB走线完全匹配的特性阻抗。这可能导致信号反射回LVDS输出,从而丧失完整性。使能各LVDS缓冲器的正输出与负输出之间的内部端接可以减轻这种影响。将en\_lvds\_term位设为1可选择内部端接模式。此位置1后,位时钟、帧时钟和数据缓冲器的内部端接值可利用三位组设置。表21显示了LVDS缓冲器的内部端接编程方法。所示值为典型值,对于不同器件和温度,其变化范围可达±20%。

表21: LCLK、FCLK和数据的LVDS输出内部端接

| term_*<2:0> | LVDS内部端接 |

|-------------|----------|

| 000         | 端接禁用     |

| 001         | 260 Ω    |

| 010         | 150 Ω    |

| 011         | 94 Ω     |

| 100         | 125 Ω    |

| 101         | 80 Ω     |

| 110         | 66 Ω     |

| 111         | 55 Ω     |

#### 功耗模式控制

| 名称                  | 描述                  | 默认              | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 十六进制 地址 |

|---------------------|---------------------|-----------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---------|

| sleep4_ch<br><4:1>  | 四通道设置的<br>特定通道休眠模式。 | 无效              |     |     |     |     |     |     |    |    |    |    |    |    | х  | X  | х  | х  |         |

| sleep2_ch<br><2:1>  | 双通道设置的<br>特定通道休眠模式。 | 无效              |     |     |     |     |     |     |    |    |    |    | х  | х  |    |    |    |    |         |

| sleep1_ch1          | 单通道设置的<br>特定通道休眠模式。 | 无效              |     |     |     |     |     |     |    |    |    | x  |    |    |    |    |    |    | 0x0F    |

| sleep               | 进入休眠模式。             | 无效              |     |     |     |     |     |     |    | х  |    |    |    |    |    |    |    |    |         |

| pd                  | 进入掉电模式。             | 无效              |     |     |     |     |     |     | х  |    |    |    |    |    |    |    |    |    |         |

| pd_pin_cfg<br><1:0> | 配置PD引脚功能。           | PD引脚配置为<br>掉电模式 |     |     |     |     | х   | х   |    |    |    |    |    |    |    |    |    |    |         |

| lvds_pd_<br>mode    | 控制LVDS掉电模式。         | 高阻态             |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | Х  | 0x52    |

HMCAD1520器件具有多种功耗管理模式,从启动时间短的休眠模式到功耗极低的全掉电模式。休眠模式有两种,LVDS时钟(FCLK、LCLK)在这两种模式下均运行,从而维持与接收器的同步。第一种是启动时间很短的轻度休眠模式(sleep\*\_ch),第二种是启动时间与全掉电模式相同的深度休眠模式(sleep)。

sleep4\_ch<n>=1时,四通道设置中的通道<n>进入休眠模式。sleep2\_ch<n>=1时,双通道设置中的通道<n>进入休眠模式。sleep1\_ch1=1时,单通道设置中的ADC通道进入休眠模式。这是启动时间很短的轻度休眠模式。

设置sleep = 1将使所有通道休眠,但FCLK和LCLK继续运行以维持LVDS同步。启动时间与完全掉电模式相同。功耗显著低于利用sleep\*\_ch寄存器使所有通道休眠的模式。

设置pd = 1会使芯片完全掉电,包括带隙基准电压电路。从这种模式启动的时间显著长于从sleep\*\_ch模式启动。LCLK和FCLK输出被置于高阻态,因而与LVDS接收器的同步丢失。

当PD引脚设为高电平时,设置pdn\_pin\_cfg<1:0> = x1会配置电路进入休眠通道模式(所有通道关闭)。这与利用sleep\*\_ch 寄存器使所有通道休眠相同。使用PD引脚不能分别关断各个通道。当PD引脚设为高电平时,设置pdn\_pin\_cfg<1:0> = 10 会配置电路进入(深度)休眠模式(相当于设置sleep=1)。当PD引脚设为高电平时,设置pdn\_pin\_cfg<1:0> = 00(默认值)会配置电路进入掉电模式。

lvds\_pd\_mode寄存器配置LVDS数据输出驱动器在休眠和休眠通道模式下是关断还是保持活动。LCLK和FCLK驱动器不受此寄存器影响,在休眠和休眠通道模式下始终开启。如果lvds\_pd\_mode设为0(默认值),则LVDS输出处于高阻态,驱动器完全掉电。如果lvds\_pd\_mode设为1,则LVDS输出设置为常数0,驱动器在休眠和休眠通道模式下仍然开启。

## 可编程增益

| 名称                     | 描述                     | 默认             | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | DЗ | D2 | D1 | D0 | 十六进制<br>地址 |

|------------------------|------------------------|----------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| coarse_gain<br>_cfg    | 配置粗调增益设置。              | x增益<br>使能      |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | х  | 0x33       |

| fine_gain_en           | 启用精调增益。                | 禁用             |     |     |     |     |     |     |    |    |    |    |    |    |    |    | х  |    | 0.833      |

| cgain4_ch1<br><3:0>    | 四通道设置中通道1的<br>可编程粗调增益。 | 1x增益           |     |     |     |     |     |     |    |    |    |    |    |    | х  | х  | х  | х  |            |

| cgain4_ch2<br><3:0>    | 四通道设置中通道2的<br>可编程粗调增益。 | 1x增益           |     |     |     |     |     |     |    |    | х  | х  | х  | х  |    |    |    |    | 004        |

| cgain4_ch3<br><3:0>    | 四通道设置中通道3的<br>可编程粗调增益。 | 1x增益           |     |     |     |     | х   | х   | х  | х  |    |    |    |    |    |    |    |    | 0x2A       |

| cgain4_ch4<br><3:0>    | 四通道设置中通道4的<br>可编程粗调增益。 | 1x增益           | х   | х   | х   | х   |     |     |    |    |    |    |    |    |    |    |    |    |            |

| cgain2_ch1<br><3:0>    | 双通道设置中通道1的<br>可编程粗调增益。 | 1x增益           |     |     |     |     |     |     |    |    |    |    |    |    | х  | х  | х  | х  |            |

| cgain2_ch2<br><3:0>    | 双通道设置中通道2的<br>可编程粗调增益。 | 1x增益           |     |     |     |     |     |     |    |    | х  | х  | х  | х  |    |    |    |    | 0x2B       |

| cgain1_ch1<br><3:0>    | 单通道设置中通道1的<br>可编程粗调增益。 | 1x增益           |     |     |     |     | х   | х   | х  | х  |    |    |    |    |    |    |    |    |            |

| fgain_<br>branch1<6:0> | 分支1的可编程<br>精调增益。       | 1x / 0dB<br>增益 |     |     |     |     |     |     |    |    |    | х  | х  | Х  | Х  | х  | х  | х  | 004        |

| fgain_<br>branch2<6:0> | 分支2的可编程<br>精调增益。       | 1x / 0dB<br>增益 |     | х   | х   | х   | х   | х   | х  | х  |    |    |    |    |    |    |    |    | 0x34       |

| fgain_<br>branch3<6:0> | 分支3的可编程<br>精调增益。       | 1x / 0dB<br>增益 |     |     |     |     |     |     |    |    |    | х  | х  | Х  | х  | х  | х  | х  | 0.05       |

| fgain_<br>branch4<6:0> | 分支4的可编程<br>精调增益。       | 1x / 0dB<br>增益 |     | х   | х   | х   | х   | х   | х  | х  |    |    |    |    |    |    |    |    | 0x35       |

| fgain_<br>branch5<6:0> | 分支5的可编程<br>精调增益。       | 1x / 0dB<br>增益 |     |     |     |     |     |     |    |    |    | х  | х  | Х  | х  | х  | х  | х  | 0.00       |

| fgain_<br>branch6<6:0> | 分支6的可编程<br>精调增益。       | 1x / 0dB<br>增益 |     | х   | х   | х   | х   | х   | х  | х  |    |    |    |    |    |    |    |    | 0x36       |

| fgain_<br>branch7<6:0> | 分支7的可编程<br>精调增益。       | 1x / 0dB<br>增益 |     |     |     |     |     |     |    |    |    | х  | х  | Х  | Х  | х  | х  | х  | 0,427      |

| fgain_<br>branch8<6:0> | 分支8的可编程<br>精调增益。       | 1x / 0dB<br>增益 |     | х   | х   | х   | х   | х   | х  | х  |    |    |    |    |    |    |    |    | 0x37       |

除满量程控制外,该器件还有可编程增益功能。各通道的可编程增益可利用一个四位码(表示为cgain\*<3:0>)独立设置。增益由寄存器cgain\_cfg配置,当cgain\_cfg=0时,使能dB步进增益,如表22所示;当cgain\_cfg=1时,增益由表23定义。

#### 表22: 增益设置 - dB步进

| cgain_cfg | cgain*<3:0> | 实现的增益(dB) |

|-----------|-------------|-----------|

| 0         | 0000        | 0         |

| 0         | 0001        | 1         |

| 0         | 0010        | 2         |

| 0         | 0011        | 3         |

| 0         | 0100        | 4         |

| 0         | 0101        | 5         |

| 0         | 0110        | 6         |

| 0         | 0111        | 7         |

| 0         | 1000        | 8         |

| 0         | 1001        | 9         |

| 0         | 1010        | 10        |

| 0         | 1011        | 11        |

| 0         | 1100        | 12        |

| 0         | 1101        | 未使用       |

| 0         | 1110        | 未使用       |

| 0         | 1111        | 未使用       |

## 表23: 增益设置-x步进

| cgain_cfg | cgain*<3:0> | 实现的增益系数[x] |

|-----------|-------------|------------|

| 1         | 0000        | 1          |

| 1         | 0001        | 1.25       |

| 1         | 0010        | 2          |

| 1         | 0011        | 2.5        |

| 1         | 0100        | 4          |

| 1         | 0101        | 5          |

| 1         | 0110        | 8          |

| 1         | 0111        | 10         |

| 1         | 1000        | 12.5       |

| 1         | 1001        | 16         |

| 1         | 1010        | 20         |

| 1         | 1011        | 25         |

| 1         | 1100        | 32         |

| 1         | 1101        | 50         |

| 1         | 1110        | 未使用        |

| 1         | 1111        | 未使用        |

各ADC分支实现了数字精调增益功能,可调整分支之间的精密增益误差。该增益由fgain\_branch\*控制,如表24所示。 对于高速交错模式,使用数字精调增益时不会有失码,因为内部分辨率较高(1位)。

要使能精调增益功能,寄存器位fine\_gain\_en须设为1。

#### 表24: 精调增益设置

| fgain_branchx<6:0> |   |   |   | <6:0> |   |   | 算术函数                                                                                                                            | 实现的增益(x) | 增益(dB)  |

|--------------------|---|---|---|-------|---|---|---------------------------------------------------------------------------------------------------------------------------------|----------|---------|

| 0                  | 1 | 1 | 1 | 1     | 1 | 1 | OUT = $(1 + 2^{-8} + 2^{-9} + 2^{-10} + 2^{-11} + 2^{-12} + 2^{-13}) * IN$                                                      | 1.0077   | 0.0665  |

| 0                  | 1 | 1 | 1 | 1     | 1 | 0 | OUT = $(1 + 2^{-8} + 2^{-9} + 2^{-10} + 2^{-11} + 2^{-12}) * IN$                                                                | 1.0076   | 0.0655  |

| 0                  | 1 | 1 | 1 | 1     | 0 | 1 | OUT = $(1 + 2^{-8} + 2^{-9} + 2^{-10} + 2^{-11} + 2^{-13}) * IN$                                                                | 1.0074   | 0.0644  |

| 0                  | 1 | 1 | 1 | 1     | 0 | 0 | OUT = $(1 + 2^{-8} + 2^{-9} + 2^{-10} + 2^{-11}) * IN$                                                                          | 1.0073   | 0.0634  |

| 0                  | 0 | 0 | 0 | 0     | 1 | 1 | OUT = (1 + 2 <sup>-12</sup> + 2 <sup>-13</sup> ) * IN                                                                           | 1.0004   | 0.0031  |

| 0                  | 0 | 0 | 0 | 0     | 1 | 0 | OUT = (1 + 2 <sup>-12</sup> ) * IN                                                                                              | 1.0002   | 0.0021  |

| 0                  | 0 | 0 | 0 | 0     | 0 | 1 | OUT = (1 + 2 <sup>-13</sup> ) * IN                                                                                              | 1.0001   | 0.0010  |