# 具 I<sup>2</sup>C 命令和 遥测功能的 Anyside™ 高电压隔离型开关控制器

# 特点

- UL-CSA 标准的认证中:5kV<sub>RMS</sub> (持续一分钟)

- 增强绝缘型

- 内部集成隔离型电源

- 可调的上电斜坡速率和电流限值

- I<sup>2</sup>C/SMBus 接口

- 10 位 ADC 负责监视电流和两个独立通道

- 可抑制高共模瞬变:≥30kV/μs

- 故障状态警报和电源良好输出

- 含独立的 3V 至 5.5V 逻辑电源

- 可在绝缘隔离两端提供 ±20kV ESD 防护

- 最大连续工作电压:690V<sub>BMS</sub>

- 14.6mm 爬电距离

- 低电流关闭模式 (<10µA)</p>

- 22mm x 9mm x 5.16mm BGA 封装

# 屈 用

- 高电压直流热插拔

- 带电背板插入

- 隔离型分布式电源系统

- 电源监视器

- 工业控制系统

- 隔断接地环路

▲▼、LT、LTC、LTM、Linear Technology、µModule、LTspice 和 Linear 标识是 Analog Devices 公司的注册商标。PowerPath 和 Anyside 是 Analog Devices 公司的商标。所有其他 商标均为其各自拥有者的产权。

### 描述

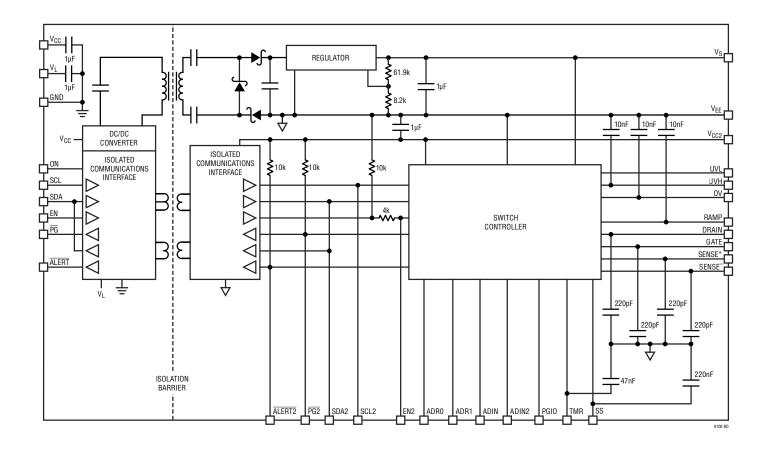

LTM®9100 μModule® (微型模块) 控制器是一款具有 I<sup>2</sup>C 接口的完整电气隔离型开关控制器,可用作负载开关或热插 拔控制器。由一个外部 N 沟道 MOSFET 开关对负载实施软 起动和控制。过流保护最大限度地减小了启动、输入阶跃和 输出短路情况下的 MOSFET 应力。由于开关的隔离、浮动 特性,因此它可以容易地通过配置以在高侧、低侧和浮动应 用中使用。

单个 5V 电源通过一个集成的隔离式 DC/DC 转换器为开关 控制器的两侧供电。与主电源无关的一个单独的逻辑电源输 入提供了与 3V 至 5.5V 逻辑电平的简易连接。负载电流和 两个额外电压输入的隔离式测量由一个 10 位 ADC 完成, 并通过  $I^2C$  接口访问。

利用一个  $5kV_{RMS}$  绝缘隔离把逻辑和  $I^2C$  接口与开关控制 器隔离开来,从而使得 LTM9100 非常适合用于高达 1000V<sub>DC</sub> 之总线供电工作的开关,以及用于在那些接地通 路断开以允许大共模电压摆幅的系统中提供电气隔离。在共 模瞬变高达 30kV/μs 的情况下,可保证通信不会出现中 断。

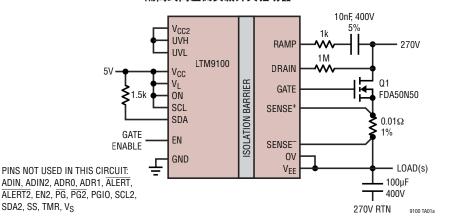

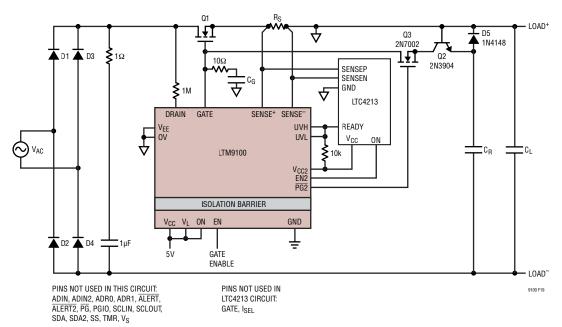

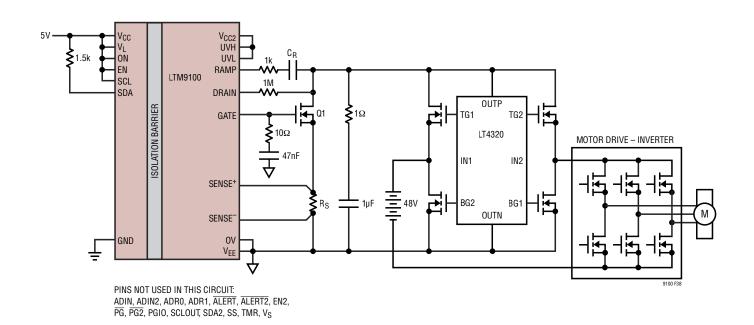

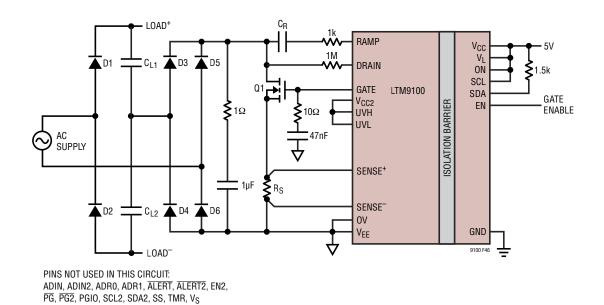

# 典型应用

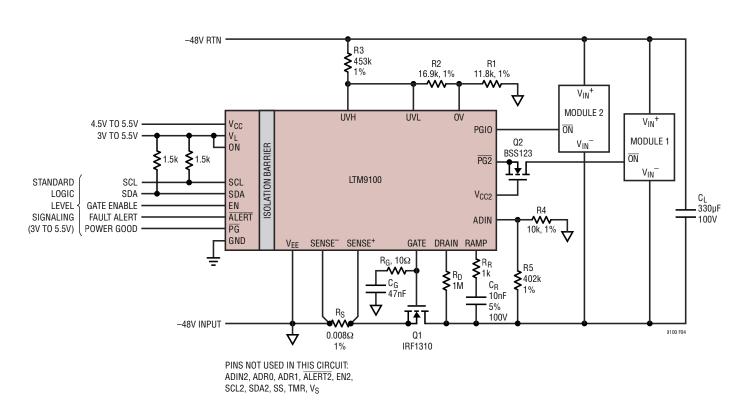

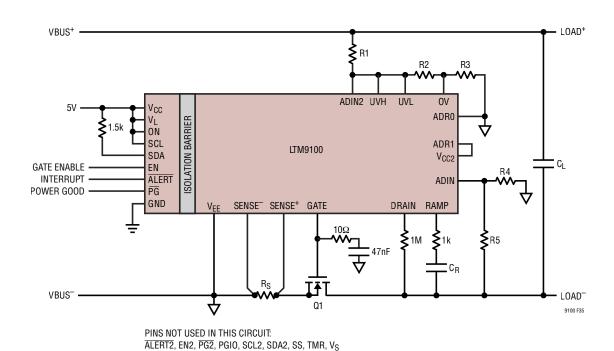

SDA2, SS, TMR, V<sub>S</sub>

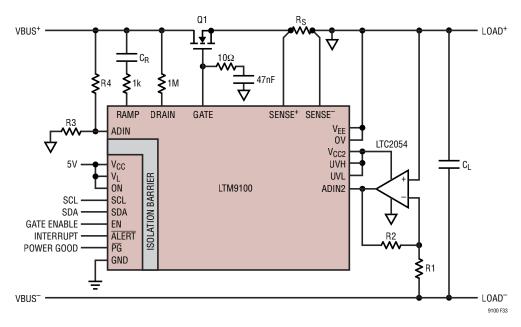

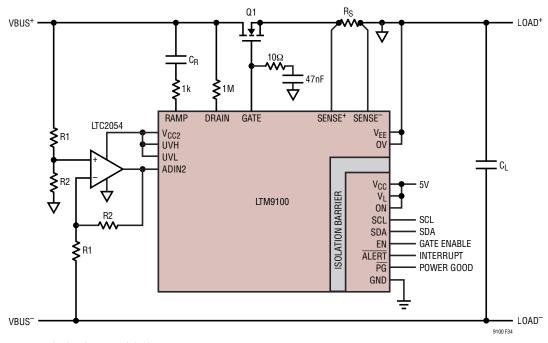

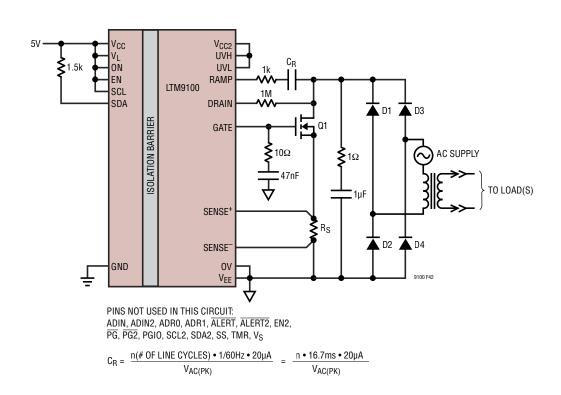

#### 隔离式高压侧负载开关驱动器

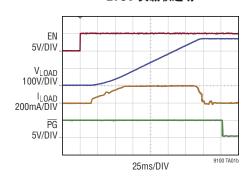

#### 270V 负载软起动

# LTM9100

# 目录

| 特点                   | 1  |

|----------------------|----|

| 应用                   | 1  |

| 典型应用                 | 1  |

| 描述                   | 1  |

| 绝对最大额定值              | 3  |

| 引脚配置                 | 3  |

| 订购信息                 | 3  |

| 电气特性                 | 4  |

| 开关特性                 | 6  |

| 隔离特性                 |    |

| 典型性能特征               | _  |

| 引脚功能                 |    |

| 方框图                  |    |

| 测试电路                 |    |

| 应用信息                 |    |

| 概要                   |    |

| μModule 技术           |    |

| DC/DC 转换器            |    |

| 从总线给 LTM9100 供电      |    |

| 低压侧应用                |    |

| 高压侧应用                |    |

| 切换 PowerPath™ (电源路径) |    |

| V <sub>L</sub> 逻辑电源  |    |

| 安全地热插拔               |    |

| 通道时序不确定性             |    |

| 初始启动和浪涌控制            |    |

| 电源状态良好监视器            |    |

| 关断序列和自动重试            |    |

| 接通 GATE 引脚 (外部 FET)  |    |

| 过流保护和过流故障            |    |

| 过压故障                 |    |

| 欠压比较器和欠压故障           | 25 |

| FET 短路故障                   | 27 |

|----------------------------|----|

| 外部故障监视器                    | 27 |

| 故障警报                       | 27 |

| 使故障复位                      | 28 |

| 数据转换器                      | 28 |

| 配置 PGIO 引脚                 | 28 |

| 设计步骤                       | 28 |

| 设计实例 #1                    | 30 |

| 设计实例 #2                    | 31 |

| 外部开关                       | 32 |

| 提升栅极电压                     | 33 |

| 负栅极偏置                      | 33 |

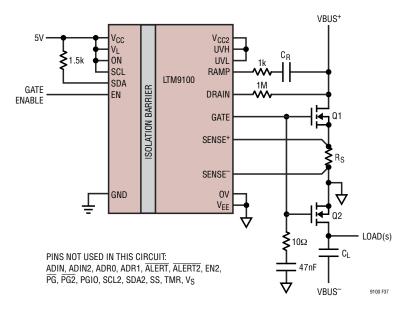

| 并联开关                       | 34 |

| 具有 AC 纹波 (整流 AC) 的 DC 总线   | 34 |

| 芯片间通信总线 (I <sup>2</sup> C) |    |

| START 和 STOP 条件            | 37 |

| 阻塞总线复位                     | 37 |

| I <sup>2</sup> C 设备寻址      | 38 |

| 确认                         | 38 |

| 写协议                        |    |

| 读协议                        |    |

| 警报响应协议                     |    |

| 单线广播模式                     |    |

| 寄存器地址和内容                   |    |

| RF、磁场抗扰度                   |    |

| PCB 布局                     |    |

| 典型应用                       |    |

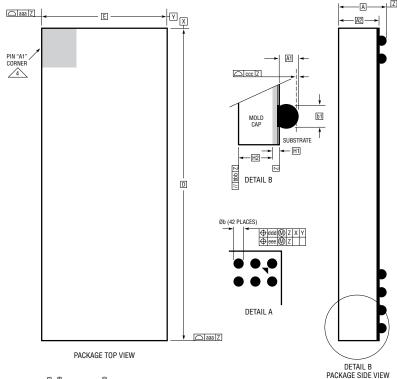

| 封装描述                       |    |

| 典型应用                       | 54 |

# 绝对最大额定值

(注1、2)

| V <sub>CC</sub> 至 GND0.3V 至 6V                        | UVL \ UVH :            |

|-------------------------------------------------------|------------------------|

| V <sub>L</sub> 至 GND0.3V 至 6V                         | PGIO 至 V <sub>EE</sub> |

| V <sub>CC2</sub> 至 V <sub>EE</sub> 0.3V 至 5.5V        | SENSE+ 至 S             |

| V <sub>S</sub> 至 V <sub>EE</sub> (注 3) −0.3V 至 10.65V | SENSE-至\               |

| DRAIN 至 V <sub>EE</sub> (注 4) −0.3V 至 3.5V            | 环境工作温度                 |

| PG · ALERT · EN · SDA · SCL ·                         | LTM9100                |

| ON 至 GND0.3V 至 (V <sub>L</sub> + 0.3V)                | LTM9100                |

| SCL2 · SDA2 · ADR0 · ADR1 · ALERT2 · PG2 · ADIN ·     | LTM9100                |

| ADIN2 · RAMP · OV · SS · EN2 ·                        | 最大内部工作                 |

| TMR 至 $V_{EE}$ $-0.3V$ 至 $(V_{CC2} + 0.3V)$           |                        |

| GATE 至 V <sub>EE</sub> 0.3V 至 (V <sub>S</sub> + 0.3V) | 峰值回流焊体                 |

| UVL、UVH 至 V <sub>EE</sub> | 0.3V 至 10V   |

|---------------------------|--------------|

| PGIO 至 V <sub>EE</sub>    | 0.3V 至 80V   |

| SENSE+ 至 SENSE            | 0.3V 至 0.3V  |

| SENSE-至 V <sub>EE</sub>   | 0.3V 至 0.3V  |

| 环境工作温度范围 (注 5)            |              |

| LTM9100C                  | 0°C 至 70°C   |

|                           | 40°C 至 85°C  |

| LTM9100H                  | 40°C 至 105°C |

| 最大内部工作温度                  | 125°C        |

| 贮存温度范围                    | 55°C 至 125°C |

| 峰值回流焊体温度                  | 245°C        |

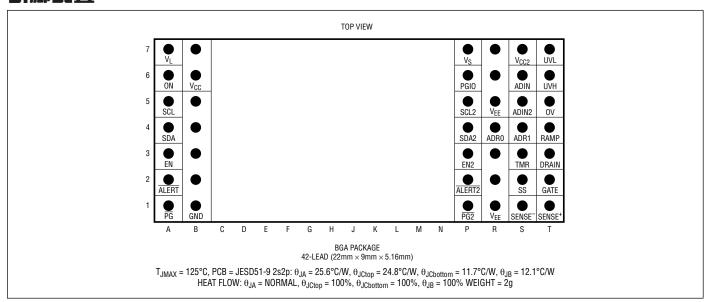

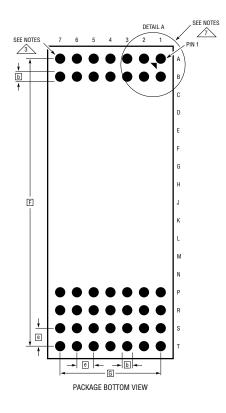

# 引脚配置

# 订购信息 http://www.linear.com.cn/product/LTM9100#orderinfo

|               |               | 器件标记     |      | 封装  | MSL |               |

|---------------|---------------|----------|------|-----|-----|---------------|

| 器件型号          | 衬垫或焊球涂层       | 器件       | 涂层代码 | 类型  | 等级  | 温度范围          |

| LTM9100CY#PBF |               |          |      |     |     | 0°C 至 70°C    |

| LTM9100IY#PBF | SAC305 (RoHS) | LTM9100Y | e1   | BGA | 3   | -40°C 至 85°C  |

| LTM9100HY#PBF |               |          |      |     |     | -40°C 至 105°C |

- 器件温度等级请见外包装箱上的标识。

- 衬垫或焊球涂层代码依据 IPC/JEDEC J-STD-609 标准。

- 端子涂层器件标记:www.linear.com.cn/leadfree

- 本产品不建议用于第二面回流焊。如需了解更多信息,请登录www.linear.com.cn/BGA-assy

- 推荐的 BGA PCB 装配及制造程序: www.linear.com.cn/BGA-assy

- BGA 封装和托盘制图: www.linear.com.cn/packaging

- 本产品对湿度很敏感。如需了解更多信息,请登录: www.linear.com.cn/BGA-assy

9100

**电气特性** 凡标注 ● 表示该指标适合整个规定工作温度范围,否则仅指 T<sub>A</sub> = 25°C。V<sub>CC</sub> = 5V,V<sub>L</sub> = 3.3V,和 GND = V<sub>EE</sub> = 0V,ON = V<sub>L</sub>,除非另有说明。

| 符号                      | 参数                                            | 条件                                                                                      |   | 最小值                   | 典型值        | 最大值                   | 单位       |

|-------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------|---|-----------------------|------------|-----------------------|----------|

| 电源                      | •                                             | •                                                                                       |   |                       |            |                       |          |

| $\overline{V_{CC}}$     | 输入电源范围                                        |                                                                                         | • | 4.5                   |            | 5.5                   | V        |

| I <sub>CC</sub>         | 输入电源电流                                        | ON = OV                                                                                 | • |                       | 0          | 10                    | μА       |

|                         | WH # 1 + F # # #                              | ON = V <sub>L</sub> ,无负载                                                                | • |                       | 50         | 70                    | mA       |

| $V_L$                   | 逻辑输入电源范围                                      | 211 211                                                                                 | • | 3                     |            | 5.5                   | V        |

|                         | 逻辑输入电源电流                                      | ON = 0V<br>ON = V <sub>L</sub>                                                          | • |                       | 0<br>3.2   | 10<br>4.5             | μA<br>mA |

|                         | V <sub>L</sub> 欠压闭锁门限                         | V <sub>L</sub> 逐渐上升                                                                     | • | 2.3                   |            | 2.7                   | V        |

|                         | V <sub>L</sub> 欠压闭锁迟滞                         |                                                                                         |   |                       | 100        |                       | mV       |

| $\overline{V_S}$        | ─────────────────────────────────<br>│稳定的输出电压 | I <sub>LOAD</sub> = 0mA 至 35mA                                                          | • | 9.65                  | 10.4       | 11.15                 | V        |

| $\overline{V_Z}$        | 在 V <sub>S</sub> 的并联稳压器电压                     | I <sub>S</sub> = 10mA · V <sub>CC</sub> = 0V                                            | • | 10.4                  | 11.2       | 12                    | V        |

|                         |                                               | I <sub>S</sub> = 10mA 至 25mA , V <sub>CC</sub> = 0V                                     | • |                       | 370        | 600                   | V        |

| Is                      | V <sub>S</sub> 电源电流                           | V <sub>S</sub> = 10.4V , V <sub>CC</sub> = 0V                                           | • |                       | 7          | 12                    | mA       |

| -                       | V <sub>S</sub> 欠压闭锁门限                         | V <sub>S</sub> 逐渐上升,V <sub>CC</sub> = 0V                                                | • | 8.5                   | 9          | 9.5                   | V        |

|                         | V <sub>S</sub> 欠压闭锁迟滞                         | V <sub>CC</sub> = 0V                                                                    | • | 0.3                   | 0.7        | 1.1                   | V        |

| V <sub>CC2</sub>        | 稳定的输出电压                                       | I <sub>LOAD</sub> = 0mA 至 15mA                                                          | • | 4.75                  | 5          | 5.25                  | V        |

| 栅极驱动 (El                | $N = V_L$ , $UVL = UVH = V_{CC2}$ , $OV = OV$ | ,除非另有说明)                                                                                |   |                       |            |                       |          |

| V <sub>GATEH</sub>      | GATE 引脚输出高电压                                  | V <sub>S</sub> = 10.4V , V <sub>CC</sub> = 0V                                           | • | 9.75                  | 10         | 10.25                 | V        |

| I <sub>GATE(UP)</sub>   | GATE 引脚上拉电流                                   | V <sub>GATE</sub> = 4V                                                                  | • | -7.5                  | -11.5      | -15.5                 | μA       |

| I <sub>GATE(OFF)</sub>  | GATE 关断电流                                     | V <sub>SENSE</sub> = 400mV · V <sub>GATE</sub> = 4V<br>EN = 0V · V <sub>GATE</sub> = 4V | • | 45<br>120             | 100<br>175 | 150<br>250            | mA<br>mA |

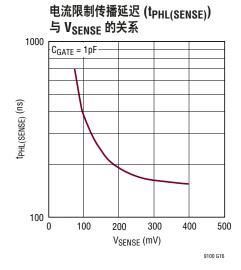

| t <sub>PHL(SENSE)</sub> | SENSE 高电平至电流限制传播延迟                            | V <sub>SENSE</sub> = 100mV 至 GATE 低电平<br>V <sub>SENSE</sub> = 300mV 至 GATE 低电平          | • |                       | 0.5<br>0.2 | 1.5<br>0.5            | μs<br>μs |

|                         | GATE 关断传播延迟                                   | EN ↓至 GATE 低电平<br>OV ↑、UVL ↓至 GATE 低电平                                                  | • |                       | 0.2<br>1.4 | 0.5<br>2              | μs<br>μs |

|                         | GATE 关断传播延迟                                   | V <sub>SENSE</sub> = 300mV 至 <del>PG2</del> ↑                                           | • | 440                   | 530        | 620                   | μs       |

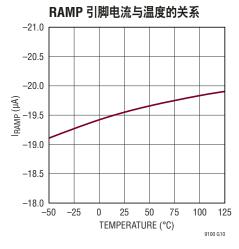

| I <sub>RAMP</sub>       | RAMP 引脚电流                                     | V <sub>SS</sub> = 2.56V                                                                 | • | -18                   | -20        | -22                   | μA       |

| $\overline{V_{SS}}$     | SS 引脚箝位电压                                     |                                                                                         | • | 2.43                  | 2.56       | 2.69                  | V        |

|                         | SS 引脚上拉电流                                     | V <sub>SS</sub> = 0V                                                                    | • | -7                    | -10        | -13                   | μA       |

|                         | SS 引脚下拉电流                                     | EN = 0V , V <sub>SS</sub> = 2.56V                                                       | • | 6                     | 12         | 20                    | mA       |

| 输入引脚                    |                                               |                                                                                         | • | •                     |            |                       |          |

|                         | EN、ON 输入门限电压                                  |                                                                                         | • | 0.33 • V <sub>L</sub> |            | 0.67 • V <sub>L</sub> | V        |

|                         | EN、ON 输入迟滞                                    | (注 6)                                                                                   |   |                       | 150        |                       | mV       |

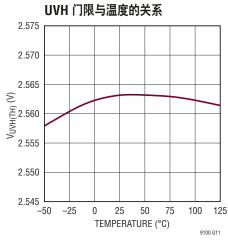

| V <sub>UVH(TH)</sub>    | UVH 门限电压                                      | V <sub>UVH</sub> 逐渐上升                                                                   | • | 2.518                 | 2.56       | 2.598                 | V        |

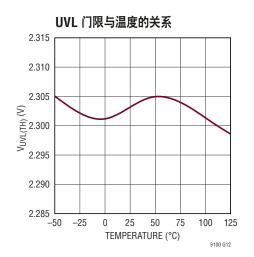

| $V_{\text{UVL(TH)}}$    | UVL 门限电压                                      | V <sub>UVL</sub> 逐渐下降                                                                   | • | 2.248                 | 2.291      | 2.328                 | V        |

| $\Delta V_{UV(HYST)}$   | UV 迟滞                                         | UVH 和 UVL 连接在一起                                                                         | • | 236                   | 269        | 304                   | mV       |

| $\delta V_{UV}$         | UVH、UVL 迟滞                                    |                                                                                         |   |                       | 15         |                       | mV       |

|                         | UVL 复位门限电压                                    | V <sub>UVL</sub> 逐渐下降                                                                   | • | 1.12                  | 1.21       | 1.30                  | V        |

|                         | UVL 复位迟滞                                      |                                                                                         |   |                       | 60         |                       | mV       |

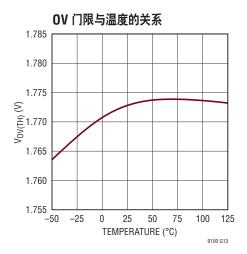

| V <sub>OV(TH)</sub>     | OV 引脚门限电压                                     | V <sub>OV</sub> 逐渐上升                                                                    | • | 1.735                 | 1.770      | 1.805                 | V        |

电气精性 凡标注 ● 表示该指标适合整个规定工作温度范围,否则仅指  $T_A=25$ °C。 $V_{CC}=5V$ , $V_L=3.3V$ ,和  $GND=V_{EE}=0V$ ,  $ON=V_L$ ,除非另有说明。

| 符号                  | 参数                | 条件                                                                                            |   | 最小值                                            | 典型值                    | 最大值                                           | 单位       |

|---------------------|-------------------|-----------------------------------------------------------------------------------------------|---|------------------------------------------------|------------------------|-----------------------------------------------|----------|

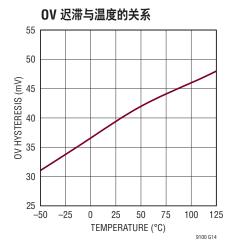

|                     | OV 引脚迟滞           |                                                                                               | • | 18                                             | 37.5                   | 62                                            | mV       |

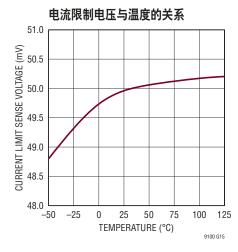

|                     | 电流限制检测引脚门限        | SENSE+ - SENSE-                                                                               | • | 45                                             | 50                     | 55                                            | mV       |

|                     | PGIO 引脚输入门限电压     | V <sub>PGIO</sub> 逐渐上升                                                                        | • | 1.10                                           | 1.25                   | 1.40                                          | V        |

|                     | PGIO 引脚输入迟滞       |                                                                                               |   |                                                | 100                    |                                               | mV       |

|                     | 输入电流              | ON \ EN \ UVH \ UVL \ OV \ SENSE+<br>SENSE-                                                   | • |                                                | 0<br>-10               | ±2<br>-20                                     | μA<br>μA |

| 定时器                 |                   |                                                                                               | ' | •                                              |                        |                                               |          |

|                     | TMR 引脚高电平门限       | V <sub>TMR</sub> 逐渐上升                                                                         | • | 2.43                                           | 2.56                   | 2.69                                          | V        |

|                     | TMR 引脚低电平门限       | V <sub>TMR</sub> 逐渐下降                                                                         | • | 40                                             | 75                     | 110                                           | mV       |

|                     | TMR 引脚上拉电流        | 接通和自动重试 (OC 除外) 延迟,<br>V <sub>TMR</sub> = 0.2V                                                | • | -7                                             | -10                    | -13                                           | μА       |

|                     |                   | 电源良好和 OC 自动重试延迟, $V_{TMR} = 0.2V$                                                             | • | -3.5                                           | -5                     | <b>-</b> 7                                    | μА       |

|                     | TMR 引脚下拉电流        | 延迟 (OC 自动重试除外), V <sub>TMR</sub> = 2.56V                                                      | • | 6                                              | 12                     | 20                                            | mA       |

|                     |                   | OC 自动重试延迟,V <sub>TMR</sub> = 2.56V                                                            | • | 3                                              | 5                      | 7                                             | μA       |

| 输出引脚                |                   |                                                                                               | • |                                                |                        |                                               |          |

| V <sub>OH</sub>     | 输出高电压             | $\overline{ALERT}$ , $I_{LOAD} = -4mA$ , $\overline{PG}$ , $I_{LOAD} = -2mA$                  | • | V <sub>L</sub> - 0.4                           |                        |                                               | V        |

| $V_{OL}$            | 输出低电压             | ALERT $\cdot$ I <sub>LOAD</sub> = 4mA $\cdot$ $\overline{PG}$ $\cdot$ I <sub>LOAD</sub> = 2mA | • |                                                |                        | 0.4                                           | V        |

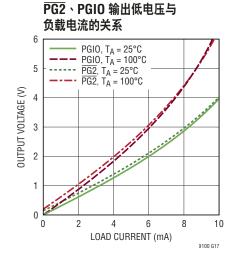

|                     |                   | $PGIO \cdot I_{LOAD} = 3mA$ $ALERT2 \cdot PG2 \cdot PGIO \cdot I_{LOAD} = 500\mu A$           |   |                                                | 0.8<br>0.15            | 1.6<br>0.4                                    | V<br>V   |

|                     | <br>输入电流          | PGIO = 80V                                                                                    |   |                                                | 0.13                   | 10                                            | μA       |

|                     | 短路电流              | $0V \le \overline{ALERT} \le V_I$                                                             |   |                                                | 0                      | ±85                                           | mΑ       |

|                     |                   | $0V \leq \overline{PG} \leq V_1$                                                              |   |                                                | ±30                    | ±00                                           | mA       |

|                     |                   | $OV \leq \overline{ALERT2}$ , $\overline{PG2} \leq V_{CC2}$                                   |   |                                                | ±30                    | . 0                                           | mA       |

| ADC                 |                   | $0V \le EN2 \le V_{CC2}$                                                                      | • |                                                |                        | ±2                                            | mA       |

| ADC                 | <br>分辨率 (无漏失码)    | (注 6)                                                                                         |   | 10                                             |                        |                                               | 位        |

| INL                 | 积分非线性             | SENSE                                                                                         |   | 10                                             | ±0.5                   | ±2.5                                          | LSB      |

| IIVL                |                   | ADIN · ADIN2                                                                                  | • |                                                | ±0.25                  | ±1.25                                         | LSB      |

|                     | 偏移误差              | SENSE                                                                                         | • |                                                |                        | ±2.25                                         | LSB      |

|                     |                   | ADIN · ADIN2                                                                                  | • |                                                |                        | ±1.25                                         | LSB      |

|                     | 全标度电压             | SENSE<br>ADIN · ADIN2                                                                         | • | 62.8<br>2.514                                  | 64<br>2.560            | 65.2<br>2.606                                 | mV<br>V  |

|                     | 总未调整误差            | SENSE<br>ADIN · ADIN2                                                                         | • |                                                |                        | ±1.8<br>±1.6                                  | %<br>%   |

| •                   | 转换速率              |                                                                                               | • | 5.5                                            | 7.3                    | 9                                             | Hz       |

|                     | ADIN、ADIN2 引脚输入电阻 | ADIN · ADIN2 = 1.28V                                                                          | • | 2                                              | 10                     |                                               | MΩ       |

|                     | ADIN、ADIN2 引脚输入电流 | ADIN · ADIN2 = 2.56V                                                                          | • |                                                | 0                      | ±2                                            | μA       |

| I <sup>2</sup> C 接口 |                   |                                                                                               | • |                                                |                        |                                               |          |

|                     | ADR0、ADR1 输入高门限   |                                                                                               | • | V <sub>CC2</sub> - 0.8                         | V <sub>CC2</sub> - 0.5 | $V_{CC2} - 0.3$                               | V        |

|                     | ADR0、ADR1 输入低门限   |                                                                                               | • | 0.3                                            | 0.5                    | 0.8                                           | V        |

|                     | ADRO、ADR1 输入电流    | ADR0 \ ADR1 = 0V \ V <sub>CC2</sub><br>ADR0 \ ADR1 = 0.8V \ (V <sub>CC2</sub> - 0.8V)         | • | ±10                                            |                        | ±80                                           | μA<br>μA |

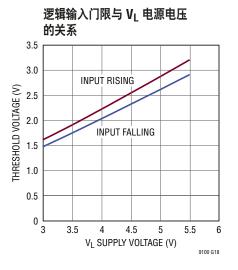

|                     | 输入门限电压            | SCL · SDA<br>SDA2                                                                             | • | 0.3 • V <sub>L</sub><br>0.3 • V <sub>CC2</sub> |                        | 0.7V • <sub>L</sub><br>0.7 • V <sub>CC2</sub> | V        |

|                     | 1                 | 1                                                                                             | ı | 1 332                                          |                        |                                               | 9100f    |

**电气特性** 凡标注 ● 表示该指标适合整个规定工作温度范围,否则仅指 T<sub>A</sub> = 25°C。V<sub>CC</sub> = 5V,V<sub>L</sub> = 3.3V,和 GND = V<sub>EE</sub> = 0V,ON = V<sub>L</sub>,除非另有说明。

| 符号              | 参数              | 条件                                                                                                                                      |   | 最小值                    | 典型值                                              | 最大值                      | 单位             |

|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|---|------------------------|--------------------------------------------------|--------------------------|----------------|

|                 | 输入电流            | SCL、SDA = V <sub>L</sub> 或 0V                                                                                                           | • |                        |                                                  | ±2                       | μA             |

|                 | 输入迟滞            | SCL · SDA<br>SDA2                                                                                                                       |   |                        | 0.05 • V <sub>L</sub><br>0.05 • V <sub>CC2</sub> |                          | mV<br>mV       |

| $V_{OH}$        | 输出高电压           | SCL2 , I <sub>LOAD</sub> = -2mA                                                                                                         | • | V <sub>CC2</sub> - 0.4 |                                                  |                          | V              |

| V <sub>OL</sub> | 输出低电压           | SDA,I <sub>LOAD</sub> = 3mA,SCL2,I <sub>LOAD</sub> = 2mA<br>SDA2,无负载,SDA = 0V                                                           | • |                        |                                                  | 0.4<br>0.45              | V              |

|                 | 输入引脚电容          | SCL, SDA, SDA2 (注 6)                                                                                                                    | • |                        |                                                  | 10                       | pF             |

|                 | 总线电容负载          | SCL2,标准速度 (注 6)<br>SCL2,快速<br>SDA,SDA2,SR ≥ 1V/μs,标准速度 (注 6)<br>SDA,SDA2,SR ≥ 1V/μs,快速                                                  | • |                        |                                                  | 400<br>200<br>400<br>200 | pF<br>pF<br>pF |

|                 | 最小总线转换速率        | SDA , SDA2                                                                                                                              |   | 1                      |                                                  |                          | V/µs           |

|                 | 短路电流            | $SDA2 = 0 , SDA = V_L$ $0V \le SCL2 \le V_{CC2}$ $SDA = 0 , SDA2 = V_{CC2}$ $SDA = V_L , SDA2 = 0$                                      | • |                        | ±30<br>6<br>-1.8                                 | 100                      | mA<br>mA<br>mA |

| ESD (HB         | M) (注 6)        |                                                                                                                                         | • | 1                      |                                                  |                          |                |

|                 | ESD (HBM) (注 6) | (V <sub>CC2</sub> , V <sub>S</sub> , V <sub>EE</sub> ) 至 (V <sub>CC</sub> , V <sub>L</sub> , GND) (任意组合)                                |   |                        | ±20                                              |                          | kV             |

|                 | 隔离侧接口引脚         | GATE 至 (V <sub>S</sub> , V <sub>EE</sub> ) (任意组合)<br>(RAMP , DRAIN , SENSE+ , SENSE-)<br>至 (V <sub>CC2</sub> , V <sub>EE</sub> ) (任意组合) |   |                        | ±8                                               |                          | kV             |

|                 | 所有其他引脚          |                                                                                                                                         |   |                        | ±3.5                                             |                          | kV             |

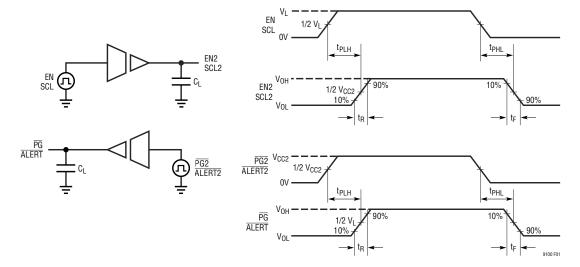

**开关特性** 凡标注 ● 表示该指标适合整个规定工作温度范围,否则仅指 T<sub>A</sub> = 25°C。V<sub>CC</sub> = 5V,V<sub>L</sub> = 3.3V,和 GND = V<sub>EE</sub> = 0V, ON = V<sub>L</sub>,除非另有说明。

| 符号                                  | 参数           | 条件                                                                                                                                                                                                               |   | 最小值 | 典型值               | 最大值               | 单位             |

|-------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------------------|-------------------|----------------|

| 逻辑时序                                |              |                                                                                                                                                                                                                  |   | '   |                   |                   |                |

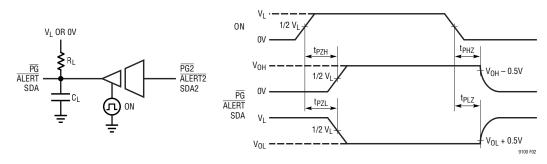

| t <sub>PHL</sub> , t <sub>PLH</sub> | 传播延迟         | $(\overline{PG2}$ , $\overline{ALERT2}$ ) 至 $(\overline{PG}$ , $\overline{ALERT}$ ) , $C_L$ = 15pF (图 1) EN 至 EN2 $(0.5 \bullet V_L \cong 0.1 \bullet V_{CC2})$ , $C_L$ = 15pF (图 1)                             | • | 35  | 60                | 150               | ns             |

| t <sub>R</sub> , t <sub>F</sub>     | 上升和下降时间      | $\overline{ALERT}$ , $C_L = 15pF$ (图 1) $\overline{PG}$ , $C_L = 15pF$ (图 1)                                                                                                                                     | • |     | 7<br>30           | 30<br>50          | ns<br>ns       |

| t <sub>PZH</sub> , t <sub>PZL</sub> | ON 使能时间      | ON $\uparrow$ 至 ( $\overline{PG}$ , $\overline{ALERT}$ ) , $R_L = 1k\Omega$ , $C_L = 15pF$ (图 2)                                                                                                                 | • |     |                   | 320               | μs             |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | ON 停用时间      | ON ↓至 $\overline{(PG)}$ , $\overline{ALERT}$ ), $R_L = 1kΩ$ , $C_L = 15pF$ (图 2)                                                                                                                                 | • |     |                   | 70                | ns             |

| I <sup>2</sup> C 接口时序               |              |                                                                                                                                                                                                                  |   | •   |                   |                   |                |

|                                     | 最大数据速率       | (注 7)                                                                                                                                                                                                            | • | 400 |                   |                   | kHz            |

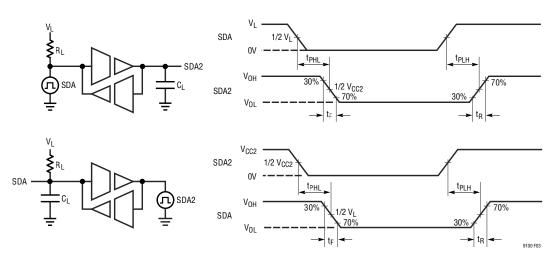

| t <sub>PHL</sub> , t <sub>PLH</sub> | 传播延迟         | SCL 至 SCL2 $^{,}$ C <sub>L</sub> = 15pF (图 1)<br>SDA 至 SDA2 $^{,}$ R <sub>L</sub> = 开路 $^{,}$ C <sub>L</sub> = 15pF (图 3)<br>SDA2 至 SDA $^{,}$ R <sub>L</sub> = 1.1k $\Omega$ $^{,}$ C <sub>L</sub> = 15pF (图 3) | • |     | 150<br>150<br>300 | 225<br>250<br>500 | ns<br>ns<br>ns |

|                                     | SCL 时钟的低电平周期 | (注 6)                                                                                                                                                                                                            |   | 1.3 |                   |                   | μs             |

**开关特性** 凡标注 ● 表示该指标适合整个规定工作温度范围,否则仅指 T<sub>A</sub> = 25°C。V<sub>CC</sub> = 5V,V<sub>L</sub> = 3.3V,和 GND = V<sub>EE</sub> = 0V, ON = V<sub>L</sub>,除非另有说明。

| 符号                   | 参数               | 条件                                                                                                                                                                        |   | 最小值      | 典型值        | 最大值               | 单位             |

|----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|------------|-------------------|----------------|

|                      | SCL 时钟的高电平周期     | (注 6)                                                                                                                                                                     |   | 600      |            |                   | ns             |

|                      | 保持时间 (重复) 起动     | (注 6)                                                                                                                                                                     |   | 600      |            |                   | ns             |

|                      | 建立时间重复起动         | (注 6)                                                                                                                                                                     |   | 600      |            |                   | ns             |

| t <sub>HD(DAT)</sub> | 数据保持时间           | (注 6)                                                                                                                                                                     |   |          | 600        |                   | ns             |

| t <sub>SU(DAT)</sub> | 数据建立时间           | (注 6)                                                                                                                                                                     |   | 100      |            |                   | ns             |

|                      | 用于停止的建立时间        | (注 6)                                                                                                                                                                     |   | 600      |            |                   | ns             |

|                      | 停止至起动总线空闲时间      | (注 6)                                                                                                                                                                     |   | 1.3      |            |                   | μs             |

| t <sub>R</sub>       | 上升时间             | SDA2 $\cdot$ C <sub>L</sub> = 200pF (图 3)<br>SDA $\cdot$ R <sub>L</sub> = 1.1k $\Omega$ $\cdot$ C <sub>L</sub> = 200pF (图 3)<br>SCL2 $\cdot$ C <sub>L</sub> = 200pF (图 1) | • | 40<br>40 |            | 350<br>250<br>250 | ns<br>ns<br>ns |

| t <sub>F</sub>       | 下降时间             | SDA2 $\cdot$ C <sub>L</sub> = 200pF (图 3)<br>SDA $\cdot$ R <sub>L</sub> = 1.1k $\Omega$ $\cdot$ C <sub>L</sub> = 200pF (图 3)<br>SCL2 $\cdot$ C <sub>L</sub> = 200pF (图 1) | • | 40<br>40 |            | 250<br>250<br>250 | ns<br>ns<br>ns |

| t <sub>PZL</sub>     | ON 使能时间          | ON † 至 SDA , $R_L = 1k\Omega$ , $C_L = 15pF$ (图 2)                                                                                                                        | • |          |            | 320               | μs             |

| t <sub>PLZ</sub>     | ON 停用时间          | ON↓至 SDA, R <sub>L</sub> = 1kΩ, C <sub>L</sub> = 15pF (图 2)                                                                                                               | • |          |            | 70                | ns             |

|                      | 由输入滤波器抑制之尖峰的脉冲宽度 | SDA, SDA2, SCL                                                                                                                                                            | • | 0        |            | 50                | ns             |

| 电源                   | '                |                                                                                                                                                                           |   |          |            |                   |                |

|                      | 上电时间             | ON ↑至 V <sub>S</sub> (最小值)<br>ON ↑至 V <sub>CC2</sub> (最小值)                                                                                                                | • |          | 0.2<br>0.2 | 1.5<br>2          | ms<br>ms       |

# 隔离特性 在TA = 25°C 时的指标。

| 符号                | 参数       | 条件                                                                                 | 最小值         | 典型值   | 最大值 | 单位                                     |

|-------------------|----------|------------------------------------------------------------------------------------|-------------|-------|-----|----------------------------------------|

|                   | 额定介质隔离电压 | 1 分钟 (从 1 秒测试推算)<br>1 秒 (注 8、9)                                                    | 5<br>6      |       |     | kV <sub>RMS</sub><br>kV <sub>RMS</sub> |

|                   | 共模瞬变抗扰度  | $V_{CC} = V_L = 0N = 5V \cdot \Delta V_{CM} = 1kV \cdot \Delta t = 33ns ( \ge 6 )$ | 30          | 50    |     | kV/μs                                  |

| V <sub>IORM</sub> | 最大连续工作电压 | (注 6、10)                                                                           | 1000<br>690 |       |     | V <sub>PEAK</sub><br>V <sub>RMS</sub>  |

|                   | 局部放电     | V <sub>PD</sub> = 1840V <sub>PEAK</sub> (注 8)                                      |             |       | 5   | pC                                     |

| CTI               | 相比漏电起痕指数 | IEC 60112 (注 6)                                                                    | 600         |       |     | V <sub>RMS</sub>                       |

|                   | 腐蚀深度     | IEC 60112 (注 6)                                                                    |             | 0.017 |     | mm                                     |

| DTI               | 隔离穿通距离   | (注 6)                                                                              |             | 0.2   |     | mm                                     |

|                   | 输入至输出电阻  | (注 6、8)                                                                            | 1           | 5     |     | TΩ                                     |

|                   | 输入至输出电容  | (注 6、8)                                                                            |             | 5     |     | pF                                     |

|                   | 爬电距离     | (注 6)                                                                              |             | 14.6  |     | mm                                     |

**注 1**: 高于「绝对最大额定值」部分所列数值的应力有可能对器件造成永久性的损害。在任何绝对最大额定值条件下暴露的时间过长都有可能影响器件的可靠性和使用寿命。

注 2: 所有流入器件引脚的电流为正; 所有电压均参考于 0V,除非特别注明。

注 3:一个内部并联稳压器把 V<sub>S</sub> 引脚电压限制在 10.65V 的最小值。把该引脚驱动至超过 10.65V 的电压有可能损坏器件。可通过一个把电流限制在小于50mA 的电阻器将此引脚安全地连接至较高的电压。

**注 4**:一个内部箝位把 DRAIN 引脚电压限制在 3.5V 的最小值。把此引脚驱动至超过该箝位的电压有可能损坏器件。可通过一个把电流限制在小于 2mA 的电阻器将该引脚安全地连接至较高的电压。

上连续工作有可能导致器件性能劣化或失效。热停机将导致内部产生之电源电压 ( $V_S$  和  $V_{CC2}$ ) 的损失和随后的 GATE 引脚关闭。热停机未在内部锁存,一旦结温下降并满足了启动条件,器件将自动重启。请注意,当发生电源故障时任何  $I^2C$  数据配置将丢失。

注 6:由设计提供保证,不经生产测试。

注7:最大数据速率由其他测量参数提供保证,并未直接测试。

注 8: 该器件被视作一款二端器件。测量于短接在一起的引脚组 A1 至 B7 和

短接在一起的引脚组 P1 至 T7 之间进行。

注 9: 额定介质绝缘电压不应解释为连续电压额定值。

注 10: DC 连续工作电压相当于峰值。

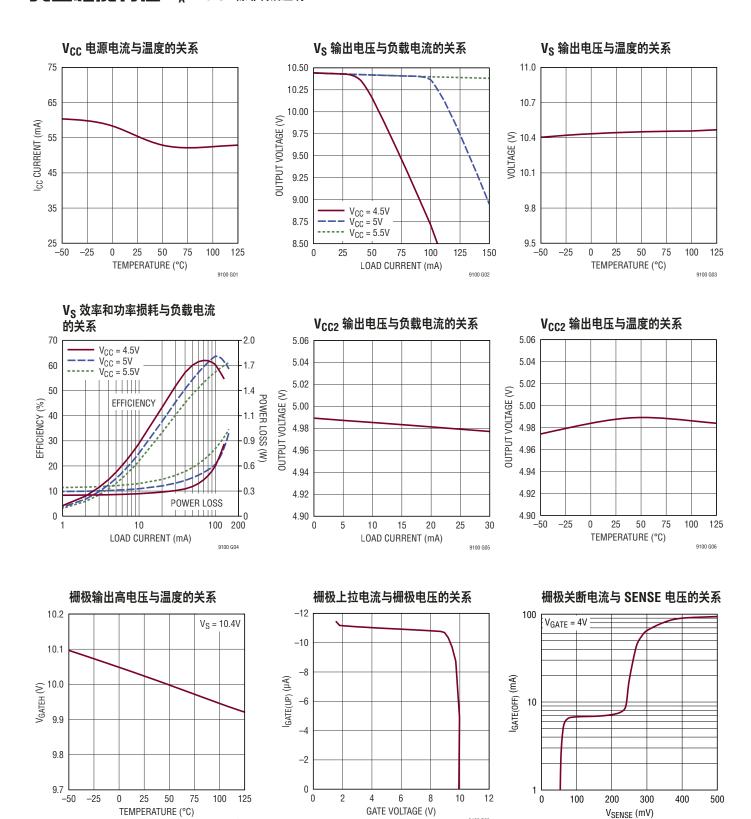

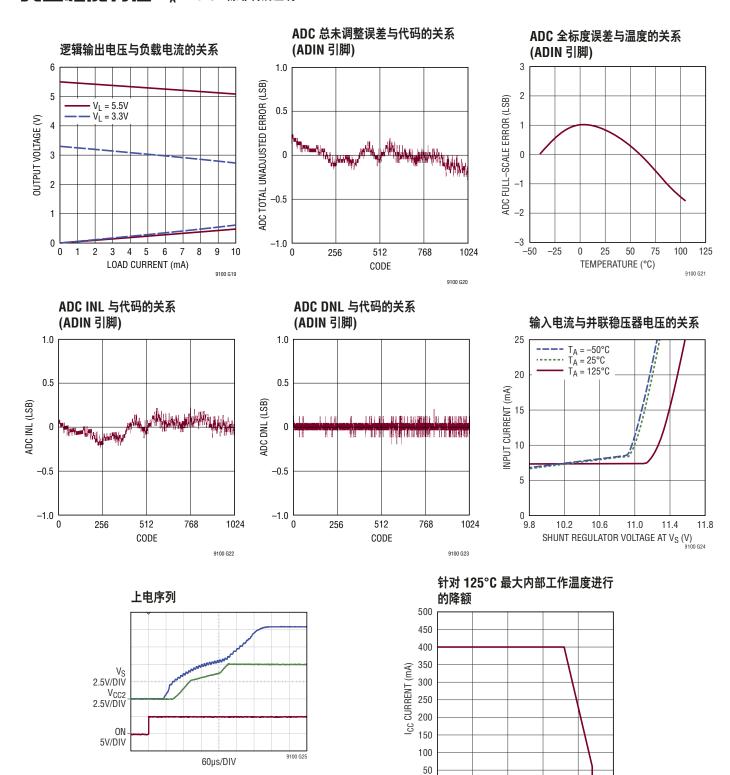

# 典型性能特征 TA = 25°C, 除非特别注明。

9100f

9100 G09

9100 G08

9100 G07

# 典型性能特征 TA = 25°C, 除非特别注明。

# 典型性能特征 TA = 25°C, 除非特别注明。

9100f

0 L

75

AMBIENT TEMPERATURE (°C)

100

125

# 引脚功能

### 逻辑侧

PG (A1): 电源良好状态输出,参考于 V<sub>L</sub> 和 GND。该逻辑 引脚在隔离侧电源开关接通之后拉至低电平并保持闭锁达两个定时器延迟 (当 GATE 达到约 9.5V 和 DRAIN 处在 V<sub>EE</sub> 的 1.77V 以内时)。电源良好输出在所有的 GATE 下拉过程中均被复位 (过压故障除外)。在发生隔离通信故障的情况下,该输出处于高阻抗状态。通信故障有可能由于极端电磁事件 (包括共模瞬变或电过应力) 而发生。如果未出现永久性损坏,则通信自动地重建。

ALERT (A2): 故障警报输出,参考于  $V_L$  和 GND。按照  $I^2C$  ALERT 寄存器的配置,当发生隔离侧故障时该逻辑引 脚拉至低电平。见「应用信息」。在发生隔离通信故障的情况下,该输出处于一种高阻抗状态。

EN (A3): GATE 使能输出,参考于  $V_L$  和 GND。一个上升沿启动隔离侧 GATE 引脚,而一个下降沿则关断隔离侧 GATE 引脚。该引脚还用于配置上电时  $I^2C$  CONTROL (D) 寄存器中 bit 3 (GATE\_CTRL) 的状态 (因此包括 GATE 引脚)。例如,倘若 EN 连接至高电平,则寄存器位 D3 在上电之后的一个定时器周期走高。同样,假如 EN 引脚连接至低电平,则 GATE 引脚在上电之后保持低电平,直到 EN 引脚变换至高电平为止。GATE 引脚可由  $I^2C$  通过寄存器位 D3 直接控制。一个高电平至低电平转换可清除任何驱动器 故障。不用时把该引脚连接至  $V_I$ 。

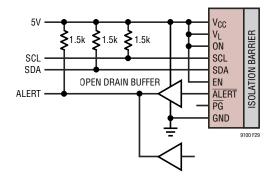

SDA (A4):串行  $I^2C$  数据引脚,参考于  $V_L$  和 GND。穿过 绝缘隔离连接至隔离侧 SDA2 引脚和可配置开关驱动器的 双向逻辑引脚。需要一个外部上拉电阻器或电流源。在发生隔离通信故障的情况下,该引脚处于一种高阻抗状态。不用时把该引脚连接至  $V_L$ 。

SCL (A5):串行  $I^2$ C 时钟引脚,参考于  $V_L$  和 GND。穿过绝缘隔离连接至隔离侧 SCL2 引脚和可配置开关驱动器的逻辑输入。需要一个外部上拉电阻器或电流源。不用时把该引脚连接至  $V_I$ 。

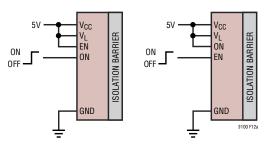

ON (A6): 模块使能引脚。使能穿过绝缘隔离的电源和数据通信。如果 ON 为高电平,则器件被使能,而且至隔离侧的电源和通信处于运行状态。如果 ON 为低电平,则逻辑侧保持在复位模式,所有的数字输出处于高阻抗状态,而且隔离侧无供电。ON 引脚可用于通过把 EN 连接至  $V_L$  来使能隔离侧电源开关驱动器。于是,ON 引脚的低电平至高电平转换将在内部隔离侧电源电压超过约 9V 并随后经历一个定时器延迟之后使能隔离侧栅极驱动器。不用时把该引脚连接至 $V_L$ 。

$V_L$  (A7):逻辑电源。用于引脚  $\overline{PG}$ 、 $\overline{ALERT}$ 、EN、SDA、SCL 和 ON 的接口电源电压。工作电压为 3V 至 5.5V。在内部利用  $1\mu F$  电容进行旁路。

GND (B1 至 B5): 电路地。

$V_{CC}$  (B6、B7): 隔离电源转换器电源电压。工作电压为 4.5V 至 5.5V。在内部利用  $1\mu$ F 电容进行旁路。如果  $V_S$  由一个外部电压驱动,则可把该引脚置于不连接状态或接地。

### 隔离侧

$\overline{\textbf{PG2}}$  (P1): 电源良好状态输出,参考于  $V_{CC2}$  和  $V_{EE}$ 。该逻辑引脚在隔离侧电源开关接通之后拉至低电平并保持闭锁达两个定时器延迟 (当 GATE 达到约 9.5V 和 DRAIN 处在  $V_{EE}$  的 1.77V 以内时)。电源良好输出在所有的 GATE 下拉过程中均被复位 (过压故障除外)。在内部经过一个 10k 电阻器连接至  $V_{CC2}$ 。

ALERT2 (P2): 故障警报输出,参考于  $V_{CC2}$  和  $V_{EE}$ 。按照  $I^2C$  ALERT 寄存器的配置,当发生隔离侧故障时该逻辑引 脚被拉至低电平。见「应用信息」。在内部经过一个 10k 电阻器连接至  $V_{CC2}$ 。

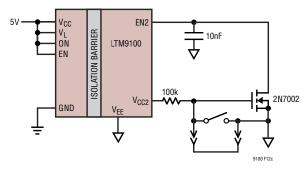

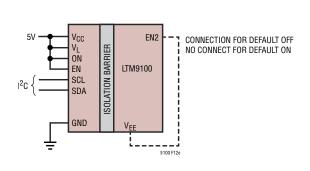

EN2 (P3): 使能输出,参考于  $V_{CC2}$  和  $V_{EE}$ 。通过绝缘隔离和 4k 电阻器连接至逻辑侧 EN 引脚和连接至开关驱动器的逻辑输出。EN2 引脚可以从外部驱动,见「应用信息」。在内部通过 4k 和 10k 电阻器连接至  $V_{EE}$ 。

**SDA2 (P4)**:串行  $I^2C$  数据引脚,参考于  $V_{CC2}$  和  $V_{EE}$ 。穿过绝缘隔离连接至逻辑侧 SDA 引脚和连接至开关驱动器的双向逻辑引脚。可实现  $I^2C$  总线扩展。利用一个 1.8mA 电

# 引脚功能

流源把输出偏置在高电平。在发生隔离通信故障的情况下该 输出默认为高电平状态。

SCL2 (P5):串行  $I^2C$  时钟输出,参考于  $V_{CC2}$  和  $V_{EE}$ 。穿过绝缘隔离连接至逻辑侧 SCL 引脚和连接至开关驱动器的逻辑输出。可实现  $I^2C$  总线扩展。时钟是单向的 (从逻辑侧至隔离侧)。在发生隔离通信故障的情况下,该输出默认为高电平状态。

PGIO (P6):通用输入/输出。逻辑输入和漏极开路输出。默认设置为输出,该输出在 PG 引脚走低之后的两个定时器延迟拉至低电平,以表示第二个电源良好输出。根据表 4进行配置。

$V_S$  (P7): 标称值为 10.4V 的隔离式电源输出电压。在内部由一个隔离式 D C / D C 转换器从  $V_{CC}$  产生并调节至 10.4V。如果  $V_{CC}$  未连接或接地,则  $V_S$  可以由一个外部电源驱动。如果从外部驱动,则通过一个降压电阻器把该引脚连接至一个正电源,见「应用信息」。一个内部并联稳压器把  $V_S$  ( $V_Z$ ) 箝位在 11.2V。一个欠压闭锁 (UVLO) 电路把GATE 保持在低电平,直到  $V_S$  高于 9V 为止。在内部利用  $1\mu F$  电容进行旁路。

V<sub>EE</sub> (R1 至 R3, R5 至 R7): 隔离电路共用。

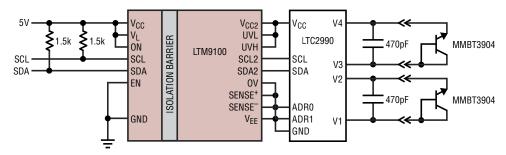

**ADRO、ADR1 (R4、S4)**:串行总线地址输入,参考于  $V_{CC2}$  和  $V_{EE}$ 。把这些引脚连接至  $V_{EE}$ 、 $V_{CC2}$  或浮置可配置 9 个可用地址之一。见「应用信息」中的表 1。

**SENSE**<sup>-</sup> (S1): 负电流限制检测输入。用于外部电流检测电阻器  $(R_S)$  的开尔文 (Kelvin) 连接。在内部利用 220pF 电容进行滤波。

**SS (S2)**: 软起动输入。该引脚用于在启动期间使浪涌电流渐变,从而实现对 di/dt 的控制。该引脚在内部连接至一个 220nF 电容器,可以增设附加的外部电容  $(C_{SS})$ 。一个内部  $10\mu$ A 电流源负责给内部和外部电容充电,产生一个电压斜坡。该电压被转换为电流以对 GATE 引脚进行充电并使输出电压斜坡下降。 SS 引脚在内部箝位至 2.56V,并把  $I_{GATE(UP)}$  限制为  $11.5\mu$ A,以及将  $I_{RAMP}$  限制为  $20\mu$ A。

TMR (S3): 延迟定时器输入。当电源良好输出下拉以及当在发生故障 (过压故障除外) 之后执行自动重试操作时,该引脚用于在上电时产生定时延迟。该引脚在内部连接至一个 47nF 电容器,可通过增设附加的外部电容 ( $C_{TMR}$ ) 以把标称延迟扩展至超过 12ms。 $10\mu A$  和  $5\mu A$  的内部上拉电流以及  $5\mu A$  和 12mA 的下拉电流把延迟周期配置为一个标称延迟  $t_D=12ms+256ms \bullet C_{TMR}/\mu F$  的倍数。针对上电以及欠压故障后自动重试的延迟与标称延迟相同。针对有序电源良好输出的延迟是标称延迟的两倍。针对过流故障后自动重试的延迟是标称延迟的 4 倍。

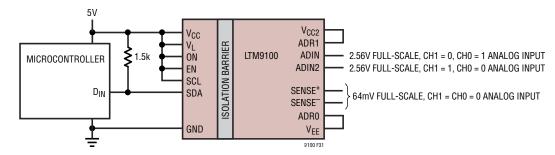

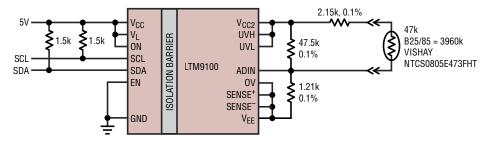

**ADIN2、ADIN (S5、S6)**: ADC 输入,参考于  $V_{EE}$ 。一个施加在这些引脚上的介于 0V 和 2.56V 之间的电压由内部模块 ADC 测量。不用时把该引脚连接至  $V_{FF}$ 。

$V_{CC2}$  (S7): 标称值为 5V 的隔离式电源输出电压。从  $V_S$  产生的线性稳定输出,具有一个 4.25V 的 UVLO 门限。该电压负责为隔离式数据转换器和逻辑控制电路供电。在内部利用  $1\mu F$  电容进行旁路。

SENSE+ (T1): 正电流限制检测输入。流过一个外部电流检测电阻器 (R<sub>S</sub>) 的负载电流由一个有源电流限制放大器监视并控制至 50mV/Rv。当  $V_{SENSE}$  达到 50mV 时,一个电路断路器定时器起动并在  $530\mu s$  之后切断开关。在发生灾难性短路的情况下,如果  $V_{SENSE}$  超过 250mV,则一个快速响应比较器立即下拉 GATE 引脚电平以关断 MOSFET。在内部利用 220pF 电容进行滤波。

GATE (T2): N 沟道 MOSFET 开关 (FET) 栅极驱动输出。该引脚的电平由一个内部电流源  $I_{GATE}$  (当 SS 引脚达到其箝位电压时为 11.5 $\mu$ A) 上拉。GATE 引脚保持低电平,直到  $V_S$  和  $V_{CC2}$  超过 UVLO 门限、EN 为高电平、UV 和 OV 条件得到满足和可调的上电定时器延迟结束为止。在由故障或欠压闭锁引起的关断期间,激活介于 GATE 和  $V_{EE}$  之间的一个 110mA 下拉电流。在内部利用 220pF 电容进行滤波。在发生隔离通信故障的情况下开关被切断。

DRAIN (T3):漏极检测输入。在该引脚和 FET 的漏极端子 之间连接一个外部电阻器。针对 50μA 标称电流来确定该电 阻器的大小,不要超过 2mA。该引脚上的电压在内部箝位

# 引脚功能

至 4V。当 DRAIN 引脚电压低于 1.77V 和 GATE 引脚电压约为 9.5V 时,电源良好输出在两个定时器周期之后确定。在内部利用 220pF 电容进行滤波。

RAMP (T4): 浪涌电流斜坡控制引脚。浪涌电流通过在RAMP 引脚和 FET 的漏极端子之间布设一个电容器 ( $C_R$ )进行调节。在启动时,GATE 引脚由  $I_{GATE(UP)}$  上拉,直到FET 开始接通为止。接着,一个电流  $I_{RAMP}$  流过  $C_R$  以使漏极电压斜坡下降。 $I_{RAMP}$  的数值由 SS 引脚电压控制。当SS 引脚达到其箝位电压 (2.56V) 时, $I_{RAMP}$  = 20 $\mu$ A。对于电容负载,FET 漏极电压 ( $V_{DRAIN}$ ) 的 RAMP 速率和负载电容器  $C_L$  设定浪涌电流: $I_{INRUSH}$  = ( $C_L/C_R$ )  $\bullet$   $I_{RAMP}$ 。在内部利用 10nF 电容进行滤波;见「应用信息」。

**OV (T5)**: 过压检测输入。把该引脚连接至一个从  $V_{EE}$  引出的外部阻性分压器。如果该引脚上的电压升至高于 1.77V,则 FET 关断。过压情况并不影响电源良好输出的状态。在内部利用 10nF 电容进行滤波。不用时把该引脚连接至  $V_{FE}$ 。

**UVH (T6)**:欠压高电平输入。把该引脚连接至一个从  $V_{EE}$  引出的外部阻性分压器。如果 UVH 引脚上的电压升至高于 2.56V 且 UVL 高于 2.291V,则允许 FET 接通。在内部利用 10nF 电容进行滤波。不用时把该引脚连接至  $V_{CC2}$ 。

UVL (T7): 欠压低电平输入。把该引脚连接至一个从  $V_{EE}$  引出的外部阻性分压器。如果 UVL 引脚上的电压降至低于 2.291V 且 UVH 低于 2.56V,则 FET 关断,电源良好输出 走高。把该引脚拉至低于 1.21V 使故障复位并允许 FET 重新接通。不用时把该引脚连接至  $V_{CC2}$ 。

# 方框图

# 测试电路

图 1:逻辑时序测量

图 2: ON 使能 / 停用时间

图 3: I<sup>2</sup>C 时序测量

### 概要

LTM9100 µModule 开关控制器提供了一个电气隔离坚固型驱动器接口,并且集成了去耦电容器。LTM9100 非常适合在那些接地点可采用不同电压的网络中使用。LTM9100中的隔离可阻断高电压差和免除接地环路,而且对于接地平面之间的共模瞬变具有极强的承受力。可在速度高达70kV/µs 的共模瞬变过程中保持无误操作,从而提供卓越的噪声隔离。

LTM9100 专为以一种受控的方式接通和关断电源电压而设计。在初始上电和时间延迟 (TMR) 之后的正常操作中, GATE 引脚接通一个 FET 以传输功率至负载。 GATE 引脚由一个输出电压  $(V_S)$  约为 10.4V 的内部隔离型 DC/DC 转换器供电。

一个连接至 SENSE 引脚的放大器用于提供过流和短路保护。它负责监视流过外部检测电阻器  $R_S$  的负载电流。在过流情况下,通过调节 GATE 把电流限制为  $50 \text{mV/R}_S$ 。如果过流情况的持续时间超过  $530 \mu \text{s}$ ,则 GATE 关断。

对 DRAIN 和 GATE 电压进行监视以确定 FET 是否得到全面强化。一旦 FET 成功接通,即在  $\overline{PG}$  和 PGIO 引脚上提供两个电源良好信号。它们提供多个负载的使能和排序。另外,PGIO 引脚还可针对一个通用输入或输出进行配置。

隔离侧逻辑电路由一个内部产生的 5V 电源 (V<sub>CC2</sub>) 供电。在接通 FET 之前,内部栅极驱动电源电压 V<sub>S</sub> 和 V<sub>CC</sub> 电压必须超过其欠压闭锁门限。此外,控制输入 UVH、UVL、OV 和 EN 也被监视。FET 保持断开状态,直到所有的启动条件都得到满足为止。

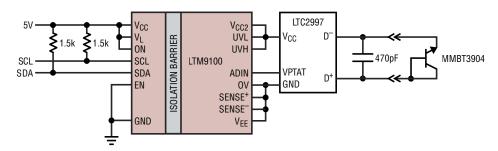

LTM9100 中内置了一个 10 位模数转换器 (ADC)。该 ADC 负责测量 SENSE 电压以及 ADIN2 和 ADIN 引脚上的电压,以供检测总线电压或温度等的辅助功能之用。

LTM9100 提供了一个 I<sup>2</sup>C 接口以对 ADC 数据寄存器进行 读操作。另外,它还允许主机对器件进行轮询并确定是否出现了某种故障。如果 ALERT 线被用作一个中断,则主机能够实时地对故障作出响应。两个三态引脚 ADRO 和 ADR1 用于设置 8 个可用的设备地址。

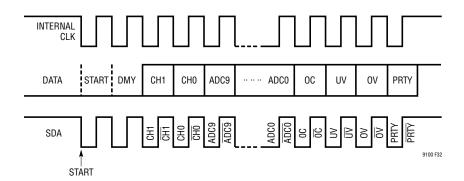

该接口还可针对一种单线广播模式进行引脚配置,可在无需对 SCL 线输送时钟信号的情况下通过 SDA 引脚把 ADC 数据和故障状态发送至主机。这种单线、单向通信能够简化系统设计。

LTM9100 非常适合分布式 DC 电源系统以及需要一个隔离型通信和控制接口的离线式电源转换器系统。图 4 示出了一款采用 LTM9100 的基本型 200W -48V 分布式电源应用

### μModule 技术

LTM9100 运用隔离器 µModule 技术以穿越一个绝缘隔离进行信号转换和供电。绝缘隔离任一侧上的信号被编码为脉冲并采用在 µModule 衬底中形成的无芯变压器横跨隔离边界进行转换。该系统拥有数据刷新、错误检查、故障安全停机功能和极高共模抗扰度,为双向信号隔离提供了坚固型解决方案。该 µModule 技术提供了把隔离式信号传输与多个稳压器和强大的隔离型 DC/DC 转换器整合在一个小型封装中的方法。

### DC/DC 转换器

LTM9100 内置一个包括变压器在内的全面集成 DC/DC 转换器,因而无需采用外部组件为隔离侧供电。逻辑侧包含一个以 2MHz 频率运行的全桥式驱动器,并 AC 耦合至单个变压器主边。一个串联 DC 隔离电容器用于避免发生由于驱动器占空比失衡所致的变压器饱和。变压器调整主边电压,并

用一个对称的倍压器进行整流。该拓扑可减少隔离侧接地点上的共模电压扰动,并且消除由副边失衡引起的变压器饱和。

DC/DC 转换器连接至一个低压差稳压器 (LDO) 以提供一个用于 GATE 驱动器电源的 10.4V 稳定输出  $(V_S)$ 。利用一个  $1\mu$ F 电容器对  $V_S$  进行内部去耦。

数据转换器和逻辑控制电路由一个从  $V_S$  电源获得 5V 的内部线性稳压器供电。该 5V 输出可在  $V_{CC2}$  引脚上提供以驱动外部电路 (高达 15mA 的负载电流)。利用一个  $1\mu F$  电容器对  $V_S$  进行内部去耦。

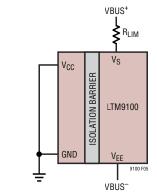

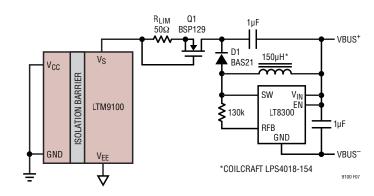

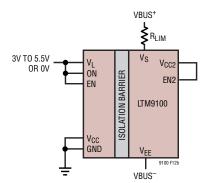

### 从总线为 LTM9100 供电

可以通过 V<sub>CC</sub> 引脚的浮置或接地来停用内部隔离型电源转换器。于是,可采用一个低压侧或高压侧电路 (取决于应用电路中 LTM9100 所处的位置) 从外部总线电压获得隔离式电源。

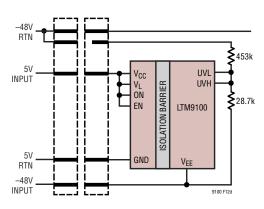

图 4:采用具电流和输入电压监视功能之 LTM9100 的 -48V/200W 低压侧热插拔控制器 (5.6A 电流限值, 0.66A 浪涌电流)

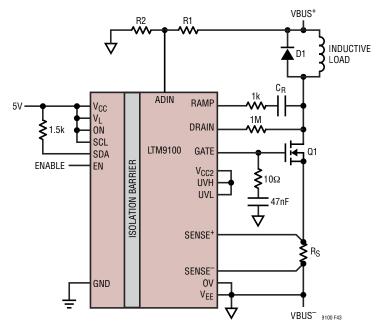

### 低压侧应用

$$R_{LIM} \le \frac{VBUS_{(MIN)} - V_{Z(MAX)}}{I_{S(EXT)} + I_{CC2(EXT)} + 10mA}$$

图 5: 从外部总线获得的隔离侧电源

$$P_{MAX} = \frac{\left[VBUS_{(MAX)} - V_{Z(MIN)}\right]^2}{R_{LIM}}$$

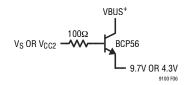

图 6:当为外部供电供电时 NPN 缓冲器消除了 R<sub>LIM</sub> 的过高功耗

### 高压侧应用

对于高压侧应用,有必要产生一个 > 总线电压 +  $V_Z$  (单位:伏特) 的电压,以在 FET 完全导通时即给 LTM9100 供电;漏极电压接近  $V_{EE}$ 。最初,LTM9100 可直接从总线供电,

直到 FET 漏极降至低于操作所需的最小  $V_S$  电压为止。请注意, $V_S$  电源电流流过负载,并将给任何负载电容充电,即使当 GATE 关断时也不例外。如果 LTM9100 被配置为在总线电压施加时即接通 GATE,那么这并不是问题。

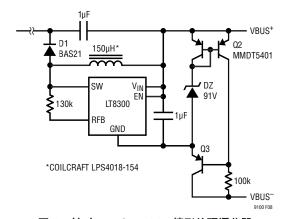

对于总线电压  $\leq$ 100V,可以使用图 7 所示的电路。该升压型转换器电路提供一个比总线电压高  $\sim$ 12V 的输出电压,并通过一个 ACL (耗尽型 MOSFET Q1,R<sub>LIM</sub>) 连接至 V<sub>S</sub>。对于总线电压 >100V,必需对升压型转换器的输入电压实施预调节,如图 8 所示。可以采用任何类型的升压转换器来提供升压电压:反激式、升压、充电泵等。晶体管 Q1、Q3和二极管 D1 必须根据总线电压和功率耗散进行选择。

图 7:针对 VBUS ≤ 100V 情形的 V<sub>S</sub> 电源

图 8:针对 VBUS > 100V 情形的预调节器

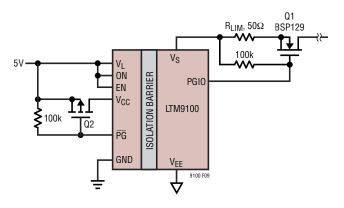

### 切换 PowerPath™ (电源路径)

于低压侧或高压侧配置,可随后使能内部 DC/DC 转换器并停用外部隔离侧转换器以最大限度地减少功率耗散。图 9中的电路采用电源良好信号以在主 FET 导通时自动地切换电源转换器通路。

图 9:外部至内部 PowerPath 切换

### V<sub>I</sub> 逻辑电源

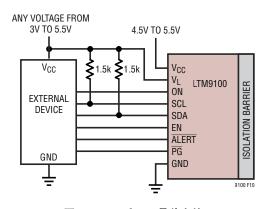

一个单独的逻辑电源引脚  $V_L$  使得 LTM9100 能够与任何  $3V \subseteq 5.5V$  的逻辑信号相连接,如图 10 所示。简单地把需要的逻辑电源连接至  $V_L$  即可。

在  $V_{CC}$  和  $V_L$  之间没有相关性;它们可以在处于其规定工作范围内的任何电压条件下同时工作,并以任何顺序进行排序。 $V_{CC}$  和  $V_L$  由  $1\mu F$  电容器在内部进行去耦。

图 10: V<sub>CC</sub> 和 V<sub>L</sub> 是独立的

### 安全地热插拔

由于集成了陶瓷去耦电容器,因此在那些插电到 LTM9100之电源 (V<sub>CC</sub> 或 V<sub>L</sub>) 的应用中必须谨慎从事。寄生电缆电感加上陶瓷电容器的高品质因数特性会引起大量的振铃,这有可能超过最大电压额定值并损坏 LTM9100。详细的讨论请参阅标题为「陶瓷输入电容器会引起过压瞬变」的「凌力尔特应用指南 AN88」(Application Note AN88)。

### 通道时序不确定性

利用输入和输出的编码和解码横跨隔离边界支持多个通道。 多达 3 个信号被组合成一个串行包并穿过绝缘隔离进行传输。传输所有 3 个位所需的时间为 50ns (典型值),并对一个信号在绝缘隔离对侧上多长时间改变一次设定限值。所用的方法给逻辑侧上的 SCL 和隔离侧上的 PG2 分配最高的优先级,这样在相关联的输出通道上就不存在抖动,只有延迟。这种抢占方案将在其他的隔离通道上产生一定量的不确定性。在这些低优先级通道上产生的脉宽不确定性通常为±6ns,但是,如果低优先级通道不是在同一个高优先级串行包内部进行编码的,则该不确定性有可能变至高达±44ns。

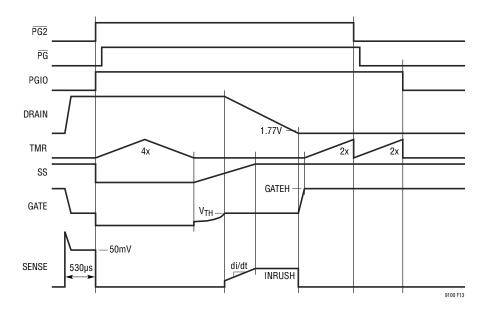

#### 初始上电和浪涌控制

在起动 FET 接通序列之前必须满足几个条件。首先, $V_S$  上 的电压必须超过其 9V 欠压闭锁电平。其次,内部电源  $V_{CC2}$  必须超过其 4.25V 欠压闭锁电平。这产生一个 100 $\mu$ s 至 160 $\mu$ s 的上电复位脉冲,在此期间 FAULT 寄存器位被清零,而 CONTROL 寄存器位则被设定或清零,如在寄存器部分中所述。在上电复位脉冲之后,UVH、UVL 和 OV 引脚上的电压必须满足 UVH > 2.56V、UVL > 2.291V 和 OV < 1.77V。在由连接至 TMR 引脚的内部和外部 ( $C_{TMR}$ ) 电容之组合设定的启动延迟期间上述条件必须全部满足。

$C_{TMR}$  用一个  $10\mu A$  的上拉电流进行充电,直至 TMR 上的电压达到 2.56V 为止。然后,用一个 12mA 电流对  $C_{TMR}$  进行快速放电。当 TMR 被拉至低于 75mV 时,初始延迟期满。启动延迟的持续时间由下式给出:

$$t_D \approx 12 \text{ms} + 256 \text{ms} \cdot \frac{C_{TMR}}{1 \mu F}$$

如果在启动延迟期满之前违反了任何上述条件,则  $C_{TMR}$  快速放电且接通序列重启。在整个启动延迟期间验证了所有的条件之后,接着检查 EN 引脚。如果该引脚为高电平,则 FET 将接通。否则, FET 将在 EN 引脚电平被提升或 CONTROL (D) 寄存器中的 bit 3 (GATE\_CTRL) 通过  $I^2C$ 接口 (当针对仅限  $I^2C$  控制进行配置时) 设定为 1 时接通。

接在 FET 接通序列后面的是用一个  $10\mu$ A 上拉电流给 SS 引脚上的一个内部和外部 ( $C_{SS}$ ) 电容器充电,而且,SS 上的电压 ( $V_{SS}$ ) 被转换为一个  $11.5\mu$ A •  $V_{SS}/2.56V$  的电流 ( $I_{GATE(UP)}$ ) 以提供 GATE 上拉。当 GATE 达到 FET 门限电压时,电流开始流过 FET,而且一个  $20\mu$ A •  $V_{SS}/2.56V$  的电流 ( $I_{RAMP}$ ) 从 RAMP 引脚流出,并流过一个连接在RAMP 和漏极电压之间的外部电容器 ( $C_{R}$ )。SS 电压被箝位至 2.56V,这对应于  $I_{GATE(UP)}$  =  $11.5\mu$ A 和  $I_{RAMP}$  =  $20\mu$ A。RAMP 引脚电压被调节在 1.1V,而  $V_{DRAIN}$  的斜坡速率则决定了对于电容性负载的浪涌电流:

$$I_{INRUSH} = 20\mu A \cdot \frac{C_L}{C_R}$$

V<sub>SS</sub> 的斜坡速率决定了浪涌电流的 di/dt:

$$\frac{dI_{INRUSH}}{dt} = 20\mu A \cdot \frac{C_L}{C_R} \cdot \frac{1\mu F}{256ms \cdot (C_{SS} + 220nF)}$$

如果在外部没有  $C_{SS}$ ,则 SS 在大约 56ms 时间里从 0V 斜坡上升至 2.56V。

当  $V_{DRAIN}$  斜坡下降至  $V_{EE}$  时, $I_{GATE}$  返回 GATE 引脚并把 GATE 上拉至  $V_{GATEH}$ 。图 11 示出了 LTM9100 的启动序 列。

在带电电路板插入或输入电源阶跃期间,一个内部箝位电路接通以把 RAMP 引脚保持在低电平。电阻器  $R_R$  和一个连接至  $V_{EE}$  的内部 10nF 电容器用于抑制 RAMP 引脚上的噪声。为了执行正确的操作, $R_R \bullet C_R$  不应超过  $50\mu s$ 。可在 RAMP 和  $V_{EE}$  之间增设额外的电容以提供附加的噪声滤波。

### 电源状态良好监视器

当 FET 两端的电压降至低于 1.77V 和 GATE 拉至高于约 9V 时,锁存一个内部电源良好信号并起动接连的两个延迟周期,如图 11 所示。当第一个持续时间为  $2t_D$  的延迟周期期满时, $\overline{PG}$  和  $\overline{PG}$  引脚拉至低电平作为电源良好信号。当第二个延迟周期 ( $2t_D$ ) 期满时,PGIO 引脚拉至低电平以作为另一个电源良好信号。 $2t_D$  定时器延迟通过用一个  $5\mu A$  电流对 TMR 上的电容进行充电,并在 TMR 达到 2.56V 时用 12mA 进行放电来获得。 $\overline{PG}$  和 PGIO 上的电源良好信号在所有的 FET 关断之情况下 (过压故障除外) 复位。

#### 关断序列和自动重试

在任何下列情况下,均通过用一个 110mA 电流下拉 GATE 来关断 FET,而且用 12mA 电流对 SS 和 TMR 引脚上的电容进行放电。

- 1. EN (或 EN2) 引脚为低电平或寄存器位 D3 被设定为 0。

- 2. UVL 上的电压低于 2.291V, 而且 UVH 上的电压低于 2.56V (欠压故障)。

- 3. OV 上的电压高于 1.77V (过压故障)。

- 4. V<sub>S</sub>上的电压低于 8.5V (V<sub>S</sub>欠压闭锁)。

- 5. V<sub>CC2</sub> 上的电压低于 4.25V (V<sub>CC2</sub> 欠压闭锁)。

- V<sub>SENSE</sub> > 50mV, 而且该条件的持续时间长于 530μs (过流故障)。

对于情况 1、4、5,在故障情况被清除之后,LTM9100 将自动进入 FET 接通序列,如前文所述。

对于故障情况 2、3、6 中的任何一种,FET 断开模式均可由 CONTROL 寄存器中对应的自动重试位进行设置。如果自动重试位被设定为 0,则在出现故障情况时 FET 即被闭锁。假如自动重试位被设定为 1,那么在故障情况被清除之后,延迟定时器起动。在定时器期满之后,FET 进入自动重

试模式且 GATE 被上拉。跟随在欠压故障之后的自动重试延迟之持续时间为  $t_D$ 。接在过流故障之后的自动重试延迟持续  $4t_D$  以提供额外的冷却时间。过压故障之后的自动重试没有延迟。自动重试控制位及其在上电时的默认设置列于表 4。请注意,LTM9100 在过流故障之后默认至闭锁。

图 11:LTM9100 接通序列

### 接通 GATE 引脚 (外部 FET)

采用 ON、EN、EN2、UV/OV 或 PGIO 引脚连同  $I^2C$  端口可实现多种接通 / 关断方法。EN 引脚可与逻辑输入或浮动开关触点很好地配合工作; $I^2C$  控制用于那些电路板只在一个中央处理器的指令下工作的系统,而且 ON 引脚适用于具有低备用电流要求的系统。UV (UVH、UVL) 和 OV 引脚适用参考于  $V_{EE}$  的信号。PGIO 不直接控制任何东西,但是可用于连接检测或其他重要信号的  $I^2C$  监视。

接通 / 关断控制可在有或没有  $I^2C$  干预的情况下完成。即使在自主运作时, $I^2C$  端口仍然能够对 GATE 输出实施控制,但是视它们连接方式的不同,EN、EN2 和 ON 可随后推翻由  $I^2C$  设定的条件。UV、OV 和其他故障条件可根据需要夺取控制权以关断 GATE 输出,而不管 EN、EN2、ON 或  $I^2C$  端口是什么状态。图 12 示出了 LTM9100 之接通 / 关断控制的 5 种配置。

具隔离的逻辑控制:图 12a 示出了采用逻辑信号控制的应用。ON 引脚或 EN 引脚的上升沿和下降沿 (引脚交替连接至高电平) 接通和关断 GATE 输出。ON 的上升沿控制由电源转换器接通时间和一个  $t_D$  周期导致了 GATE 信号的延迟,而下降沿也将被转换器放电时间 (储存能量) 以及  $V_S$  和  $V_{CC2}$  上的电源负载所延迟。GATE 将立即响应 EN 引脚上的变化。EN 引脚的状态可通过  $I^2C$  端口在寄存器位 D3 上进行检查或覆盖。每当  $V_{CC2}$  降至低于其 UVLO 门限时,寄存器位 D3 被设定为低电平。GATE 引脚输出的状态由寄存器位 A7 (GATE\_STAT) 指示,这等同于寄存器位 D3 且没有 UV、OV 和其他故障。

自举电源连接:图 12b 示出了在隔离侧上获得控制电源的低压侧应用。当 EN2 在隔离侧上连接至高电平时,GATE在加电之后上升一个  $t_D$  周期。逻辑电源  $(V_L)$  或 ON 引脚可在施加总线电压之前或之后变换 (假如 EN 引脚连接至高电平),并不会干扰 GATE 信号。

喷射器开关或通路连接检测:浮动开关触点,或一个连接检测环路与 EN 或 EN2 引脚很好地配合工作。图 12c 示出了采用 EN2 引脚的该配置,并包括一个防反跳延迟。

至 RTN 的短路引脚:图 12d 采用 UV 分压器串以检测电路板插入。另外,短路引脚连接还可通过连线以与 ON 或 EN 引脚协同工作。

仅限  $I^2C$  的控制:如欲闭锁 EN 和 ON,则采用图 12e 中示出的配置并用寄存器位 D3 来控制 GATE 引脚。该电路在上电时默认为关断 (EN2 连接至  $V_{EE}$ )。如需默认为接通,则不要连接 EN2。PGIO 引脚可用作一个输入,以监视连接检测或其他控制信号。通过把寄存器位 D6 和 D7 设定为高电平将 PGIO 配置为一个输入;其输入状态存储在寄存器位 A6。

### 过流保护和过流故障

LTM9100 具有针对短路和过流情况的两级保护。负载电流由 SENSE 引脚和电阻器 R<sub>S</sub> 监视。对于 SENSE 上的电压有两个不同的门限:用于占用有源电流限制环路和起动一个530µs 电路断路器定时器的 50mV,和用于在发生灾难性短路或输入阶跃时提供快速 GATE 下拉以限制峰值电流的250mV。

在过流情况下,当  $R_S$  两端的电压降超过 50 mV 时,电流限制环路被占用且一个内部  $530 \mu s$  电路断路器定时器被起动。 电流限制环路维持 GATE 引脚电平以保持一个  $50 mV/R_S$  的恒定输出电流。当电路断路器定时器期满时,通过用一个 110 mA 电流下拉 GATE 来关断 FET,SS 和 TMR 引脚上的电容器被放电,且电源良好信号被复位。此时,过流存在位 A2 和过流故障位 B2 被复位,而且电路断路器定时器被复位。

12(a) 逻辑输入控制

12(b) 自举电源连接

12(c) 电路板插入时的接触防反跳延迟,适用于喷射器开关或通路型连接检测

12(d) 至 RTN 的短路引脚连接检测

12(e) 限用 I<sup>2</sup>C 的控制

图 12:LTM9100 的接通 / 关断控制

在 FET 被关断之后,过流情况寄存器位 A2 被清零。如果过流自动重试寄存器位 D2 已被设定,则开关将在一个 4t<sub>D</sub> 的冷却时间之后自动重新接通。否则,FET 将保持断开状态直到过流故障寄存器位 B2 被复位为止。当过流故障位被复位时(见「使故障复位」),允许 FET 在一个 4t<sub>D</sub> 的延迟之后再次接通。与过流故障相关联的 4t<sub>D</sub> 冷却时间将不被任何其他故障情况所中断。见图 13 以了解 LTM9100 在后随自动重试的过流情况下的工作。

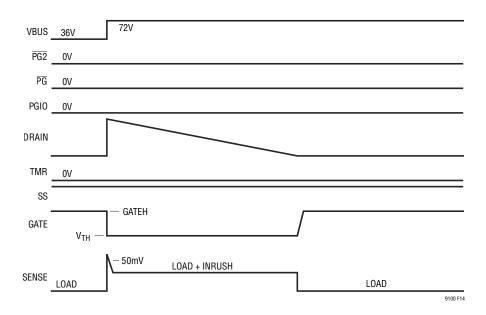

在负载侧上出现低阻抗短路,或在电池更换期间发生输入阶跃的情况下,电流过冲是不可避免的。一个具有 250mV 门限的快速 SENSE 比较器负责检测过冲并立即把 GATE 拉至低电平。一旦 SENSE 电压降至 50mV,电流限制环路随即接管并维持电流,如前文所述。如果短路情况的持续时间超过 530µs,则 FET 停机且过流故障被记录。

在输入阶跃的情况下,在内部箝位把 RAMP 引脚下拉至 1.1V 之后,浪涌控制电路接管,而且在电路断路器定时器 期满之前使电流限制环路脱离工作状态。从此刻起,器件的工作和在初始启动过程中相同:以  $I_{RAMP}$  和  $C_R$  设定的速率使  $V_{DRAIN}$  斜坡下降,随后是 GATE 上拉。在整个输入阶跃序列中, $\overline{PG}$  和 PGIO 引脚、TMR 引脚、和 SS 引脚上的电源良好信号不被中断。图 14 中的波形示出了 LTM9100 是怎样响应输入阶跃的。

请注意,电流限制门限应设定得足够高以容纳负载电流与浪涌电流之和,从而避免在发生输入阶跃的情况下占用电流限制环路。浪涌电流的最大值由下式给出:

$$I_{INRUSH} \le 0.8 \bullet \frac{45mV}{R_S} - I_{LOAD}$$

式中的因子 0.8 用作一个与最小 SENSE 门限 (45mV) 相组合的最坏情况裕度。

如图 4 所示,采用连接在 GATE 和  $V_{EE}$  之间的电容器  $C_G$  和一个串联电阻器  $R_G$  (10 $\Omega$ ) 对有源电流限制电路实施补偿。

$C_G$  的推荐值为 47nF。这个数值对于大多数 FET (Q1) 都应该是有效的。

### 过压故障

当 OV 引脚电平升至高于其 1.77V 门限时出现过压故障。 这立即切断 FET,设定过压存在寄存器位 AO 和过压故障寄存器位 BO,并下拉 SS 引脚电压。请注意,电源良好信号不受过压故障的影响。如果 OV 引脚电平随后跌回到门限以下,则 FET 将被允许立刻 (没有延迟) 重新接通,除非已经通过清零寄存器位 DO 停用了过压自动重试功能。

### 欠压比较器和欠压故障

LTM9100 提供了两个欠压引脚 (UVH 和 UVL),用于可调 UV 门限和迟滞。UVH 和 UVL 引脚具有以下的准确门限:

对于 UVH 逐渐上升,V<sub>UVH(TH)</sub> = 2.56V,接通 对于 UVL 逐渐下降,V<sub>UVL(TH)</sub> = 2.291V,关断

UVH 和 UVL 引脚具有一个  $\delta V_{UV}$  (15mV 典型值) 的迟滞。在逐渐上升或下降的输入电源中,欠压比较器以这样一种方式工作:UVH 和 UVL 引脚均必须超过其门限,比较器输出才会改变状态。

UVH、UVL和 OV 门限比专为匹配 43V 至 71V 的标准电信工作范围以及 4.5V UV 迟滞 (当 UVH和 UVL 连接在一起时,如在图 4 中那样)而设计,此时参考于 UVL 引脚的内置 UV 迟滞为:

$\Delta V_{UV(HYST)} = V_{UVH(TH)} - V_{UVL(TH)} = 0.269V$

如在图 4 中那样采用 R1 =  $11.8k \cdot R2 = 16.9k$  和 R3 = 453k 可提供一个 43.0V 至 70.7V 的典型工作范围,以及 38.5V 的欠压停机门限和 72.3V 的过压停机门限。

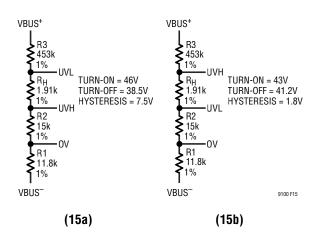

通过用一个电阻器 R<sub>H</sub> 把 UVH 和 UVL 引脚隔开以调整 UV 迟滞 (图 15)。如欲增大 UV 迟滞,则应如图 15a 所示把 UVL 抽头布设在高于 UVH 抽头的地方。如需减小 UV 迟

图 13:过流故障和自动重试

图 14:36V 至 72V 阶跃响应

滞,则如图 15b 所示把 UVL 抽头放置在 UVH 抽头的下方。参考于 UVL 引脚的 UV 迟滞由下式给出:

对于

$$V_{UVL} \ge V_{UVH}$$

$$V_{UVL(HYST)} = V_{UV(HYST)} + 2.56V \bullet \frac{R_H}{R1 + R2}$$

或对于  $V_{UVL} < V_{UVH}$

$$V_{UVL(HYST)} = V_{UV(HYST)} - 2.56V \bullet \frac{R_H}{R1 + R2 + R_H}$$

对于  $V_{UVL}$  <  $V_{UVH}$  , 允许的最小 UV 迟滞是 UVH 和 UVL 上的最小迟滞:当  $R_{H(MAX)}$  = 0.11 • ( $R_1$  +  $R_2$ ) 时  $\delta V_{UV}$  = 15mV。

图 15:用于增大 (15a) 和减小 (15b) 迟滞的欠压门限调整

LTM9100 的设计可保护 UV 比较器免受颤振,即使当  $R_H$  大于  $R_{H(MAX)}$  时也不例外。

当 UVL 引脚电平降至低于 2.291V 和 UVH 引脚降至低于  $2.56V - \delta V_{UV}$  时,出现欠压故障。这启动 FET 关断并设定 欠压存在寄存器位 A1 和欠压故障寄存器位 B1。  $\overline{PG}$  和 PGIO 引脚上的电源良好信号也被复位。

当 UVH 引脚电平升至高于 2.56V 和 UVL 引脚电平升至高于 2.291V +  $\delta V_{UV}$  时,欠压存在寄存器位 A1 被清零。在一个  $t_D$  延迟之后,FET 将重新接通,除非已经通过清零寄存器位 D1 停用了欠压自动重试功能。

当给器件加电时,如果在  $V_{CC2}$  超过其欠压闭锁门限 (4.25V) 之后 UVL 低于 2.291V 门限且 UVH 低于 2.56V  $-\delta V_{UV}$ ,则将在故障寄存器中记录一个欠压故障。

由于从一个离散电阻值表 (1% 精度电阻器以 2% 为增量, 0.1% 精度电阻器以 1% 为增量)进行选择时所做的折衷, 为每个引脚采用单独的分压器将实现最好的 OV 和 UV 准确度。这把电阻器的总数从 3 个或 4 个增至多达 6 个,但是最大限度地提高了准确度,极大地简化了计算,并且便于实施运行时变更以在不对电路板做任何改动的情况下适应多种标准或定制。

### FET 短路故障

如果在 FET 处于关断状态时数据转换器测量到一个大于或等于 2mV 的电流检测电压,则将报告一个 FET 短路。该条件设定了 FET\_STAT 寄存器位 A5 和 FET\_FAULT 寄存器位 B5。

### 外部故障监视器

当被配置为一个通用输入时,PGIO 引脚可提供熔丝烧断等外部故障情况的监视。在该场合中,如果 PGIO 引脚上的电压高于 1.25V,则寄存器位 A6 和寄存器位 B6 均被设定,但是没有与此故障相关联的警报位。PGIO 上的某种外部故障条件不会直接影响 GATE 控制功能。

#### 故障警报

当 FAULT (B) 寄存器中的任何故障位被设定时,可通过设定 ALERT (C) 寄存器中的合适位来产生一个任选的总线警报。这使得只有选定的故障才能产生警报。在上电时,默认的状态是在发生故障时不发送警报。如果某个警报被使能,则对应的故障将致使 ALERT 和 ALERT 引脚被拉至低电平。在总线主控制器广播了警报响应地址之后,LTM9100将利用其在 SDA 线上的地址作出响应并释放 ALERT,如图 30 所示。如果在两个同时利用其地址作出响应的比TM9100之间存在冲突,则具有较低地址的那个器件赢得

仲裁并首先响应。如果器件被总线主控器寻址,那么 ALERT 线也将被释放。

一旦已经针对某个故障发布了 ALERT 信号,那么在 FAULT 寄存器指示出现了一个不同的故障、或原故障被清除而又再度出现之前,它将不被重新拉至低电平。请注意,这意味着重复或持续的故障将不产生警报,直到相关联的 FAULT 寄存器位已被清零为止。

### 使故障复位

利用以下任何条件使故障复位。首先,把「0」写入 FAULT 寄存器将清零相关联的故障位。其次,当 EN2 引脚或寄存器位 D3 从高电平变至低电平时,或如果 V<sub>CC2</sub> 降至低于其 4.25V 的欠压闭锁门限,则整个 FAULT 寄存器被清零。另外,把 UVL 引脚拉至低于其 1.21V 复位门限也清零整个 FAULT 寄存器。当 UVL 引脚被拉回至 1.21V 以上但低于 2.291V 时,欠压故障寄存器位 B1 被设定 (如果 UVH 引脚低于 2.56V)。这可以通过在变换 UVL 引脚电平以使故障复位时把 UVH 引脚保持在高于 2.56V 来避免。

具有仍然存在之关联条件的故障位 (如 STATUS (A) 寄存器中所示) 不能清零。当执行自动重试时,FAULT 寄存器将不被清零。当自动重试功能被停用时,寄存器位 B0 (过压)、B1 (欠压) 或 B2 (过流) 的存在把 FET 保持于关断状态。在故障位被清零且一个  $t_D$  延迟期满之后,FET 将重新接通。请注意,如果通过  $I^2C$  写入一个「0」清零了过压故障寄存器位 B0,则允许 FET 重新接通 (无需经过一个延迟)。假如自动重试被使能,则寄存器位 A0、A1 或 A2 中的一个高值将保持 FET 关断,而且 FAULT 寄存器被忽略。随后,当寄存器位 A0、A1 和 A2 被清零时,FET 被允许重新接通。

### 数据转换器

LTM9100 纳入了一个连续监视 (顺序为) SENSE、ADIN2 和 ADIN 上的三个不同电压的 10 位  $\Delta\Sigma$  模数转换器 (ADC)。 $\Delta\Sigma$  架构内在地于测量周期中对信号噪声进行平均处理。SENSE+ 和 SENSE- 引脚之间的电压以一个 64mV

全标度和 62.5µV 分辨率进行监视,且数据被存储在寄存器 E 和 F 中。ADIN 和 ADIN2 引脚以一个 2.56V 全标度和 2.5mV 分辨率进行监视。用于 ADIN2 引脚的数据被存储在 寄存器 G 和 H 中。用于 ADIN 引脚的数据存储在寄存器 I 和 J 中。

寄存器 E、F、G、H、I 和 J 中的结果以 7.3Hz 的频率更新。设定寄存器位 D5 将唤醒一种测试模式,该模式暂停这些寄存器的更新,以便对它们进行用于软件测试的读写操作。通过刚好在读取 ADC 数据寄存器之前唤醒该测试模式,被分离在两个寄存器中的 10 位数据实现同步化。

ADIN 和 ADIN2 引脚可用于监视输入和输出电压或控制器 的温度  $^{,}$  如图 33 至 35 、图 39 、图 40 、图 43 和图 45 所示。

### 配置 PGIO 引脚

表 4 描述了采用寄存器位 D6 和 D7 的 PGIO 引脚的可能状态。在上电时,默认状态是让 PGIO 引脚在第二个电源良好信号就绪时拉至低电平。PGIO 引脚的其他用途是当第二个电源良好信号就绪时变至高阻抗,一个通用输出和一个通用输入。当 PGIO 引脚被配置为一个通用输出时,寄存器位 C6 的状态被传递至该引脚。当它被配置为一个通用输入时,倘若 PGIO 上的输入电压高于 1.25V,则寄存器位 A6 和 B6 被复位。假如 PGIO 上的输入电压随后降至低于 1.25V,则寄存器位 A6 被清零。寄存器位 B6 可通过使 FAULT 寄存器复位来清零,如前文所述。

### 设计步骤

1. 采用应用的负载电流  $(I_{LOAD})$  要求,用 45 mV 的最小 SENSE 门限电压来计算检测电阻器  $(R_S)$  的阻值。

$$R_{S} = \frac{45mV}{I_{LOAD}}$$

$$I_{MAX} = \frac{55mV}{R_{S}}$$

2. 对于一个电容性负载  $(C_L)$ , 通过计算斜坡电容器  $(C_R)$  的数值来设定浪涌  $(I_{INBUISH})$  电流。

$$C_R = C_L \bullet \frac{I_{RAMP}}{I_{INRUSH}} = C_L \bullet \frac{20\mu A}{I_{INRUSH}}$$

浪涌电流和斜坡电容器可能需要根据选定的开关安全工作区 (SOA) 进行迭代。

对于阻性或容性负载,接通电压的变化率采用下式计算:

$$\frac{dV}{dt} = \frac{I_{RAMP}}{C_{R}} = \frac{20\mu A}{C_{R}}$$

3. 选择一个 N 沟通开关 (Q1); MOSFET、SiC MOSFET、IGBT等。开关选择基于最大工作电压 (具有裕量)、ON 状态功率耗散 (I<sub>MAX</sub><sup>2</sup> • R<sub>DSON</sub> 或 I<sub>MAX</sub> • V<sub>CESAT</sub>)和 SOA。最大 ON 状态功率耗散 (P<sub>ON</sub>)采用最大负载电流和最大期望开关 R<sub>DSON</sub>来计算。在 125°C 时的最大开关电阻通常为产品手册电特性表中给出的 25°C 结温下之最大 ON 电阻的 2 倍。

$$P_{ON} = I_{MAX}^2 \cdot R_{DSON(125^{\circ}C)}$$

针对开关 SOA 必须考虑的多种情形包括:正常浪涌接通、短路接通、输入电压阶跃、和接通时的短路。为了在多家制造商和工作状况之间评估开关 SOA,可通过计算  $P^2t$  或  $P\sqrt{t}$  并加以比较来对计算数据和产品手册 SOA 曲线的恒定功率 (对角地逐渐减小) 部分进行归一化。专门针对线性或 DC 操作进行设计和特性分析的开关是最合适的。这些通常是采用平面工艺 (而不是高密度垂直工艺 [例如:沟槽]) 制造的开关。

a. 正常开关接通功率耗散  $(P_{TON})$  包括一个从 VBUS 至  $\approx 0V$  的电压斜坡和恒定充电电流  $I_{INRUSH}$ 。假设没有负载电流且忽略慢速起动:

$$P_{TON} = \frac{VBUS \cdot I_{INRUSH}}{2}$$

$$t_{INRUSH} = \frac{C_R \cdot VBUS}{I_{RAMP(min)}} = \frac{C_L \cdot VBUS}{I_{INRUSH}}$$

$$P\sqrt{t} = P_{TON}\sqrt{t_{INRUSH}}$$

b. 负载短路接通功率耗散  $(P_{SCTON})$  包括一个至  $I_{MAX}$  的电流斜坡,这是 MOSFET 跨导周期  $(t_{fs})$ ,后随  $I_{MAX}$  下的电路断路器周期  $(t_{CB})$ ,各在恒定总线电压条件下。忽略慢速起动:

$$P_{fs} = \frac{VBUS \cdot I_{MAX}}{2}$$

$$P_{CB} = VBUS \cdot I_{MAX}$$

$$t_{fs} = \frac{\left(C_G + C_{iss(max)}\right) \cdot 2 \cdot I_{MAX}}{I_{GATE(min)} \cdot 9 \cdot 9 \cdot 9 \cdot 9 \cdot 1}$$

式中的  $I_{GATE(min)}$  = 7.5 $\mu$ A ,  $C_{iss}$  是 MOSFET 栅极输入电容,而  $g_{fs}$  是 MOSFET 正向跨导。

计算整个事件过程中的总体功率耗散:

$$P_{SCTON} = \frac{P_{fs} \cdot t_{fs} + P_{CB} \cdot t_{CB}}{t_{fs} + t_{CB}}$$

$$P\sqrt{t} = P_{SCTON} \sqrt{t_{fs} + t_{CB}}$$

c. 针对输入阶跃的功率耗散 ( $P_{STEP}$ ) 包括一个从  $V_{STEP}$  至  $\approx$  0V 的电压斜坡和  $I_{MAX} = I_{INRUSH} + I_{LOAD}$  的恒定电流。假设负载电流不受工作电压的影响:

$$P_{STEP} = \frac{V_{STEP} \cdot I_{MAX}}{2}$$

$$t_{STEP} = \frac{C_R \cdot V_{STEP}}{I_{RAMP(min)}} = \frac{C_L \cdot V_{STEP}}{I_{INRUSH}}$$

$$P\sqrt{t} = P_{STEP}\sqrt{t_{STEP}}$$

### LTM9100

# 应用信息

d. 传导时的负载短路功率耗散 (P<sub>SCON</sub>) 包括一个在持续时间为电路断路器周期的最大电流下的恒定总线电压。

$$t_{CB} = 620 \mu s$$

$P\sqrt{t} = P_{SCON} \sqrt{t_{CB}}$

经过检查,情形 d 将始终产生一个比情形 b 更低的数值,而且将不需要进行计算。

4. 选择 GATE 补偿电容  $(C_G)$ 。 GATE 引脚上的总电容应  $\approx$  47nF 以补偿有源电流限制电路。总电容等于:

$$C_{G(TOTAL)} = C_G + C_{iss} \approx 47 nF$$

- 5. 针对欠压和过压跳变点确定分压电阻器的大小,假设 UVL 和 UVH 引脚连接在一起,而且一个分压器用于这 两种功能(图 4)。可以通过把 UVL 和 UVH 连接至 V<sub>CC2</sub>、以及 OV 连接至 V<sub>EE</sub> 来停用这些功能。

- a. 选择一个流入分压器的标称电流  $(I_{DIV(NOM)})$ 。通常 它为  $100\mu A$ 。

- b. 过压情况下分压器中的电流为:

$$I_{DIV(OV)} = I_{DIV(NOM)} \bullet \frac{VBUS_{OV}}{VBUS_{NOM}}$$

式中的  $VBUS_{NOM}$  是标称总线电压,而  $VBUS_{OV}$  则为过压情况下的总线电压。

c. 计算 R1:

$$R_1 = \frac{V_{OV(TH)}}{I_{DIV(OV)}} = \frac{1.77V}{I_{DIV(OV)}}$$

d. 选择欠压总线电压 (VBUS<sub>UV</sub>)。欠压可以采用 2.56V 的上升门限 (UVH),即系统开始运作时的总线电压 来设定,或 2.291V 的下降门限(UVL),即系统停止 运作时的总线电压来设定,这取决于系统要求。

e. 在欠压过程门限的分压器电流为:

$$I_{DIV(UV)} = I_{DIV(NOM)} \bullet \frac{VBUS_{UV}}{VBUS_{NOM}}$$

f. 计算 R2:

$$R2 = \frac{V_{UV(TH)}}{I_{DIV(UV)}} - R1$$

g. 计算 R3:

$$R3 = \frac{VBUS_{NOM}}{I_{DIV(NOM)}} - R1 - R2$$

6. 确定连接至 DRAIN 引脚的电阻器大小,建议的偏置电流为 50μA,把数值限制为 <2mA。

$$R_D = \frac{VBUS_{NOM}}{50\mu A}$$

### 设计实例 #1

对于本设计实例,考虑具有  $C_L = 330 \mu F$  的 200W 应用,如图 4 所示。工作电压范围为 43V 至 71V,并具有一个 38.5V 的 UV 关断门限。为了计算的目的,最小工作电压为 36V,而最大值为 72V。本设计必须能耐受短路和一个 36V 的输入电压阶跃。

检测电阻器采用最小检测门限、最小工作电压和应用功率来计算:

$$R_S = \frac{45\text{mV} \cdot 36\text{V}}{200\text{W}} = 0.008\Omega$$

$$I_{MAX} = \frac{55 \text{mV}}{0.008} = 6.875 \text{A}$$

把浪涌电流设定为 0.66A。

$$C_R = C_L \cdot \frac{20\mu A}{0.66A} = 10nF$$

如前文讨论的那样,R<sub>R</sub> 的阻值选择为 1k。

3. 选择一个 MOSFET 并比较所有条件下的功率耗散计算值。选择的是 IRF1310,最坏情况传导损耗为:

$$P_{ON} = I_{MAX}^2 \bullet R_{DSON(125^{\circ}C)} = 6.875^2 \bullet 72 mΩ = 3.4 W$$

从产品手册 SOA 曲线可知,10ms 运作产生的  $P\sqrt{t} \approx 25 W\sqrt{s}$  ( $V_{DS} = 50V$ ,  $I_{D} = 5A$ )。

情形 3a:

$$P\sqrt{t} = \frac{72 \cdot 0.66}{2} \sqrt{\frac{330\mu \cdot 72}{0.66}} = 4.5W\sqrt{s}$$

情形 3b:

$$P_{fs} = \frac{72 \cdot 6.875}{2} = 248W, P_{CB} = 72 \cdot 6.875 = 495W$$

$$t_{fs} = \frac{(47n+1.9n) \cdot 2 \cdot 6.875}{7.5 \mu A \cdot 14} = 6.4 ms$$

$$P_{SCTON} = \frac{248 \cdot 6.4 \text{m} + 495 \cdot 620 \mu}{6.4 \text{m} + 620 \mu} = 270 \text{W}$$

$$P\sqrt{t} = 270\sqrt{6.4m + 620\mu} = 22.6W\sqrt{s}$$

情形 3c:

$$P\sqrt{t} = \frac{36 \cdot 6.875}{2} \sqrt{\frac{330\mu \cdot 36}{0.66}} = 16.6W\sqrt{s}$$

所有情况都满足  $P\sqrt{t}$  值 <  $25W\sqrt{s}$ 。

4. 在步骤 3 中选择的 FET 具有一个 1.9nF 的输入电容,因此 47nF 的  $C_G$  电容值是合适的。

5. 设定标称 UV/OV 分压器串至 100μA, 电阻器被取整至 最接近的 1% 精度阻值。

$$I_{DIV(OV)} = 100 \mu A \cdot \frac{72}{48} = 150 \mu A$$

$$I_{DIV(UV)} = 100 \mu A \cdot \frac{43}{48} = 89.6 \mu A$$

$$R1 = \frac{1.77}{150 \text{uA}} = 11.8 \text{k}\Omega$$

$$R2 = \frac{2.56}{89.6\mu A} - 11.8k\Omega = 16.9k\Omega$$

$$R3 = \frac{48}{100 \mu A} - 11.8 k\Omega - 16.9 k\Omega = 453 k\Omega$$

6. DRAIN 引脚电阻器被设定为  $1M\Omega$ 。

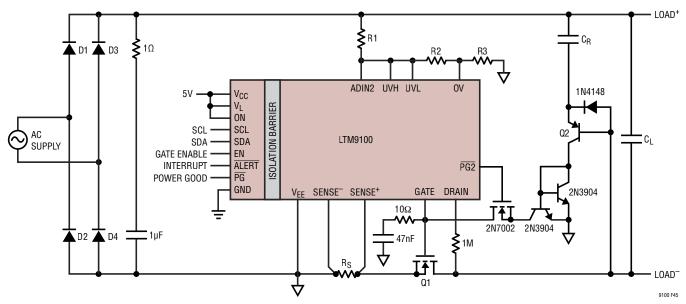

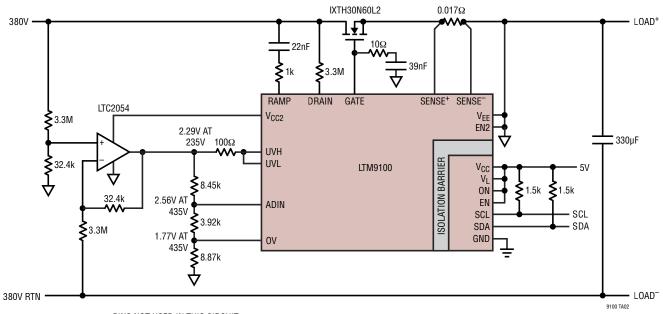

### 设计实例 #2

对于本设计实例,考虑具有  $C_L = 330 \mu F$  的 380 V 应用,如封底上所示。工作电压范围为 260 V 至 420 V,并具有一个 235 V 的 UV 关断门限和 435 V 的 UV 门限。本设计必须能耐受短路,且专为用一个现成有售的 MOSFET 实现可用负载电流的最大化而设计。

当最大工作电压为 435V 时,期望采用一个具有 600V 漏极 至源极电压的 MOSFET。为了最大限度地增加负载电流,需要最小的 R<sub>DSON</sub> 和卓越的 SOA。通过全面的器件考察我们发现 IXYS IXTH30N60L2 是一款上佳的可选产品。合理、可散热的电路板级传导损耗 (P<sub>ON</sub>) 为 5W。最大工作电流现可按下式计算:

$$I_{MAX} = \sqrt{\frac{P_{ON}}{R_{DSON(125^{\circ}C)}}} = \sqrt{\frac{5}{0.48}} = 3.25A$$

1. 计算检测电阻器:

$$R_S = \frac{55\text{mV}}{3.25\text{A}} = 0.017\Omega$$

2. 通过在 DC SOA 工作曲线的下面选择一个工作电流 (在 400V),以设定浪涌电流。

$$I_{INRUSH} = 0.3A, C_R = 330\mu \cdot \frac{20\mu A}{0.3A} = 22nF$$

3. 器件的 P√t 在外壳温度为 75°C 时 ≈ 80W√s

情形 3a:

$$P\sqrt{t} = \frac{430 \cdot 0.3}{2} \sqrt{\frac{330\mu \cdot 430}{0.3}} = 44W\sqrt{s}$$

情形 3b:

$$P_{fs} = \frac{430 \cdot 3.25}{2} = 700W, P_{CB} = 430 \cdot 3.25 = 1.4kW$$

$$t_{fs} = \frac{(39n+10.7n) \cdot 2 \cdot 3.25}{7.5uA \cdot 10} = 4.3ms$$

$$P_{SCTON} = \frac{700 \cdot 4.3m + 1400 \cdot 620\mu}{4.3m + 620\mu} = 788W$$

$$P\sqrt{t} = 788\sqrt{4.3m + 620\mu} = 55W\sqrt{s}$$

情形 3c 未计算,因为没有明确规定一个输入阶跃。

- 4. 所选的 FET 具有 10.7nF 的输入电容,因此 39nF 的  $C_G$  电容值是合适的。

- 5. 在本例中,总线电压必须进行电平移位并参考于 V<sub>EE</sub> 以使用 UV、OV 和模拟输入。这是由采用 LTC<sup>®</sup>2054 的差分放大级完成的。由于该放大器的输出连接至 UV 引脚,因此放大器分压比是针对一个 2.291V 输出电压 (在235V 的 UV 关断门限) 设定的;235/2.291=102.3。选择适当的输入电阻器以最大限度地减少电流和功率耗

散;选择的阻值为 3.3 M  $\Omega$ ,分压电阻器于是为 3.3 M  $\Omega$ /102.3 = 32.4 k  $\Omega$ 。如在原理图上注释的那样, ADIN 引脚电压应为 2.56 V (在 435 V),而 OV 电压应为 1.77 V (在 435 V)。把最大分压器串电流设定为 200 μ A。

$$R1 = \frac{1.77}{200\mu A} = 8.87k\Omega$$

$$R2 = \frac{2.56}{200\mu A} - 8.87k\Omega = 3.92k\Omega$$

$$R3 = \frac{\frac{VBUS_{OV}}{102.3}}{200\mu A} - 8.87k\Omega - 3.92k\Omega = 8.45k\Omega$$

6. DRAIN 引脚电阻器被设定为  $3.3M\Omega$ 。

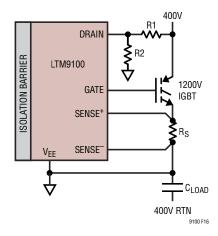

### 外部开关

虽然 LTM 9100 的主要应用是控制一个外部 N 沟道 MOSFET,但是可以采用隔离栅双极型晶体管 (IGBT)。在不可使用具有足够 SOA 和低  $R_{DSON}$  的传统 FET 的 > 250V 电压应用中,这一点特别让人感兴趣。

具有 600V、1200V 和更高电压额定值的 IGBT 是很容易获得。并非所有的 IGBT 都合适,只有那些指定用于如产品手册 SOA 工作曲线中标示的 DC 或接近 DC 操作的 IGBT 方可。两个额外的关注事项是集电极至发射极饱和电压和栅极至发射极门限电压。

LTM9100 通过 DRAIN 引脚和检串联电阻器监视 IGBT 的集电极电压,以确保 IGBT 在电源良好信号被转换之前接通。DRAIN 引脚门限为 1.77V。IBGT 的饱和电压 V<sub>CE(SAT)</sub> 可能比此更高,因而有必要在 DRAIN 监视器输入引脚上布设一个分压器,如图 16 所示。

电阻器 R1 的大小根据总线电压和 2mA 的最大 DRAIN 电流来确定。接着选择电阻器 R2 的阻值以在 DRAIN 引脚上

图 16:用于 IGBT 集电极检测的 LTM9100 DRAIN 监视器阻性分压器

提供一个低于 1.77V 的电压,并留有针对最坏情况负载电流和最小 GATE 电压下 IBGT 之  $V_{CE}$  电压的裕量。

IGBT 栅极至发射极门限电压也是必须考虑的。所选 IGBT 的最大栅极至发射极门限电压  $V_{GE(th)}$  应对应于最小LTM9100 GATE 电源良好条件或 8.5V 的  $V_S$  最小 UVLO 电压。器件产品手册电特性表中给出的门限电压经常是在非常低集电极电流下的数值。通常提供了「集电极电流与栅极-发射极电压的关系曲线」图和「栅极-发射极电压与栅极电荷的关系曲线」图。必须谨慎地评估 IGBT 的特性以确保与LTM9100 的兼容性。

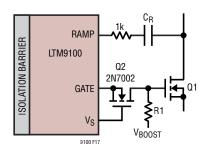

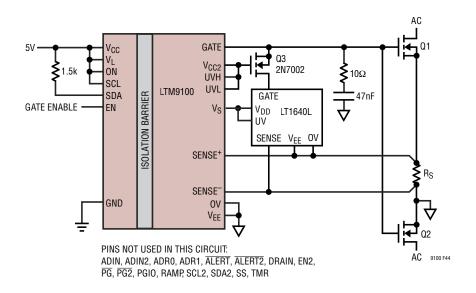

### 提升栅极电压

出于两个主要原因也许需要提供较高的栅极电压。首先,为了降低通过米勒电容从漏极或集电极至栅极的 dV/dt 耦合的敏感性,提供额外的噪声裕量。其次,旨在优化  $R_{DSON}$  或  $V_{CE}$ ,进而降低功率耗散。

图 17 示出了一种增加栅极电压的简单方法。Q2 保持导通状态,直到相对于  $V_S$  的 LTM9100 GATE 电压达到 Q2 的  $V_{GS}$  门限为止。当 Q2 关断时,Q1 的栅极继续通过连接至一个外部电源电压 ( $V_{BOOST}$ ) 的 R1 进行充电。R1 阻值的选择应确保 Q1 栅极在  $\overline{PG2}$  转换之前、LTM9100 GATE 引

脚达到  $\sim 9V$  一个定时器延迟之后接近全电压。另外,R1 的阻值还影响 Q1 的栅极充电电流。在负载电流浪涌计算和  $C_B$  大小确定的过程中必须考虑这个额外的电流。

图 17:简单的栅极电压升压器

$$\begin{split} I_{RAMP} &\approx 20 \mu A + 2 \bullet \frac{V_{B00ST} - V_{Q1(threshold)}}{R1} \\ C_{R} &= C_{L} \bullet \frac{I_{RAMP}}{I_{INRUSH}} \end{split}$$

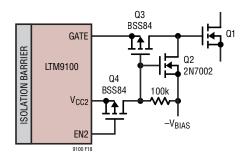

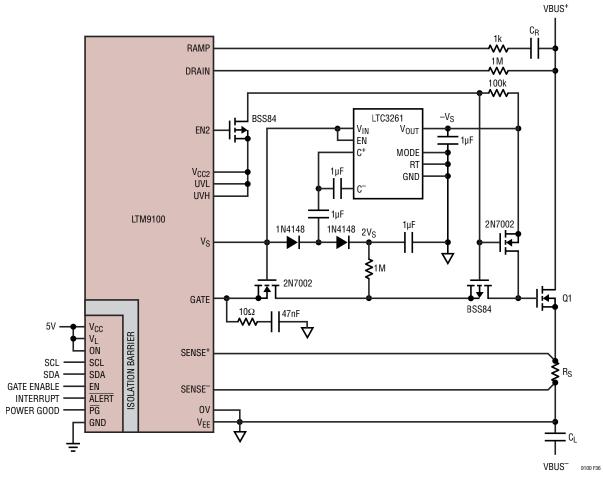

### 负栅极偏置

虽然 GATE 在关断状态中被强烈地拉至  $V_{EE}$ ,但是可能仍然期望拥有额外的电压裕量以进一步降低发生电容耦合开关接通的风险。在该场合中,还可以纳入一个负栅极关断偏置,如图 18 所示。Q4 在 EN 转换至低电平时使能负偏置,Q3 阻断从基于  $V_{EE}$  的 GATE 引脚流出的电流,而 Q2 把一个外部负电压  $(-V_{BIAS})$  连接至开关。

图 18:由 EN 控制的负栅极偏置

图 36 的应用电路显示了一种用于从  $V_S$  产生升压电源和负偏置电源的方法。

### 并联开关

建议不要采用并联连接开关的方式来扩大接通期间的 SOA。LTM9100 未纳入任何旨在确保多个开关之间均流的 保障。开关接通特性的差异将不可避免地导致一个开关传导 大部分的接通电流,直至得到全面平衡为止。

这一点也适用于由多颗芯片组成以实现较高电流额定值的 FET 模块。这种模块未采用任何动态均流方法。开关门限匹配并不足以保证均流。

### 具有 AC 纹波 (整流 AC) 的 DC 总线

LTM9100 主要用于通过使一个外部 FET 的漏极电压线性地渐变 (这产生一个恒定的充电电流) 来控制一个电容器的充电。如果 DC 总线电压包含一个 AC 分量,则电容器仅在整流输入电压超过电容器电压时充电,因而产生短间隔的高峰值电流。

通常增设一个串联电感器以抑制 AC 纹波并使电容器充电电流平稳。必须根据电源阻抗、负载要求等谨慎地设计输入 LC 滤波器,而有关它的设计不在本讨论的范围内。

如果不希望使用一个电感性输入滤波器,而且负载要求使得初始接通之后的峰值电容器充电电流处于可容许的水平,则LTM9100 可配置为给负载电容充电,见图 19。由于 AC 电压耦合到 GATE 上,因此未采用 RAMP 引脚,取而代之的是增设晶体管 Q2,并以串联方式布设斜坡电容器,以在负载电容充电时控制 GATE。二极管 D5 使斜坡电容器在器件关断时复位,而晶体管 Q3 则在接通序列结束之后隔离GATE,以防止在正常操作期间执行进一步的 GATE 调制。

检测电阻器的大小是针对正常操作期间的峰值电容器充电电流确定的,以避免占用内部电流限制和电路断路器功能,否则有可能导致过多的功率耗散和 FET 损毁。在 FET 两端具有高达全输入总线电压的浪涌充电周期中尤其如此。

530μs 的内部电路断路器时间导致了接通期间的过多功率 耗散和短路情况。如果需要提供接通期间的短路保护,则必

图 19:整流 AC 高压侧充电电路

| 表 1: | 针对 13.4%   | 6 纹波 (单相 | 1和3.4% 纹波           | (三相) 的组件值 |

|------|------------|----------|---------------------|-----------|

| ~ ·  | 11 AJ 10.7 |          | / 'I'' U.T /U ///// | \_        |

| V <sub>AC</sub> | Q1         |      |                         | C <sub>G</sub> | I <sub>LOAD</sub> | CL     | C <sub>R</sub> | R <sub>S</sub> |            |

|-----------------|------------|------|-------------------------|----------------|-------------------|--------|----------------|----------------|------------|

|                 | 器件型号       | 电压   | R <sub>DSON(25°C)</sub> |                |                   |        |                | 1φ             | <b>3</b> ¢ |

| 48              | FQA90N15   | 150V | 0.018                   | 39nF           | 8                 | 5600µF | 56nF           | 0.0008         | 0.0016     |

| 120             | FQA55N25   | 250V | 0.04                    | 47nF           | 6                 | 1500µF | 39nF           | 0.001          | 0.002      |

| 240             | FDL100N50F | 500V | 0.055                   | 33nF           | 5                 | 680µF  | 6.8nF          | 0.001          | 0.002      |

需采用一个外部电子电路断路器,即图 19 中的LTC4213。

负载充电电流  $(I_{INRUSH})$  的选择基于  $FET\ SOA$ 。斜坡电容器  $(C_R)$  和斜坡时间  $(t_{INRUSH})$  的计算和前面一样,只是采用 GATE 电流取代了 RAMP 电流:

$$\begin{split} &C_R = C_L \bullet \frac{I_{GATE}}{I_{INRUSH}} = C_L \bullet \frac{11.5 \mu A}{I_{INRUSH}} \\ &t_{INRUSH} = C_R \bullet \frac{V_{PEAK}}{I_{GATE}} = C_L \bullet \frac{V_{PEAK}}{I_{INRUSH}} \end{split}$$

也许需要延长充电时间以减小接通期间的瞬态温度摆幅。诸如 LTspice® 等电路仿真软件可用于预知最大结温,假如可使用一种准确的 FET 瞬态热阻抗模型的话。表 1 列出了针

对三种不同输入电压电平下的单相和三相电压输入的组件值。在图 20 中,针对表 1 中 120V<sub>AC</sub> 的情形示出了负载充电电压、电流和 Q1 的结温。

为表 1 中的实例而指定的检测电阻器基于一个 0Ω 的电源阻抗,因此代表的是最小值,实际上峰值电容器充电电流将较低,应该适当地确定检测电阻器的大小。此外,还必须选择合适的负载电容器以处理高的 RMS 充电电流,而由于这个原因负载电容器通常将由多个并联电容器构成。

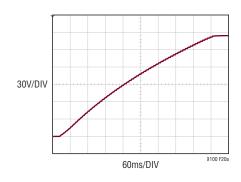

图 20(a): 负载电容器电压

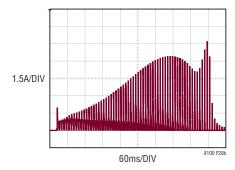

图 20(b):负载电容器电流

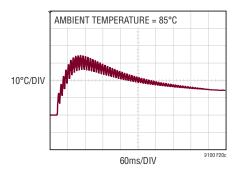

图 20(c): Q1 的结温

图 20:负载电容器充电电压、电流和 Q1 的结温

图 21: I<sup>2</sup>C 时序图

### 芯片间通信总线 (I<sup>2</sup>C)

LTM9100 提供了一个可兼容  $I^2C$  的隔离型接口;时钟线 (SCL $\rightarrow$ SCL2) 是单向的,支持仅限主控器的模式,而数据线 (SDA $\longleftrightarrow$ SDA2) 则是双向的。 $I^2C$  接口提供对 ADC 数据存储器和其他 4 个用于 FET 监视和控制之寄存器的访问。此外,隔离侧  $I^2C$  引脚也是可访问的,因而可提供额外的串行设备扩展。

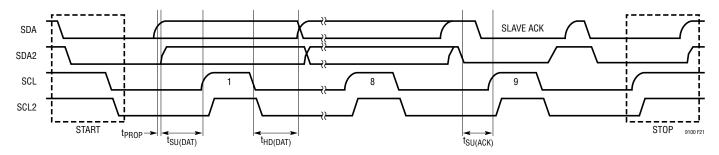

最大  $I^2C$  数据速率为 400kHz,能支持快速模式,受限于从属确认建立时间  $(t_{SU(ACK)})$ ,该时间由系统传播延迟、毛刺干扰滤波器、和大约 500ns 的固定隔离数据延迟所组成。时序详见图 21。总的建立时间把  $I^2C$  数据保持时间  $(t_{HD(DAT)})$  减小至 175ns 的最大值,从而保证充足的数据建立时间  $(t_{SU(DAT)})$ 。

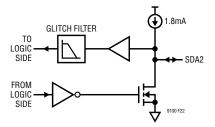

隔离侧双向串行数据引脚 SDA2 的简化原理图示于图 22。 一个内部 1.8mA 电流源为 SDA2 提供一个上拉电流。不要 把任何其他上拉器件连接至 SDA2。该电流源足以满足针对 大于 200pF (在快速模式中) 和大于 400pF (在标准模式中) 之总线电容的系统要求。

另外的专有电路负责监视 SDA 和 SDA2 信号上的转换速率,以管理横跨绝缘隔离的方向控制。两个引脚上的转换速率必须大于 1V/µs 以执行正确的操作。

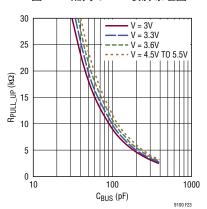

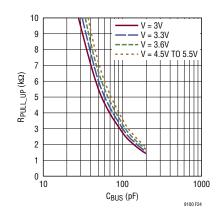

逻辑侧双向串行数据引脚 SDA 需要一个连接至 V<sub>L</sub> 的上拉电阻器或电流源。遵循图 23 和 24 中的要求,在 SDA 上布设适合的上拉电阻器以满足期望的上升时间规格以及针对快

图 22:隔离 SDA2 引脚原理图

图 23: SDA 上的最大标准速度模式上拉电阻

图 24: SDA 上的最大快速模式上拉电阻

速 (FAST) 和标准 (STANDARD) 模式的 V<sub>OL</sub> 最大限值。 电 阻曲线代表最大电阻边界;可以使用位于合适曲线左侧的任 何数值。

隔离侧时钟引脚 SCL2 具有一个弱推挽式输出驱动器;不要 连接一个外部上拉器件。SCL2 无需时钟拉伸即可兼容 I<sup>2</sup>C 设备。在轻负载接线上,可使用一个布设在 SCL2 和 Ver 之间的 100pF 电容器或 RC 低通滤波器 (R =  $500\Omega$ , C = 100pF) 来增加上升和下降时间并最大限度地降低噪声。

LTM9100 是一款读写型从器件,并且支持 SMBus 读类 型、写类型、读字 (word) 和写字命令。一个读字命令中的 第二个字和第一个字将是完全相同的。一个写字命令中的第 二个字是被忽略的。这些命令的数据格式示于图 25 至 28。

#### START 和 STOP 条件

当总线空闲时, SCL 和 SDA 均必须为高电平。一个总线主 控器通过在 SCL 为高电平的情况下把 SDA 从高电平转换至 低电平来表示一个传输的开始和一个 START 条件。当主控 器完成了与受控器的通信时,它通过在 SCL 为高电平的情 况下把 SDA 从低电平转换至高电平发布一个 STOP 条件。 总线随后空闲出来以执行另一项传输。

#### 阻塞总线复位

LTM9100 I<sup>2</sup>C 接口具有一个阻塞总线复位定时器。对 SCL2 和 SDA2 引脚的低电平条件进行「或」逻辑运算以起 动定时器。当 SCL2 和 SDA2 均被拉至高电平时,定时器

| S                                    | ADDRESS     | W | Α | COMMAND                   | Α         | DATA                                   | Α               | P |  |  |  |

|--------------------------------------|-------------|---|---|---------------------------|-----------|----------------------------------------|-----------------|---|--|--|--|

|                                      | 001a3:a0    | 0 | 0 | XXXXb3:b0                 | 0         | b7:b0                                  | 0               |   |  |  |  |

| 9100 F25                             |             |   |   |                           |           |                                        |                 |   |  |  |  |

|                                      | M MASTER TO |   |   | A: NOT<br>R: REA<br>W: WR | AC<br>D B | WLEDGE<br>KNOWL<br>IT (HIGI<br>BIT (LO | EĎŒ<br>H)<br>W) |   |  |  |  |

| S: START CONDITION P: STOP CONDITION |             |   |   |                           |           |                                        |                 |   |  |  |  |

|   | S | ADDRESS  | W | Α | COMMAND   | A | DATA  | Α | DATA     | A | Р     |

|---|---|----------|---|---|-----------|---|-------|---|----------|---|-------|

|   |   | 001a3:a0 | 0 | 0 | XXXXb3:b0 | 0 | b7:b0 | 0 | XXXXXXXX | 0 |       |

| _ |   |          |   |   |           |   |       |   |          |   | 00.50 |

图 26:LTM9100 串行总线 SDA 写字 (word) 协议

图 25: LTM9100 串行总线 SDA 写字节 (Byte) 类型协议

| S | ADDRESS  | W | A | COMMAND   | A | S | ADDRESS  | R | A | DATA  | A | Р |

|---|----------|---|---|-----------|---|---|----------|---|---|-------|---|---|

|   | 001a3:a0 | 0 | 0 | XXXXb3:b0 | 0 |   | 001a3:a0 | 1 | 0 | b7:b0 | 1 |   |

图 27:LTM9100 串行总线 SDA 读字节类型协议

| S | ADDRESS  | W | A | COMMAND   | Α | S | ADDRESS  | R | Α | DATA  | A | DATA  | Α | Р |

|---|----------|---|---|-----------|---|---|----------|---|---|-------|---|-------|---|---|

|   | 001a3:a0 | 0 | 0 | XXXXb3:b0 | 0 |   | 001a3:a0 | 1 | 0 | b7:b0 | 0 | b7:b0 | 1 |   |

图 28:LTM9100 串行总线 SDA 读字协议

复位。如果 SCL2 引脚或 SDA2 引脚保持低电平的时间超过 66ms,则阻塞总线定时器将期满,且内部 I<sup>2</sup>C 状态机将被复位以在总线阻塞于低电平的情况被清除之后提供正常的通信。 当 SCL2 引脚和 SDA2 引脚被交替地保持在低电平时,如果在定时器复位情况 (SCL2 和 SDA2 均为高电平)出现之前 SCL2 和 SDA2 的「或」低电平周期超过66ms,则阻塞总线定时器将期满且 I<sup>2</sup>C 状态机复位。

#### I<sup>2</sup>C 设备寻址